可以调节时钟数据恢复CDR锁定点的装置的制作方法

本发明涉及集成电路设计,尤其涉及高速串行接口芯片物理层电路设计中的时钟数据恢复(cdr)技术。

背景技术:

1、时钟数据恢复(cdr)是串行通信系统中的关键组成部分,用于在接收端通过接收数据恢复发送端时钟,从而实现正确的数据采样。在高速数据传输过程中,由于信号传输路径的延迟、失真和噪声等因素,接收端的时钟信号可能与发送端的时钟信号存在相位差异,导致采样误差。为了解决这个问题,cdr 电路被引入到串行通信系统中,以便于在接收端准确地恢复发送端的时钟信号并实现精确的数据采样。

2、cdr 通常采用两种不同的算法:mueller-muller(mm)算法和bang-bang(bb)算法。两者在采样方式和性能上有所不同。

3、mueller-muller(mm)算法:mm 算法采用单倍采样方式,即接收端的时钟信号和数据信号采样率相同。mm 算法通过对输入数据信号的零交叉点进行检测和分析,估计发送端时钟信号的相位,并根据相位差异调整接收端时钟信号。

4、bang-bang(bb)算法:bb 算法采用双倍过采样方式,即接收端的时钟信号采样率是数据信号采样率的两倍。bb 算法在每个单位间隔(ui)的中心和边缘点进行数据采样,并根据采样结果调整接收端时钟信号。

5、然而,尽管 mm 和 bb 算法在某些方面有所优势,但它们仍然存在一定的局限性,无法确保恢复时钟正好采在数据最佳点上。因此,需要更先进的 cdr技术,以便在高速数据通信中实现更高的锁定精度和更低的误码率。

技术实现思路

1、本申请的目的在于提供一种可以调节时钟数据恢复cdr锁定点的装置,以解决上述背景技术中提出的问题。

2、本申请公开了一种可以调节时钟数据恢复cdr锁定点的装置,包括:

3、相位插值器,用于对接收到的数据进行采样,并根据pi码字累加器反馈的新的相位控制码字动态调整输出时钟信号的相位;

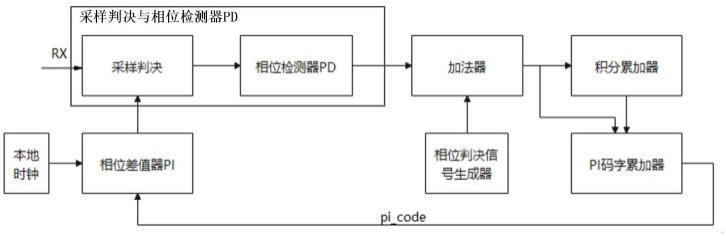

4、采样判决与相位检测器模块,所述采样判决与相位检测器模块包含采样判决以及相位检测器模块,其中,所述采样判决与所述相位插值器的输出端连接,所述相位检测器与采样判决的输出端连接,所述采样判决与相位检测器模块用于对相位插值器输出的时钟进行相位判决,产生表示时钟相位偏移方向的早晚信号;

5、相位判决偏置信号生成器,用于产生不同方向和大小的时钟相位偏置;

6、加法器,分别与所述相位检测器的输出端和所述相位判决偏置信号生成器的输出端连接,用于接收时钟早晚信号,并与时钟相位偏置相加,产生表示时钟相位调整量的控制信号;

7、积分累加器,与所述加法器的输出端连接,用于对控制信号进行累加,产生相位控制码字,以动态调整本地时钟的相位;

8、pi码字累加器,与所述加法器的输出端以及积分累加器的输出端连接,用于将控制信号与当前的相位控制码字进行累加,生成新的相位控制码字,并反馈给所述相位插值器,以调整时钟相位使其锁定在最佳采样点。

9、在一个优选例中,所述相位插值器采用线性相位插值器。

10、在一个优选例中,所述相位检测器采用亚采样时钟的相位检测技术。

11、在一个优选例中,所述相位判决偏置信号生成器输出的时钟相位偏置为周期性脉冲信号。

12、在一个优选例中,所述积分累加器采用数字积分器实现。

13、在一个优选例中,所述pi码字累加器采用数字pi调节码累加器实现。

14、在一个优选例中,所述相位检测器使用锯齿波方法,或互相关法,或混频法来实现。

15、在一个优选例中,所述相位判决偏置信号生成器周期性地向相位判决结果中添加early或late偏置信号。

16、本申请实施方式中,相位判决偏置信号生成器用于产生不同方向和大小的时钟相位偏置;加法器用于接收时钟早晚信号,并与时钟相位偏置相加,产生表示时钟相位调整量的控制信号;pi码字累加器用于将控制信号与当前的相位控制码字进行累加,生成新的相位控制码字,并反馈给所述相位插值器,以调整时钟相位使其锁定在最佳采样点,由此,通过各个组件的协同工作,实现了时钟相位的动态调整、降低误码率、提高锁定精度等技术效果。这使得该电路在数据通信、存储和其他高速传输领域具有广泛的应用潜力。

17、本申请的说明书中记载了大量的技术特征,分布在各个技术方案中,如果要罗列出本申请所有可能的技术特征的组合(即技术方案)的话,会使得说明书过于冗长。为了避免这个问题,本申请上述

技术实现要素:

中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均因视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a+b+c,在另一个例子中公开了特征a+b+d+e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a+b+c+d的方案因技术不可行而应当不被视为已经记载,而a+b+c+e的方案应当视为已经被记载。

技术特征:

1.一种可以调节时钟数据恢复cdr锁定点的装置,其特征在于,包括:

2.如权利要求1所述的装置,其特征在于,所述相位插值器采用线性相位插值器。

3.如权利要求1所述的装置,其特征在于,所述相位检测器采用亚采样时钟的相位检测技术。

4.如权利要求1所述的装置,其特征在于,所述相位判决偏置信号生成器输出的时钟相位偏置为周期性脉冲信号。

5.如权利要求1所述的装置,其特征在于,所述积分累加器采用数字积分器实现。

6.如权利要求1所述的装置,其特征在于,所述pi码字累加器采用数字pi调节码累加器实现。

7.如权利要求1所述的装置,其特征在于,所述相位检测器使用锯齿波方法,或互相关法,或混频法来实现。

8.如权利要求1所述的装置,其特征在于,所述相位判决偏置信号生成器周期性地向相位判决结果中添加early或late偏置信号。

技术总结

本申请涉及集成电路技术,公开了一种可以调节时钟数据恢复CDR锁定点的装置,包括:相位插值器、相位检测器、加法器、相位判决偏置信号生成器、积分累加器和PI码字累加器,其中,相位判决偏置信号生成器用于产生不同方向和大小的时钟相位偏置;加法器用于接收时钟早晚信号,并与时钟相位偏置相加,产生表示时钟相位调整量的控制信号;PI码字累加器用于将控制信号与当前的相位控制码字进行累加,生成新的相位控制码字,并反馈给所述相位插值器,以调整时钟相位使其锁定在最佳采样点。本申请能够在高速数据通信中实现更高的锁定精度和更低的误码率。

技术研发人员:葛云龙,王浩南,冯飞

受保护的技术使用者:上海钫铖微电子有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!