一种异质结自整流忆阻器、集成电路及制备方法

本发明属于微电子,具体涉及一种异质结自整流忆阻器、集成电路其制备方法。

背景技术:

1、人工智能作为引领未来的前沿性、战略性技术,是第四次科技革命的核心驱动力,也是催生新就业的有力武器。忆阻器在人工智能类脑神经计算领域中发挥着重要的作用,应用较广泛,具有高集成密度、低功耗、低工艺复杂度和多值计算潜力等方面的优势。

2、忆阻器集成电路往往采用交叉阵列结构,该阵列潜在的漏电流主要来自忆阻单元周围未被选中的单元。而漏电流的存在会导致最终得到的读出电流大于选中单元的实际读出电流。漏电流问题不仅会降低读取裕度,而且会导致阵列功耗增加,因此需解决这一漏电流问题。

3、现有技术中,一种做法是将忆阻器串联一个有源的晶体管构成1t1r单元,或用忆阻器和选择器串联构成1s1r单元,或用忆阻器和一个二极管串联构成1d1r单元实现整流的功效,来解决漏电流问题。但是,这种做法由于需要将忆阻器与一个器件串联,不可避免会严重限制器件的集成度,对器件性能和小型化集成应用形成干扰,还会使得工艺更加复杂。

4、现有技术中还有一种做法是通过提升忆阻器自身的整流性能来减轻上述漏电流问题。例如,公开号为cn113206194a的专利申请公开一种自整流忆阻器,该专利申请通过在氧化物阻变层中进行金属掺杂,使得金属以金属离子状态融入氧化层,改变器件的能带结构,从而提升忆阻器的整流性能,但该自整流忆阻器对于漏电流问题的减轻效果还不够好。

技术实现思路

1、为了解决现有技术中所存在的上述问题,本发明提供了一种异质结自整流忆阻器、集成电路其制备方法。

2、本发明要解决的技术问题通过以下技术方案实现:

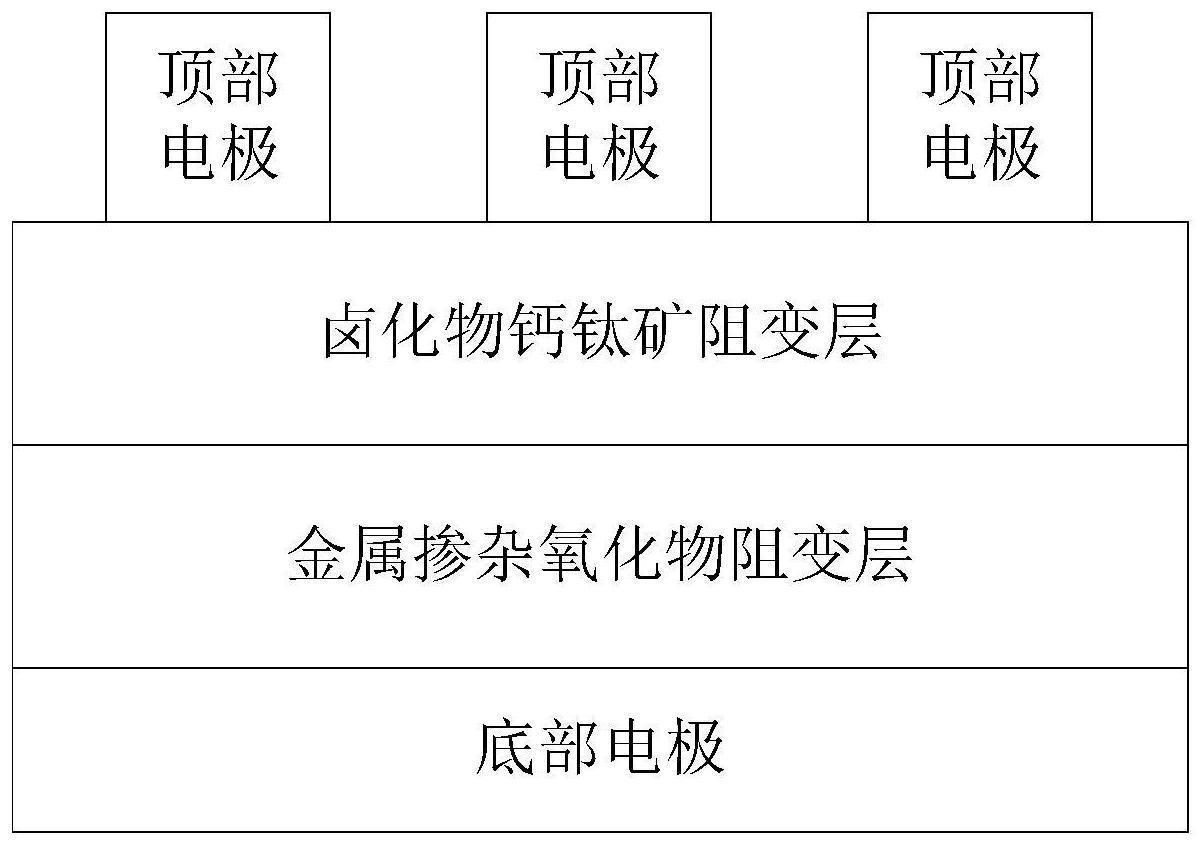

3、一种异质结自整流忆阻器,包括:

4、底部电极;

5、金属掺杂氧化物阻变层,制备在所述底部电极之上;

6、卤化物钙钛矿阻变层,制备在所述金属掺杂氧化物阻变层之上;

7、顶部电极,制备在所述卤化物钙钛矿阻变层之上;

8、其中,所述金属掺杂氧化物阻变层和所述卤化物钙钛矿阻变层形成忆阻器的异质结阻变层。

9、优选地,所述金属掺杂氧化物阻变层,包括:cu:tiox阻变层。

10、优选地,所述卤化物钙钛矿阻变层,包括:abx3型钙钛矿阻变层;

11、其中,a为ma、fa及cs中的一种或多种的组合,b为pb或sn,x为cl、i及br中的一种或多种的组合。

12、优选地,所述顶部电极包括多个。

13、本发明还提供了一种异质结自整流忆阻器集成电路,包括多个如上所述的异质结自整流忆阻器。

14、本发明还提供了一种异质结自整流忆阻器制备方法,包括:

15、在衬底上制备底部电极;

16、在所述底部电极之上制备金属掺杂氧化物阻变层;

17、在所述金属掺杂氧化物阻变层之上制备卤化物钙钛矿阻变层;

18、在所述卤化物钙钛矿阻变层之上制备顶部电极,得到制备完成的异质结自整流忆阻器;

19、其中,所述金属掺杂氧化物阻变层和所述卤化物钙钛矿阻变层形成忆阻器的异质结阻变层。

20、优选地,在所述底部电极之上制备金属掺杂氧化物阻变层,包括:

21、采用磁控共溅射工艺在所述底部电极之上沉积金属掺杂氧化物阻变层。

22、优选地,所述金属掺杂氧化物阻变层,包括:cu:tiox阻变层。

23、优选地,在所述金属掺杂氧化物阻变层之上制备卤化物钙钛矿阻变层,包括:

24、采用热动态旋涂法于所述金属掺杂氧化物阻变层上涂覆卤化物钙钛矿阻变层。

25、优选地,所述卤化物钙钛矿阻变层,包括:abx3型钙钛矿阻变层;

26、其中,a为ma、fa及cs中的一种或多种的组合,b为pb或sn,x为cl、i及br中的一种或多种的组合。

27、本发明提供的异质结自整流忆阻器中,金属掺杂氧化物阻变层和卤化物钙钛矿阻变层结合形成异质结,由此可利用异质结界面肖特基势垒调制效应提升器件的整流特性;在此基础上,可以通过增加光照使得钙钛矿层产生额外的光生载流子,从而实现对器件自整流特性的进一步调控。

28、并且,金属掺杂氧化物阻变层中的金属是充分均匀地掺杂在氧化钛的内部而不是表面,即该金属掺杂氧化物阻变层为一个整体层而非分别作用的两层,因此该金属掺杂氧化物阻变层分别与底部电极、顶部电极的接触势垒得到了改善,进一步提高了自整流忆阻器的自整流能力。

29、综上,本发明提供的自整流忆阻器,器件结构简单、性能良好且稳定。基于该自整流忆阻器,可降低构建交叉阵列配置的复杂度,便于通过crossbar结构来构建高密度的忆阻阵列,从而有利于硬件实现大规模阵列的忆阻人工神经网络,具有十分巨大的应用潜力。

30、以下将结合附图及对本发明做进一步详细说明。

技术特征:

1.一种异质结自整流忆阻器,其特征在于,包括:

2.根据权利要求1所述的异质结自整流忆阻器,其特征在于,所述金属掺杂氧化物阻变层,包括:cu:tiox阻变层。

3.根据权利要求1所述的异质结自整流忆阻器,其特征在于,所述卤化物钙钛矿阻变层,包括:abx3型钙钛矿阻变层;

4.根据权利要求1所述的异质结自整流忆阻器,其特征在于,所述顶部电极包括多个。

5.一种异质结自整流忆阻器集成电路,其特征在于,包括多个如权利要求1~4任一项所述的异质结自整流忆阻器。

6.一种异质结自整流忆阻器制备方法,其特征在于,包括:

7.根据权利要求6所述的异质结自整流忆阻器制备方法,其特征在于,在所述底部电极之上制备金属掺杂氧化物阻变层,包括:

8.根据权利要求6或7所述的异质结自整流忆阻器制备方法,其特征在于,所述金属掺杂氧化物阻变层,包括:cu:tiox阻变层。

9.根据权利要求6所述的异质结自整流忆阻器制备方法,其特征在于,在所述金属掺杂氧化物阻变层之上制备卤化物钙钛矿阻变层,包括:

10.根据权利要求6或9所述的异质结自整流忆阻器制备方法,其特征在于,所述卤化物钙钛矿阻变层,包括:abx3型钙钛矿阻变层;

技术总结

本发明公开了一种异质结自整流忆阻器,包括:底部电极;金属掺杂氧化物阻变层,制备在所述底部电极之上;卤化物钙钛矿阻变层,制备在所述金属掺杂氧化物阻变层之上;顶部电极,制备在所述卤化物钙钛矿阻变层之上;其中,所述金属掺杂氧化物阻变层和所述卤化物钙钛矿阻变层形成忆阻器的异质结阻变层。

技术研发人员:汪钰成,段唯钦,王少熙,李伟,吴玉潘

受保护的技术使用者:西北工业大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!