包括不同导电线的半导体装置的制作方法

示例实施例涉及一种包括不同导电线的半导体装置及其制造方法。

背景技术:

1、已经进行了减小半导体装置中包括的元件的尺寸并改善其性能的研究。随着半导体装置中包括的元件的尺寸的减小,由位线之间的寄生电容引起的rc延迟已经作为相对于具有减小尺寸的位线的大问题而出现。

技术实现思路

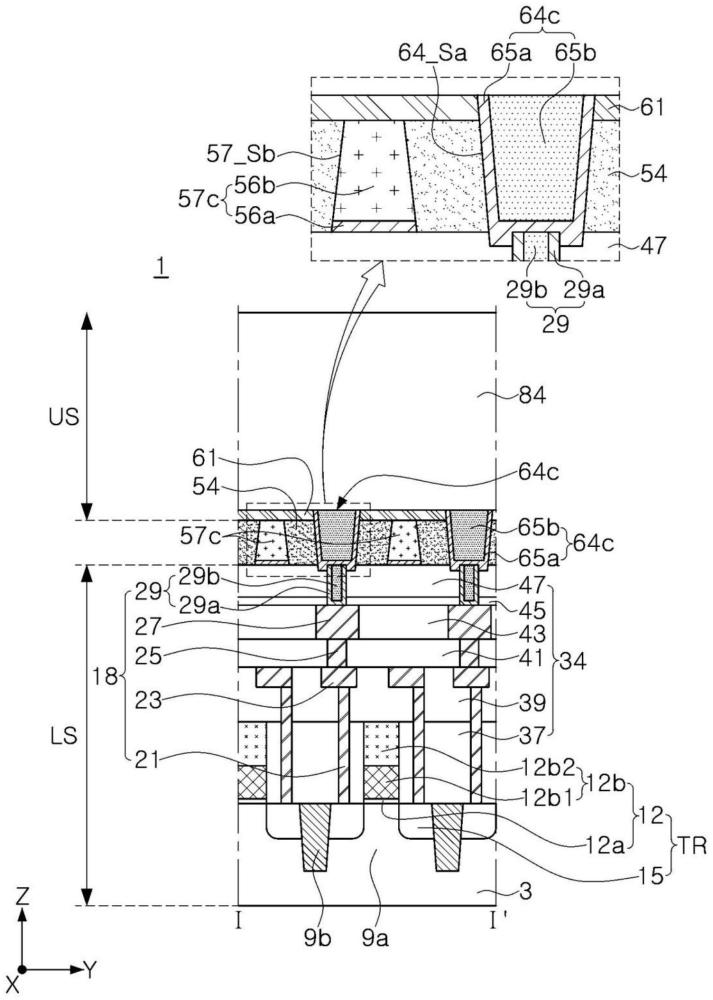

1、实施例涉及一种半导体装置,包括下结构、下结构上的层间绝缘层、下结构上的导电屏蔽线、层间绝缘层和导电屏蔽线上的封盖绝缘层、以及下结构上的位线,导电屏蔽线穿透层间绝缘层,位线穿透封盖绝缘层和层间绝缘层,其中,位线的上表面位于比导电屏蔽线的上表面高的水平高度处,并且位线的下表面位于等于或低于导电屏蔽线的下表面的水平高度处。

2、实施例还包括一种半导体装置,包括下结构、下结构上的第一导电线、以及在下结构上并与第一导电线间隔开的第二导电线,其中,第二导电线的上表面位于比第一导电线的上表面高的水平高度处,第二导电线的下表面位于与第一导电线的下表面相同或更低的水平高度处,并且第二导电线的侧表面的斜率不同于第一导电线的侧表面的斜率。

3、实施例还包括一种半导体装置,该半导体装置包括:衬底;衬底上的电路装置;衬底上的布线结构,该布线结构电连接到电路装置;位线,其分别在第一水平方向上延伸,并且位于比布线结构的水平高度高的水平高度处;导电屏蔽线,其与位线在垂直于第一水平方向的第二水平方向上交替布置;以及字线,其分别在第二水平方向上延伸,其中,字线位于比位线和导电屏蔽线高的水平高度处,并且位线的上表面位于比导电屏蔽线的上表面高的水平高度,并且位线中的每一条具有负斜率。

技术特征:

1.一种半导体装置,包括:

2.如权利要求1所述的半导体装置,其中,所述位线包括导电图案以及覆盖所述导电图案的侧表面和下表面的阻挡层。

3.如权利要求1所述的半导体装置,其中,所述位线的侧表面的斜率不同于所述导电屏蔽线的侧表面的斜率。

4.如权利要求3所述的半导体装置,其中,所述位线的侧表面具有负斜率。

5.如权利要求3所述的半导体装置,其中,所述导电屏蔽线的侧表面具有正斜率。

6.如权利要求1所述的半导体装置,其中:

7.如权利要求1所述的半导体装置,其中:

8.如权利要求7所述的半导体装置,其中,所述位线与所述第一接触插塞的上表面和所述第一接触插塞的上部区域的侧表面接触。

9.如权利要求7所述的半导体装置,其中,所述位线的与所述第一接触插塞接触的下表面具有向下弯曲的形状。

10.如权利要求1所述的半导体装置,其中,所述位线的最下端位于比所述导电屏蔽线的最下端低的水平高度处。

11.如权利要求1所述的半导体装置,还包括:

12.如权利要求11所述的半导体装置,还包括:

13.如权利要求1所述的半导体装置,其中,所述下结构包括:

14.如权利要求1所述的半导体装置,其中,所述封盖绝缘层包括与所述层间绝缘层的材料不同的材料。

15.一种半导体装置,包括:

16.如权利要求15所述的半导体装置,其中,所述第二导电线包括导电图案以及覆盖所述导电图案的侧表面和底表面的阻挡层。

17.如权利要求15所述的半导体装置,其中:

18.一种半导体装置,包括:

19.如权利要求18所述的半导体装置,其中,所述位线中的每一条的最下端位于比所述导电屏蔽线中的每一条的最下端低的水平高度处。

20.如权利要求18所述的半导体装置,其中,所述位线中的每一条的宽度大于所述导电屏蔽线中的每一条的宽度。

技术总结

一种半导体装置,包括下结构、下结构上的层间绝缘层、在下结构上并穿过层间绝缘层的导电屏蔽线、层间绝缘层和导电屏蔽线上的封盖绝缘层、以及在下结构上并穿过封盖绝缘层和层间绝缘层的位线。位线的上表面位于比导电屏蔽线的上表面高的水平高度处。位线的下表面位于等于或低于导电屏蔽线的下表面的水平高度处。

技术研发人员:张志熏,宋在俊,河宪俊,李钟武

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!