采样开关电路、模数转换电路、芯片及电子设备的制作方法

本公开的实施例涉及集成电路,具体地,涉及采样开关电路、模数转换电路、芯片及电子设备。

背景技术:

1、集成电路的前端输入信号的采样精度直接影响集成电路整体性能,因此减少信号采样失真至关重要。传统互补金属氧化物半导体(complementary metal oxidesemiconductor,cmos)栅压自举采样开关电路为了抑制普通n型金属-氧化物-半导体(n-metal-oxide-semiconductor,nmos)开关由于背栅效应造成的输出失真,使用深n阱(deepn-well,dnw)nmos器件将p型衬底(p-sub)和体端(bulk)隔离开来。但是使用dnw nmos器件存在采样线性度的问题。

技术实现思路

1、本文中描述的实施例提供了一种采样开关电路、模数转换电路、芯片及电子设备。

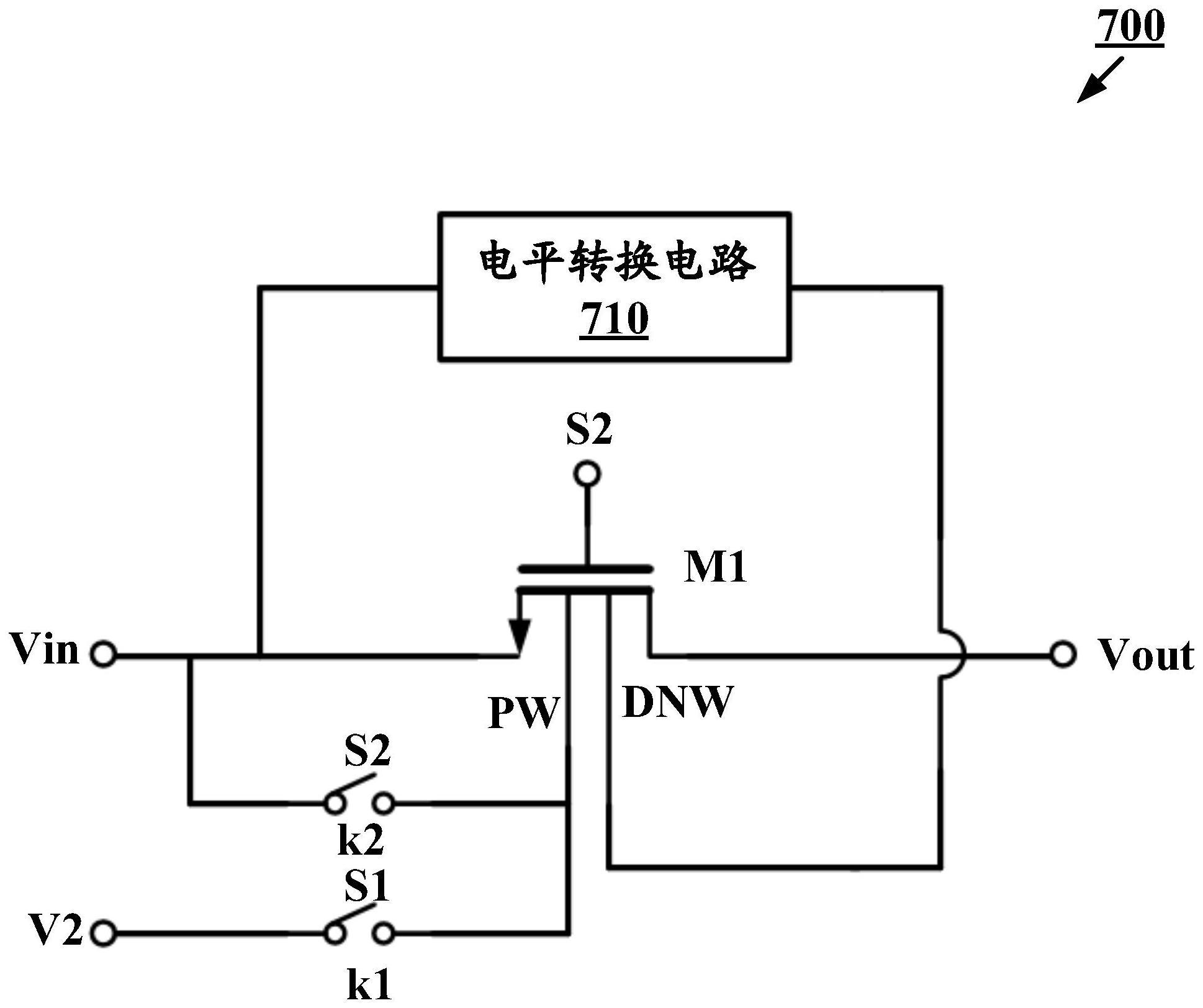

2、根据本公开的第一方面,提供了一种采样开关电路。该采样开关电路包括:第一晶体管、第一压控开关、第二压控开关以及电平转换电路。其中,第一晶体管是深n阱nmos晶体管。第一晶体管的控制极耦接采样控制端。第一晶体管的第一极耦接输入电压端。第一晶体管的第二极耦接输出电压端。第一晶体管的深n阱耦接电平转换电路的输出端。第一晶体管的p阱耦接第一压控开关的第一端和第二压控开关的第一端。第一压控开关的受控端耦接保持控制端。第一压控开关的第二端耦接第二电压端。第二压控开关的受控端耦接采样控制端。第二压控开关的第二端耦接输入电压端。电平转换电路被配置为:在采样开关电路进行信号采样时,生成并输出与来自输入电压端的输入电压线性正相关的线性驱动电压;在采样开关电路不进行信号采样时,输出电源电压。其中,在采样开关电路进行信号采样时,来自采样控制端的采样控制信号处于有效电平,来自保持控制端的保持控制信号处于无效电平。在采样开关电路不进行信号采样时,采样控制信号处于无效电平,保持控制信号处于有效电平。

3、在本公开的一些实施例中,电平转换电路包括:第三压控开关、第四压控开关、第二晶体管、第一电流源以及第一升压电路。其中,第三压控开关的受控端耦接保持控制端。第三压控开关的第一端耦接电源电压端。第三压控开关的第二端耦接第一升压电路的输出端和第二晶体管的控制极。第四压控开关的受控端耦接采样控制端。第四压控开关的第一端耦接输入电压端。第四压控开关的第二端耦接第一升压电路的输入端。第一升压电路被配置为:将第一升压电路的输入端处的电压升高固定值后输出。第二晶体管的第一极耦接电平转换电路的输出端和第一电流源。第二晶体管的第二极耦接第一电压端。第一电流源被配置为:生成第一恒定电流并向第二晶体管提供第一恒定电流。

4、在本公开的一些实施例中,电平转换电路包括:第五压控开关、第六压控开关、第三晶体管以及第二电流源。其中,第五压控开关的受控端耦接保持控制端。第五压控开关的第一端耦接电源电压端。第五压控开关的第二端耦接第三晶体管的控制极和第六压控开关的第二端。第六压控开关的受控端耦接采样控制端。第六压控开关的第一端耦接输入电压端。第三晶体管的第一极耦接电平转换电路的输出端和第二电流源。第三晶体管的第二极耦接第二电压端。第二电流源被配置为:生成第二恒定电流并向第三晶体管提供第二恒定电流。

5、在本公开的一些实施例中,电平转换电路包括:第七压控开关、第八压控开关、第九压控开关、第四晶体管、第五晶体管以及第二升压电路。其中,第七压控开关的受控端耦接保持控制端。第七压控开关的第一端耦接电源电压端。第七压控开关的第二端耦接第四晶体管的控制极和第二升压电路的输出端。第八压控开关的受控端耦接采样控制端。第八压控开关的第一端耦接输入电压端。第八压控开关的第二端耦接第五晶体管的控制极和第二升压电路的输入端。第九压控开关的受控端耦接保持控制端。第九压控开关的第一端耦接电源电压端。第九压控开关的第二端耦接第五晶体管的控制极和第二升压电路的输入端。第二升压电路被配置为:将第二升压电路的输入端处的电压升高固定值后输出。第四晶体管的第二极耦接第一电压端。第四晶体管的第一极耦接电平转换电路的输出端和第五晶体管的第一极。第五晶体管的第二极耦接第二电压端。

6、在本公开的一些实施例中,第二压控开关是第六晶体管。第六晶体管是深n阱nmos晶体管。第六晶体管的控制极耦接采样控制端。第六晶体管的第一极耦接第一晶体管的p阱。第六晶体管的第二极耦接输入电压端。第六晶体管的深n阱耦接第一晶体管的深n阱。第六晶体管的p阱耦接第一晶体管的p阱。

7、在本公开的一些实施例中,第一压控开关是第七晶体管。第七晶体管的控制极耦接保持控制端。第七晶体管的第一极耦接第二电压端。第七晶体管的第二极耦接第一晶体管的p阱。

8、根据本公开的第二方面,提供了一种采样开关电路。该采样开关电路包括:第一晶体管、第二晶体管、第六晶体管、第七晶体管、第三压控开关、第四压控开关、第一电流源以及第一升压电路。其中,第一晶体管是深n阱nmos晶体管。第一晶体管的控制极耦接采样控制端。第一晶体管的第一极耦接输入电压端。第一晶体管的第二极耦接输出电压端。第一晶体管的深n阱耦接第六晶体管的深n阱和第二晶体管的第一极。第一晶体管的p阱耦接第六晶体管的第一极、第六晶体管的p阱和第七晶体管的第二极。第六晶体管是深n阱nmos晶体管。第六晶体管的控制极耦接采样控制端。第六晶体管的第二极耦接输入电压端。第七晶体管的控制极耦接保持控制端。第七晶体管的第一极耦接第二电压端。第三压控开关的受控端耦接保持控制端。第三压控开关的第一端耦接电源电压端。第三压控开关的第二端耦接第一升压电路的输出端和第二晶体管的控制极。第四压控开关的受控端耦接采样控制端。第四压控开关的第一端耦接输入电压端。第四压控开关的第二端耦接第一升压电路的输入端。第一升压电路被配置为:将第一升压电路的输入端处的电压升高固定值后输出。第二晶体管的第一极耦接第一电流源。第二晶体管的第二极耦接第一电压端。第一电流源被配置为:生成第一恒定电流并向第二晶体管提供第一恒定电流。其中,在采样开关电路进行信号采样时,来自采样控制端的采样控制信号处于有效电平,来自保持控制端的保持控制信号处于无效电平。在采样开关电路不进行信号采样时,采样控制信号处于无效电平,保持控制信号处于有效电平。

9、根据本公开的第三方面,提供了一种模数转换电路。该模数转换电路包括根据本公开的第一方面或第二方面所述的采样开关电路。

10、根据本公开的第四方面,提供了一种芯片。该芯片包括根据本公开的第三方面所述的模数转换电路。

11、根据本公开的第五方面,提供了一种电子设备。该电子设备包括根据本公开的第四方面所述的芯片。

技术特征:

1.一种采样开关电路,包括:第一晶体管、第一压控开关、第二压控开关以及电平转换电路,

2.根据权利要求1所述的采样开关电路,其中,所述电平转换电路包括:第三压控开关、第四压控开关、第二晶体管、第一电流源以及第一升压电路,

3.根据权利要求1所述的采样开关电路,其中,所述电平转换电路包括:第五压控开关、第六压控开关、第三晶体管以及第二电流源,

4.根据权利要求1所述的采样开关电路,其中,所述电平转换电路包括:第七压控开关、第八压控开关、第九压控开关、第四晶体管、第五晶体管以及第二升压电路,

5.根据权利要求1至4中任一项所述的采样开关电路,其中,所述第二压控开关是第六晶体管,所述第六晶体管是深n阱nmos晶体管,所述第六晶体管的控制极耦接所述采样控制端,所述第六晶体管的第一极耦接所述第一晶体管的p阱,所述第六晶体管的第二极耦接所述输入电压端,所述第六晶体管的深n阱耦接所述第一晶体管的深n阱,所述第六晶体管的p阱耦接所述第一晶体管的p阱。

6.根据权利要求1至4中任一项所述的采样开关电路,其中,所述第一压控开关是第七晶体管,所述第七晶体管的控制极耦接所述保持控制端,所述第七晶体管的第一极耦接所述第二电压端,所述第七晶体管的第二极耦接所述第一晶体管的p阱。

7.一种采样开关电路,包括:第一晶体管、第二晶体管、第六晶体管、第七晶体管、第三压控开关、第四压控开关、第一电流源以及第一升压电路,

8.一种模数转换电路,包括:根据权利要求1至7中任一项所述的采样开关电路。

9.一种芯片,包括:根据权利要求8所述的模数转换电路。

10.一种电子设备,包括:根据权利要求9所述的芯片。

技术总结

本公开的实施例提供一种采样开关电路、模数转换电路、芯片及电子设备。采样开关电路包括:第一晶体管、第一和第二压控开关、电平转换电路。第一晶体管是深N阱NMOS晶体管。第一晶体管的控制极耦接采样控制端和第二压控开关的受控端。第一晶体管的第一极耦接输入电压端和第二压控开关的第二端。第一晶体管的第二极耦接输出电压端。第一晶体管的深N阱耦接电平转换电路的输出端。第一晶体管的P阱耦接第一和第二压控开关的第一端。第一压控开关的受控端耦接保持控制端。第一压控开关的第二端耦接第二电压端。电平转换电路在信号采样期间生成并输出与输入电压线性正相关的线性驱动电压。在采样开关电路进行信号采样时采样控制信号处于有效电平。

技术研发人员:张义桢

受保护的技术使用者:圣邦微电子(北京)股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!