一种缩延时驱动电路与电子设备的制作方法

本申请涉及缩延时,具体而言,涉及一种缩延时驱动电路与电子设备。

背景技术:

1、近年来随着半导体行业的兴起,越来越多的芯片相继推出,行业竞争也越来越激烈,锂电池保护领域更是如此。因此芯片成本越低,性价比越高才能让产品具有更强的竞争力。而在芯片的cp和ft测试阶段能提高测试良率缩短测试时间同样能提升产品竞争力。

2、但是在芯片cp测试阶段由于芯片某些功能有较长的保护延时,而当需要cp的芯片数量较多时就会耗费大量时间,进而增加了芯片成本延长了芯片的量产时间。

3、因此,为了缩短测试时间,一般芯片内还包括缩延时模块,缩延时模块一般需要特定的驱动信号,但目前的驱动电路一般较为复杂。

4、综上,现有技术中存在缩延时模块的驱动电路较为复杂的问题。

技术实现思路

1、本申请的目的在于提供缩延时驱动电路,以解决现有技术中存在的缩延时模块的驱动电路较为复杂的问题。

2、为了实现上述目的,本申请实施例采用的技术方案如下:

3、一方面,本申请实施例提供了一种缩延时驱动电路,所述缩延时驱动电路包括上拉模块、下拉模块、传输模块以及触发器,所述上拉模块、所述下拉模块均与所述传输模块电连接,所述上拉模块还连接电源,所述下拉模块还接地,所述传输模块与所述触发器电连接;其中,

4、当处于正常工作状态时,所述上拉模块关断,所述下拉模块导通,以通过所述传输模块向所述触发器输出低电平信号,所述触发器也输出低电平信号;

5、当处于缩延时状态时,所述上拉模块导通,以通过所述传输模块向所述触发器输出高电平信号,所述触发器也输出高电平信号。

6、可选地,所述上拉模块包括第一pmos管,第二pmos管以及pmos管组,所述pmos管组包括多个串联的二极管接法的pmos管,所述第一pmos管、所述第二pmos管的源极均连接电源,所述第一pmos管的栅极分别连接第一pmos管的漏极与所述第二pmos管的栅极,所述第一pmos管的漏极通过所述pmos管组接地,所述第二pmos管的漏极与所述传输模块的输入端电连接;其中,

7、当所述电源电压低于阈值时,所述缩延时驱动电路处于正常工作状态,所述第一pmos管与所述第二pmos管均关断;

8、当所述电源电压高于阈值时,所述缩延时驱动电路处于缩延时工作状态,所述第一pmos管导通,以使所述第二pmos管导通。

9、可选地,所述上拉模块还包括第三pmos管与连接单元,所述第三pmos管的源极连接电源,所述第三pmos管的栅极连接所述第一pmos管的栅极,所述第三pmos管的漏极与连接单元电连接,且所述连接单元与所述传输模块的输入端电连接。

10、可选地,所述连接单元还包括第四pmos管,所述传输模块包括第一反相器与第二反相器,第四pmos管的源极与所述第三pmos管的漏极电连接,所述第四pmos管的漏极与所述下拉模块均与所述第一反相器的输入端电连接,所述第四pmos管的栅极与所述第一反相器的输出端电连接,所述第一反相器的输出端还与所述第二反相器的输入端电连接,所述第二反相器的输出端与所述触发器电连接。

11、可选地,所述上拉模块的上拉能力大于所述下拉模块的下拉能力,当处于缩延时状态时,所述下拉模块也导通。

12、可选地,所述下拉模块包括第一nmos管,所述第一nmos管的源极接地,所述第一nmos管的漏极连接所述传输模块,所述第一nmos管的栅极输入偏置电压,并在处于正常工作状态与缩延时状态时均导通。

13、可选地,所述缩延时驱动电路还包括第二nmos管,所述第二nmos管的栅极与所述传输模块的输入端电连接,所述第二nmos管的源极与漏极均接地。

14、可选地,所述缩延时驱动电路还包括第三nmos管,所述第三nmos管的漏极与所述传输模块的输入端电连接,所述第三nmos管的源极接地,所述第三nmos管的栅极连接驱动信号。

15、可选地,所述触发器包括rs触发器,所述传输模块与所述rs触发器的s端电连接,所述rs触发器的r端用于接收低电平使能信号。

16、另一方面,本申请实施例还提供了一种电子设备,所述电子设备包括上述的缩延时驱动电路。

17、相对于现有技术,本申请具有以下有益效果:

18、本申请提供了一种缩延时驱动电路与电子设备,该缩延时驱动电路包括上拉模块、下拉模块、传输模块以及触发器,上拉模块、下拉模块均与传输模块电连接,上拉模块还连接电源,下拉模块还接地,传输模块与触发器电连接;其中,当处于正常工作状态时,上拉模块关断,下拉模块导通,以通过传输模块向触发器输出低电平信号,触发器也输出低电平信号;当处于缩延时状态时,上拉模块导通,以通过传输模块向触发器输出高电平信号,触发器也输出高电平信号。一方面,由于在正常状态时,该缩延时驱动电路可以输出低电平信号,而在处于缩延时状态时,可以输出高电平信号,因此实现了驱动信号的输出。另一方面,本申请提供的缩延时驱动电路中,电路结构相对简单,且器件数量相对较少,并且在正常工作状态下不会产生功耗,成本较低。

19、为使本申请的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:

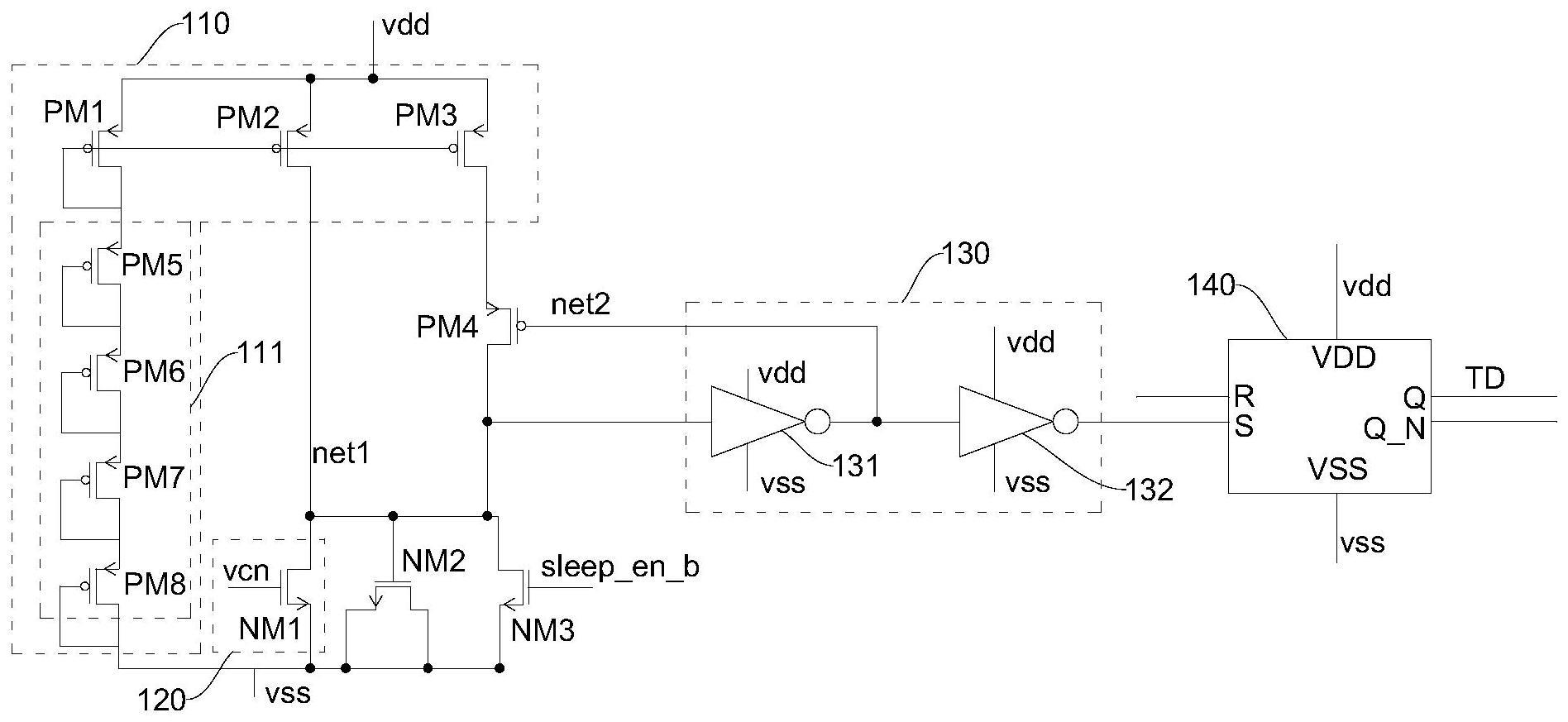

1.一种缩延时驱动电路(100),其特征在于,所述缩延时驱动电路(100)包括上拉模块(110)、下拉模块(120)、传输模块(130)以及触发器(140),所述上拉模块(110)、所述下拉模块(120)均与所述传输模块(130)电连接,所述上拉模块(110)还连接电源,所述下拉模块(120)还接地,所述传输模块(130)与所述触发器(140)电连接;其中,

2.如权利要求1所述的缩延时驱动电路(100),其特征在于,所述上拉模块(110)包括第一pmos管(pm1),第二pmos管(pm2)以及pmos管组,所述pmos管组(111)包括多个串联的二极管接法的pmos管,所述第一pmos管(pm1)、所述第二pmos管(pm2)的源极均连接电源,所述第一pmos管(pm1)的栅极分别连接第一pmos管(pm1)的漏极与所述第二pmos管(pm2)的栅极,所述第一pmos管(pm1)的漏极通过所述pmos管组(111)接地,所述第二pmos管(pm2)的漏极与所述传输模块(130)的输入端电连接;其中,

3.如权利要求2所述的缩延时驱动电路(100),其特征在于,所述上拉模块(110)还包括第三pmos管(pm3)与连接单元,所述第三pmos管(pm3)的源极连接电源,所述第三pmos管(pm3)的栅极连接所述第一pmos管(pm1)的栅极,所述第三pmos管(pm3)的漏极与所述连接单元电连接,且所述连接单元与所述传输模块(130)的输入端电连接。

4.如权利要求3所述的缩延时驱动电路(100),其特征在于,所述连接单元包括第四pmos管(pm4),所述传输模块(130)包括第一反相器(131)与第二反相器(132),第四pmos管(pm4)的源极与所述第三pmos管(pm3)的漏极电连接,所述第四pmos管(pm4)的漏极与所述下拉模块(120)均与所述第一反相器(131)的输入端电连接,所述第四pmos管(pm4)的栅极与所述第一反相器(131)的输出端电连接,所述第一反相器(131)的输出端还与所述第二反相器(132)的输入端电连接,所述第二反相器(132)的输出端与所述触发器(140)电连接。

5.如权利要求1所述的缩延时驱动电路(100),其特征在于,所述上拉模块(110)的上拉能力大于所述下拉模块(120)的下拉能力,当处于缩延时状态时,所述下拉模块(120)也导通。

6.如权利要求5所述的缩延时驱动电路(100),其特征在于,所述下拉模块(120)包括第一nmos管(nm1),所述第一nmos管(nm1)的源极接地,所述第一nmos管(nm1)的漏极连接所述传输模块(130),所述第一nmos管(nm1)的栅极输入偏置电压,并在处于正常工作状态与缩延时状态时均导通。

7.如权利要求1所述的缩延时驱动电路(100),其特征在于,所述缩延时驱动电路(100)还包括第二nmos管(nm2),所述第二nmos管(nm2)的栅极与所述传输模块(130)的输入端电连接,所述第二nmos管(nm2)的源极与漏极均接地。

8.如权利要求1所述的缩延时驱动电路(100),其特征在于,所述缩延时驱动电路(100)还包括第三nmos管(nm3),所述第三nmos管(nm3)的漏极与所述传输模块(130)的输入端电连接,所述第三nmos管(nm3)的源极接地,所述第三nmos管(nm3)的栅极连接驱动信号。

9.如权利要求1所述的缩延时驱动电路(100),其特征在于,所述触发器(140)包括rs触发器,所述传输模块(130)与所述rs触发器的s端电连接,所述rs触发器的r端用于接收低电平使能信号。

10.一种电子设备,其特征在于,所述电子设备包括如权利要求1至9任一项所述的缩延时驱动电路(100)。

技术总结

本申请提供了一种缩延时驱动电路与电子设备,涉及缩延时技术领域。该缩延时驱动电路包括上拉模块、下拉模块、传输模块以及触发器,上拉模块、下拉模块均与传输模块电连接,上拉模块还连接电源,下拉模块还接地,传输模块与触发器电连接;其中,当处于正常工作状态时,上拉模块关断,下拉模块导通,以通过传输模块向触发器输出低电平信号,触发器也输出低电平信号;当处于缩延时状态时,上拉模块导通,以通过传输模块向触发器输出高电平信号,触发器也输出高电平信号。本申请提供的缩延时驱动电路与电子设备具有实现了为缩延时模块提供驱动信号且功耗较低的效果。

技术研发人员:张正旭

受保护的技术使用者:芯弘微电子(深圳)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!