用于制造半导体装置的方法与流程

本公开涉及半导体技术的领域,具体地,本公开涉及一种用于制造包括整体形成的非易失性存储器(nvm)晶体管和金属氧化物半导体(mos)晶体管的半导体装置的方法。

背景技术:

1、快闪存储器,简称闪存,是一种非易失性存储器(nvm),即在电源断开的情况下仍然不会丢失所存储的数据,特别适用于移动通讯和计算机存储部件等领域。此外,有些闪存还具有高密度存储能力,适用于大容量移动存储介质等方面的应用。

2、传统的闪存使用浮栅型单元结构或sonos型(silicon-oxide-nitride-oxide-silicon:硅-氧化物-氮化物-氧化物-硅)单元结构。然而,然而,现有的浮栅型闪存和sonos型闪存都存在工艺尺寸无法缩小、单元面积大、写入功耗大及阵列面积开销大的问题,无法实现吉比特(gb)容量以上的高密度集成。

3、此外,对于诸如片上系统的许多应用,期望将金属氧化物半导体(mos)晶体管和nvm晶体管集成在单个芯片或衬底上。然而,这种集成会严重影响mos晶体管和nvm晶体管的制造工艺。

4、mos晶体管通常使用基准互补金属氧化物半导体(cmos)工艺流程来制造,包括导体、半导体和电介质材料的形成和图案化。在cmos工艺流程中使用的这些材料的组合、加工试剂的组合和浓度以及温度等对于每个工艺步骤是严格控制的,以确保获得的mos晶体管能够正常操作。

5、此外,nvm晶体管包括栅介质叠层,其通常包括两个氧化物层以及夹在它们之间的氮化物层或氮氧化物层,而制造这两个氧化物层的材料和工艺通常不同于基准的cmos工艺流程的材料和工艺,因此可能对mos晶体管的制造造成不利影响,或者受到mos晶体管制造的影响。

6、因此,nvm晶体管和mos晶体管的集成可能严重影响基准cmos工艺流程,并且通常需要数目众多的掩模设置和处理步骤,这增加了制造成本并且降低了生产效率。

7、在本背景技术部分中公开的以上信息仅用于理解本发明构思的背景,并且因此可能包含不构成现有技术的信息。

技术实现思路

1、为了解决现有技术中存在的以上问题,本公开提出了新型的用于制造包括整体形成的非易失性存储器(nvm)晶体管和金属氧化物半导体(mos)晶体管的半导体装置的方法。

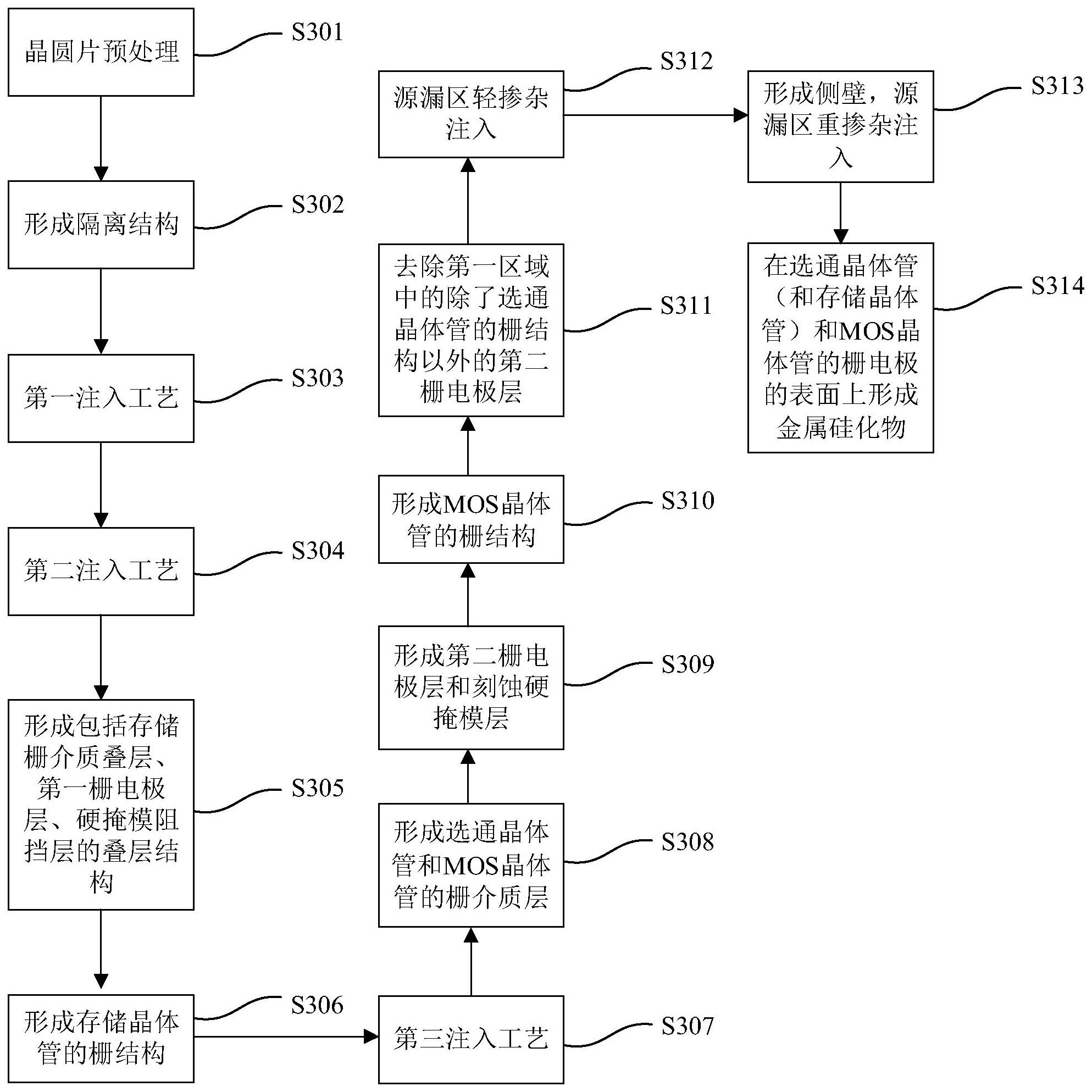

2、根据本公开的一个方面,提供了一种用于制造半导体装置的方法。该半导体装置包括其中形成多个闪存单元的第一区域和其中形成金属氧化物半导体(mos)晶体管的第二区域,并且每个闪存单元包括两个存储晶体管和设置在两个存储晶体管之间的一个选通晶体管。根据本公开的用于制造半导体装置的方法包括:提供半导体衬底并且在其中形成隔离结构;形成存储晶体管的存储栅介质叠层和第一栅电极层;通过对存储栅介质叠层和第一栅电极层构图形成存储晶体管的栅结构;并发地形成选通晶体管和mos晶体管的栅介质层和第二栅电极层;以及并发地形成mos晶体管的栅结构和选通晶体管的栅结构。

3、根据本公开的用于制造半导体装置的方法,可以将非易失性存储器(nvm)晶体管集成到mos晶体管的制造工艺中。

4、然而,本公开的效果不限于上述效果,并且可以在不脱离本公开的精神和范围的情况下进行各种扩展。应当理解,前面的通常描述和下面的详细描述都是示例性和解释性的,并且旨在提供对要求保护的本公开的进一步说明。

技术特征:

1.一种用于制造半导体装置的方法,

2.根据权利要求1所述的方法,其中,所述存储晶体管的栅结构沿竖直方向自下而上包括沟道区、所述存储栅介质叠层、所述第一栅电极层和硬掩模阻挡部,

3.根据权利要求1所述的方法,其中,所述第二栅电极层的上表面高于所述第一栅电极层的上表面。

4.根据权利要求1所述的方法,其中,设置在所述第二区域中的mos晶体管包括低压mos晶体管、接口mos晶体管或高压mos晶体管中的一种或更多种。

5.根据权利要求4所述的方法,其中,所述选通晶体管的栅介质层的厚度与所述低压mos晶体管、所述接口mos晶体管和所述高压mos晶体管中的任一种的栅介质层的厚度相同。

6.根据权利要求1所述的方法,其中,所述第一区域中的闪存单元通过第一隔离结构隔离,所述第二区域中的mos晶体管通过第二隔离结构隔离,并且所述第一区域和所述第二区域通过所述第一隔离结构和/或所述第二隔离结构隔离,以及

7.根据权利要求1所述的方法,还包括:

8.根据权利要求7所述的方法,其中,所述第二注入工艺在形成所述存储晶体管的存储栅介质叠层和第一栅电极层之前执行,或者在通过对所述存储栅介质叠层和所述第一栅电极层构图形成所述存储晶体管的栅结构之后执行。

9.根据权利要求7所述的方法,其中,执行所述第一注入工艺和所述第三注入工艺使得所述存储晶体管的沟道区的掺杂浓度低于所述选通晶体管的沟道区的掺杂浓度。

10.根据权利要求1所述的方法,其中,所述存储栅介质叠层沿竖直方向自下而上包括第一氧化物层、存储介质层和第二氧化物层,

11.根据权利要求10所述的方法,其中,所述存储介质层还包括所述第三存储介质子层上方的第四存储介质子层,以及

12.根据权利要求1所述的方法,还包括:在所述存储栅介质叠层和所述第一栅电极层之间形成高功函数金属界面层。

13.根据权利要求1所述的方法,还包括:形成用于隔离所述选通晶体管和所述存储晶体管的隔离层。

14.根据权利要求1所述的方法,还包括:在所述选通晶体管和所述mos晶体管的栅电极的表面上形成金属硅化物。

15.根据权利要求14所述的方法,还包括:在所述存储晶体管的栅电极的全部或部分表面上形成金属硅化物。

技术总结

本公开提供了一种用于制造半导体装置的方法。该半导体装置包括其中形成多个闪存单元的第一区域和其中形成金属氧化物半导体(MOS)晶体管的第二区域,每个闪存单元包括两个存储晶体管和设置在两个存储晶体管之间的选通晶体管。根据本公开的用于制造半导体装置的方法包括:提供半导体衬底并在其中形成隔离结构;形成存储晶体管的存储栅介质叠层和第一栅电极层;通过对存储栅介质叠层和第一栅电极层构图形成存储晶体管的栅结构;并发地形成选通晶体管和MOS晶体管的栅介质层和第二栅电极层;以及并发地形成MOS晶体管的栅结构和选通晶体管的栅结构。根据本公开的用于制造半导体装置的方法,可以将非易失性存储器(NVM)晶体管集成到MOS晶体管的制造工艺中。

技术研发人员:蒋家勇,请求不公布姓名,石振东

受保护的技术使用者:北京磐芯微电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!