一种在使用多个旋钮编码器场景下节省芯片IO口的方法与流程

本发明涉及编码器,更具体地说是指一种在使用多个旋钮编码器场景下节省芯片io口的方法。

背景技术:

1、随着电子技术中编码器的广泛应用,编码器是一种通过信号转换原理把输出轴上的机械位移量转化为脉冲信号或者数字量的传感器。按照工作性质划分,编码器可分为增量型编码器和绝对值编码器。增量型编码器有着构造简单,机械寿命长,抗干扰能力强,适合速度和长度传输,可靠性高的优点,缺点是不能直观的输出位置信号。绝对值编码器有高位数分辨率的特征,且其机械位置决定的每个位置是唯一的,无需找参考点,抗干扰性和可靠性更高,有很好的定位功能。

2、使用多个旋钮编码器时,目前大多数方法都是将每个旋钮编码器的a、b脚都接到芯片的io口上,当使用场景需要较多旋钮编码器时,经常会导致芯片io口不够用不得不更换更多引脚的芯片,都存在一些缺点,具体缺点如下:

3、不足1:占用过多的芯片io口,造成资源的浪费;

4、不足2:每个旋钮编码器顺时针、逆时针旋转都需要软件单独计算判断,造成软件算法实现复杂。

技术实现思路

1、本发明的目的在于克服现有技术的缺陷,提供一种在使用多个旋钮编码器场景下节省芯片io口的方法,目的在于减少使用多个旋钮编码器时需要的芯片io口数量,首先将每个旋钮编码器上a、b端的脉冲信号通过两个d触发器转变为电平信号,再将所有的电平信号连接到移位寄存器的并行数据接口上,移位寄存器将并行数据转串行数据最终被主控芯片读取到。

2、为实现上述目的,本发明采用以下技术方案:

3、9.一种在使用多个旋钮编码器场景下节省芯片io口的方法,包括多个旋钮编码器、主控芯片和移位寄存器,所述主控芯片并行输入所述移位寄存器的接口;

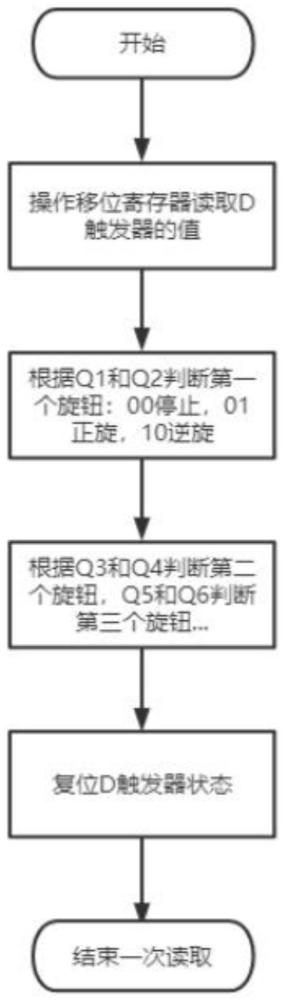

4、所述在使用多个旋钮编码器场景下节省芯片io口的方法具体步骤方法如下:

5、s01、将每个所述旋钮编码器上的a、b端的脉冲信号通过两个d触发器转变为电平信号;

6、s02、所述旋钮编码器将轴的角运动转换为a、b两个输出相位偏差90°的脉冲信号;

7、s03、再将所有的电平信号连接到所述移位寄存器的并行数据接口上;

8、s04、所述移位寄存器将并行数据连接到所述主控芯片;

9、s05、所述主控芯片读取到所述移位寄存器的并行数据转成的串行数据;

10、s06、所述主控芯片通过根据串行数据能依次判断出多个所述旋钮编码器的状态;

11、s07、当所述旋钮编码器顺时针旋转,第一个d触发器的输出q1=0,第二个d触发器的输出q2=1;

12、s08、当所述旋钮编码器逆时针旋转时则q1=1,q2=0;

13、s09、所述主控芯片读取数据之后,再依次通过q3和q4判断第二旋钮的旋转状态,通过q5和q6判断第三旋钮的旋转状态,直至第n个旋钮的旋转状态;

14、s10、所述主控芯片再通过rd端将复位所述d触发器置零。

15、进一步方案为,所述移位寄存器为并行输入并行数据,串行输出到所述主控芯片上。

16、进一步方案为,所述旋钮编码器有a、b、c三端,使用时a、b接上电阻,所述c端接地。

17、进一步方案为,所述旋钮编码器根据a、b信号的相位关系可以获得旋转方向,根据脉冲在单位时间内的计数可以获得角速度。

18、进一步方案为,当旋钮顺时针转动时b端输出脉冲相位超前90°,当旋钮逆时针转动时a端输出脉冲相位超前90°。

19、进一步方案为,所述旋钮编码器的a端接第一个d触发器的d端,所述旋钮编码器的b端接第一个d触发器的clk端。

20、进一步方案为,所述旋钮编码器a端还接第二个d触发器的clk端,旋钮编码器b端接第二个d触发器的d端。

21、进一步方案为,所述主控芯片通过第一个d触发器的输出q1和第二个d触发器的输出q2,来判断所述述旋钮编码器的旋转方向。

22、本发明与现有技术相比的有益效果是:目的在于减少使用多个旋钮编码器时需要的芯片io口数量,实现原理为:首先将每个旋钮编码器上a、b端的脉冲信号通过两个d触发器转变为电平信号,再将所有的电平信号连接到移位寄存器的并行数据接口上,移位寄存器将并行数据转成串行数据最终被主控芯片读取到,这样多个旋钮编码器的旋转状态就能输出到主控芯片上,具有以下优点:

23、进步1:节省主控芯片被多个旋钮编码器占用多个io接口资源;

24、进步2:同时降低了软件及设计的复杂度。

技术特征:

1.一种在使用多个旋钮编码器场景下节省芯片io口的方法,其特征在于,包括多个旋钮编码器、主控芯片和移位寄存器,所述主控芯片并行输入所述移位寄存器的接口;

2.如权利要求1所述的在使用多个旋钮编码器场景下节省芯片io口的方法,其特征在于,所述移位寄存器为并行输入并行数据,串行输出到所述主控芯片上。

3.如权利要求1所述的在使用多个旋钮编码器场景下节省芯片io口的方法,其特征在于,所述旋钮编码器有a、b、c三端,使用时a、b接上电阻,所述c端接地。

4.一种在使用多个旋钮编码器场景下节省芯片io口的方法,其特征在于,所述旋钮编码器根据a、b信号的相位关系可以获得旋转方向,根据脉冲在单位时间内的计数可以获得角速度。

5.如权利要求1所述的在使用多个旋钮编码器场景下节省芯片io口的方法,其特征在于,当旋钮顺时针转动时b端输出脉冲相位超前90°,当旋钮逆时针转动时a端输出脉冲相位超前90°。

6.如权利要求1所述的在使用多个旋钮编码器场景下节省芯片io口的方法,其特征在于,所述旋钮编码器的a端接第一个d触发器的d端,所述旋钮编码器的b端接第一个d触发器的clk端。

7.如权利要求1所述的在使用多个旋钮编码器场景下节省芯片io口的方法,其特征在于,所述旋钮编码器a端还接第二个d触发器的clk端,旋钮编码器b端接第二个d触发器的d端。

8.如权利要求1所述的在使用多个旋钮编码器场景下节省芯片io口的方法,其特征在于,所述主控芯片通过第一个d触发器的输出q1和第二个d触发器的输出q2,来判断所述述旋钮编码器的旋转方向。

技术总结

本发明提供一种在使用多个旋钮编码器场景下节省芯片IO口的方法,包括多个旋钮编码器、主控芯片和移位寄存器,当有多个旋钮编码器时,每个旋钮编码器接两个D触发器,再将所有D触发器的输出接入一个移位寄存器,移位寄存器将并口数据转成串口数据给到主控芯片,主控芯片就能依次判断出旋钮编码器的状态了;减少了使用多个旋钮编码器时需要的主控芯片IO口数量,每个旋钮编码器上A、B端的脉冲信号通过两个D触发器转变为电平信号,再将所有的电平信号连接到移位寄存器的并行数据接口上,移位寄存器将并行数据转串行数据最终被主控芯片读取到。

技术研发人员:苑志强,苑茂存

受保护的技术使用者:深圳市名扬时代电子有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!