一种用于高速数字信号的采集与数据处理系统的制作方法

本发明涉及高速数字信号处理,具体而言,涉及一种用于高速数字信号的采集与数据处理系统。

背景技术:

1、在高速传输的通讯系统中,时钟数据恢复(clock and data recovery,cdr)电路常被用来确保可以正确地读取所传输的输入数据;现有技术中,为了保证电路的具有更高的泛用性与可移植性,一般采用数字电路来实现,但若以全数字电路实施,则会因为时序延迟等限制而具有追踪相位能力不佳等问题;因此,急需设计一种新的用于高速数字信号的采集电路与数据处理技术,以克服全数字电路在实施过程中存在的问题。

技术实现思路

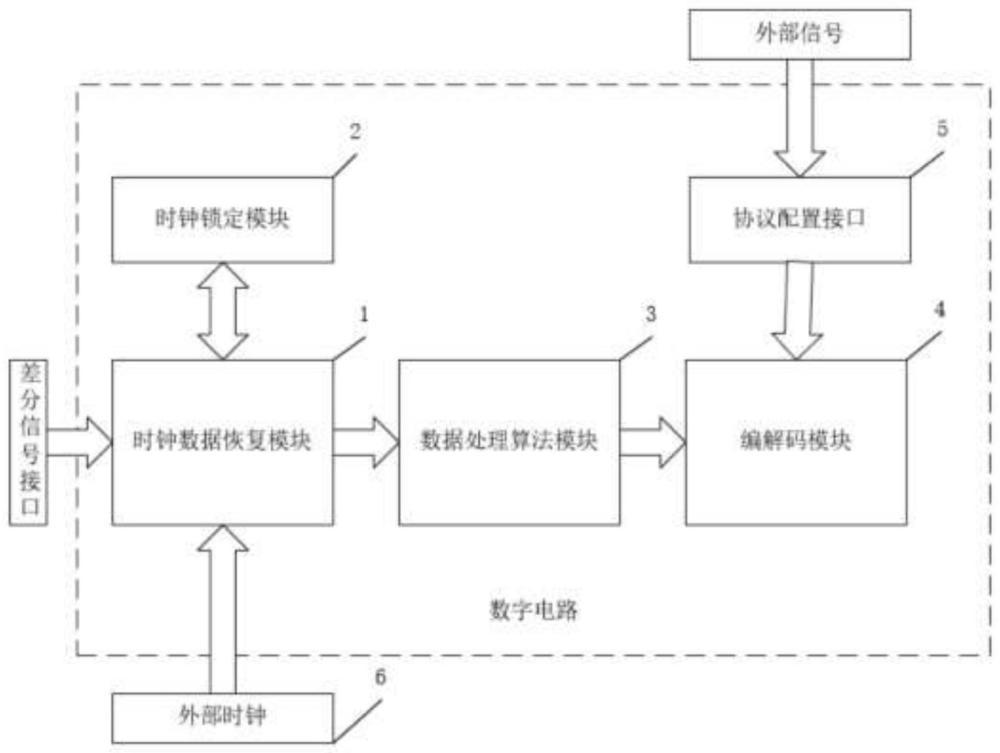

1、为了解决上述问题,本发明提供了一种用于高速数字信号的采集与数据处理系统,应用于无时钟差分信号接口,包括:

2、时钟数据恢复模块,采用多相位时钟与数据延迟双通道进行混合采样,使用低频时钟采集高速率的差分信号数据,获取过采样数据;

3、时钟锁定模块,与时钟数据恢复模块进行电性连接,用于根据差分信号数据选择适配的低频时钟;

4、数据处理算法模块,与时钟数据恢复模块进行电性连接,用于根据过采样数据,依据低频时钟对应的时钟信息进行降采样处理,生成并行信号;

5、编解码模块,与数据处理算法模块进行电性连接,用于根据并行信号,依据设置的协议内容完成时钟与数据的锁定和对齐,并进行打包输出。

6、优选地,时钟数据恢复模块,用于依据采样率高于数据速率两倍以上进行过采样,获取过采样数据。

7、优选地,时钟数据恢复模块,还用于检测过采样数据的跳变沿,判断亚稳态的出现位置,选择可靠的数据进行储存。

8、优选地,时钟锁定模块,还用于采用边沿探测与计时器捕捉差分信号数据的跳变,根据8b10b编码的特性,使用调节数据延迟的方法锁定时钟与数据相位,判断时钟与数据是否匹配,获取适配的低频时钟。

9、优选地,时钟数据恢复模块还用于根据编解码模块提供的8b10b编码,对差分信号数据,进行编码,生成过采样数据。

10、优选地,编解码模块,还用于根据8b10b编码,通过自定义加入其他协议,提高数据自由度,并通过增加加密或是数据包,提高数据安全性以及可靠性。

11、优选地,编解码模块,还用于通过协议配置接口,获取外部信号的协议,并加入到8b10b编码中,并将打包后的数据发送至外部信号的发送端。

12、优选地,编解码模块,还用于在打包后的数据发送至一定长度后,再重新发送包头进行对齐。

13、优选地,协议配置接口,还用于对编解码模块与发送端之间的协议内容与数据格式以及最大连续传输长度进行自行配置。

14、优选地,通过采集与数据处理系统对高速数字信号进行处理过程,包括以下步骤:

15、第一步,将高速数字信号通过差分信号接口发送至时钟数据恢复模块进行初始的数据采样,使用多个时钟对数据与其延迟进行采样,获得多倍的过采样数据;

16、第二步,将初始采样数据送入时钟锁定模块,通过检测数据跳变的频率锁定数据的速率,分析给出时钟信息,根据时钟信息调整数据的延迟,并将时钟信息送回时钟数据恢复模块进行恢复;

17、第三步,将过采样数据与时钟信息,输入信号处理算法模块进行降采样处理,根据时钟信息与计算结果得到可靠的数据并转换为并行信号;

18、第四步,将并行信号中的数据与时钟,输入编解码模块,根据编解码模块中的协议内容完成时钟与数据的锁定与对齐,通过将数据打包,传输一定长度后重新发送包头进行对齐。

19、本发明公开了以下技术效果:

20、本发明为纯数字电路结构,具有很高的可移植性;

21、本发明采用多相位时钟与数据延迟方式实现多倍采样,所需时钟频率低且稳定性高;

22、本发明的协议部分可由用户自定义,适用多种环境;

23、本发明为通用数据接收端,可以通过变更外部时钟变更采样速率。

技术特征:

1.一种用于高速数字信号的采集与数据处理系统,其特征在于,应用于无时钟差分信号接口,包括:

2.根据权利要求1所述一种用于高速数字信号的采集与数据处理系统,其特征在于:

3.根据权利要求2所述一种用于高速数字信号的采集与数据处理系统,其特征在于:

4.根据权利要求3所述一种用于高速数字信号的采集与数据处理系统,其特征在于:

5.根据权利要求4所述一种用于高速数字信号的采集与数据处理系统,其特征在于:

6.根据权利要求5所述一种用于高速数字信号的采集与数据处理系统,其特征在于:

7.根据权利要求6所述一种用于高速数字信号的采集与数据处理系统,其特征在于:

8.根据权利要求7所述一种用于高速数字信号的采集与数据处理系统,其特征在于:

9.根据权利要求8所述一种用于高速数字信号的采集与数据处理系统,其特征在于:

10.根据权利要求9所述一种用于高速数字信号的采集与数据处理系统,其特征在于:

技术总结

本发明公开了一种用于高速数字信号的采集与数据处理系统,属于高速数字信号处理技术领域,包括:时钟数据恢复模块,采用多相位时钟与数据延迟双通道进行混合采样,使用低频时钟采集高速率的差分信号数据,获取过采样数据;时钟锁定模块,与时钟数据恢复模块进行电性连接,用于根据差分信号数据选择适配的低频时钟;数据处理算法模块,与时钟数据恢复模块进行电性连接,用于根据过采样数据,依据低频时钟对应的时钟信息进行降采样处理,生成并行信号;编解码模块,与数据处理算法模块进行电性连接,用于根据并行信号,依据设置的协议内容完成时钟与数据的锁定和对齐,并进行打包输出;本发明为纯数字电路结构,具有很高的可移植性。

技术研发人员:刘志勇

受保护的技术使用者:武汉乐芯科技有限公司

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!