一种有源电感的制作方法

本发明涉及射频集成电路领域,特别涉及一种有源电感,更具体来说涉及一种具有高q值、高线性动态范围且电感值可独立调控的新型宽频带射频前端有源电感。

背景技术:

1、在射频集成电路中,电感是一个非常重要的模块。随着集成电路朝着高速、微型、可调方向的发展,对电感的性能也同样提出了更高的要求。传统的片上金属薄膜螺旋无源电感是由金属线在硅衬底上构成的,其电感值、q值、自谐振频率等性能参数均由金属线的形状、宽度和圈数决定,且面积越大电感值越大,因而传统的无源电感难以同时集小面积、高q值、高线性动态范围、宽频带于一体。这些不足,极大地限制了射频集成电路向高性能、小型化的方向发展。

2、为克服上述问题,基于有源晶体管构成的有源电感,提供了一个很有前景的解决方案。相较于传统片上金属薄膜螺旋无源电感,有源电感具有很多优点,具体来说,有源电感面积小容易实现集成,以及由于晶体管的特性参数(例如跨导)是受电压控制,因而可通过调控外部控制电压(例如调制电压)改变晶体管特性参数的方式来对有源电感的电感值、q值等性能指标进行调节,进而可广泛应用于射频集成电路中来增强性能。

3、然而,现有有源电感的电路由于其电路结构相对简单,且各单元之间的相互配合不足,在高q值、高线性动态范围、独立调控性等方面的性能,还有较大的提升空间。

技术实现思路

1、针对现有技术中所存在的不足,本发明提供了一种有源电感,以提高有源电感的综合性功能。

2、本发明的目的是通过以下方案进行实现的:

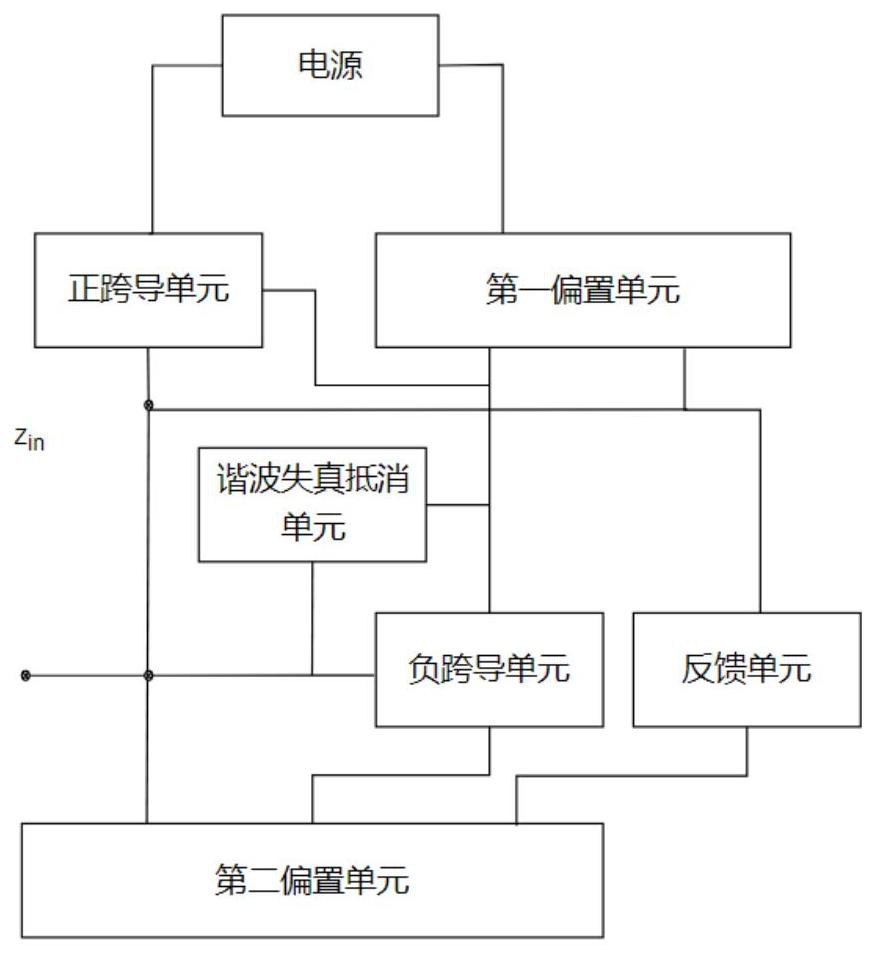

3、根据本发明实施例提供一种有源电感,所述有源电感至少包括负跨导单元、正跨导单元、第一偏置单元、第二偏置单元;其中,所述负跨导单元具有电源端、信号输入端和第一调制端,所述负跨导单元的电源端通过所述第一偏置单元连接至电源,并且所述负跨导单元的电源端还连接所述正跨导单元的信号输入端;所述负跨导单元和所述正跨导单元的接地端通过所述第二偏置单元接地;所述负跨导单元的信号输入端作为所述有源电感的输入端,且该输入端与所述正跨导单元的接地端连接,所述正跨导单元的电源端连接至电源。

4、在本发明的一些实施例中,所述有源电感还包括反馈单元,所述反馈单元的输入端通过所述第一偏置单元连接电源,所述反馈单元的接地端通过所述第二偏置单元接地,以及所述反馈单元的输入端与所述有源电感的输入端连接。

5、在本发明的一些实施例中,所述有源电感还包括谐波失真抵消单元,所述谐波失真抵消单元串联于所述负跨导单元的电源端与信号输入端之间。

6、在本发明的一些实施例中,所述正跨导单元包括第一n型mos晶体管,所述第一n型mos晶体管的漏极作为所述正跨导单元的电源端,源极作为所述正跨导单元的接地端,栅极作为所述正跨导单元的信号输入端;所述负跨导单元包括第三n型mos晶体管和第四n型mos晶体管,所述第四n型mos晶体管的漏极作为所述负跨导单元的电源端、栅极作为所述第一调制端,所述第四n型mos晶体管的源极与所述第三n型mos晶体管的漏极连接,所述第三n型mos晶体管的栅极作为所述负跨导单元的信号输入端;所述第一偏置单元至少包括第五p型mos晶体管和第一偏置端,所述第五p型mos晶体管的删极作为所述第一偏置端,所述第五p型mos晶体管源极连接至电源;所述第二偏置单元包括第二n型mos晶体管、第九n型mos晶体管和第二偏置端,所述第二n型mos晶体管和第九n型mos晶体管的栅极相连并作为所述第二偏置端,所述第二n型mos晶体管和第九n型mos晶体管的源极接地;其中,所述第二n型mos晶体管的漏极连接于所述第一n型mos晶体管源极;所述第九n型mos晶体管的漏极连接所述第三n型mos晶体管的源极;所述第四n型mos晶体管的漏极与所述第五p型mos晶体管的漏极连接,且与所述第一n型mos晶体管的栅极连接。

7、在本发明的一些实施例中,所述反馈单元包括第七n型mos晶体管、第八n型mos晶体管和第二调制端,所述第七n型mos晶体管和第八n型mos晶体管的栅极相连并作为所述第二调制端,所述第七n型mos晶体管的漏极作为所述反馈单元的输入端;所述第八n型mos晶体管的源极作为所述反馈单元的接地端;所述第一偏置还包括第六p型mos晶体管,所述第六p型mos晶体管的栅极与所述第五p型mos晶体管的删极相连,所述第六p型mos晶体管的源极连接至电源;所述第八n型mos晶体管的源极连接于所述第九n型mos晶体管的漏极,所述第七n型mos晶体管的漏极连接于所述第六p型mos晶体管的漏极,且连接于所述有源电感的输入端。

8、在本发明的一些实施例中,所述谐波失真抵消单元包括第十n型mos晶体管和第一无源电容;所述第一无源电容串联于所述第十n型mos晶体管的漏极和栅极之间,所述第十n型mos晶体管的漏极连接于所述第四n型mos晶体管的漏极,所述第十n型mos晶体管的源极连接于所述第三n型mos晶体管的栅极。

9、相比于现有技术,本发明具有如下有益效果:本发明实施例采用负跨导单元和正跨导单元构成其主体架构,实现电感的基本性能,其中,采用负跨导单元通过第二偏置单元接地,形成了浮地型负跨导单元,减小了有源电感的等效输入电容,进而提高了有源电感超宽工作频带。

10、此外,在输入端辅以反馈支路(也称反馈单元),减小了有源电感的等效串联电阻,从而还增大了q值;采用谐波失真抵消单元,可以进而稳定浮地型负跨导单元的跨导值,进而还提升有源电感的线性动态范围,以及本发明实施例中,再引入反馈单元、谐波失真抵消单元后,在q值、线性动态范围、超宽工作频带等方面性能均有提升。

技术特征:

1.一种有源电感,其特征在于,所述有源电感至少包括负跨导单元、正跨导单元、第一偏置单元、第二偏置单元;

2.根据权利要求1所述的有源电感,其特征在于,所述有源电感还包括反馈单元,所述反馈单元的输入端通过所述第一偏置单元连接电源,所述反馈单元的接地端通过所述第二偏置单元接地,以及所述反馈单元的输入端与所述有源电感的输入端(zin)连接。

3.根据权利要求1或2所述的有源电感,其特征在于,所述有源电感还包括谐波失真抵消单元,所述谐波失真抵消单元串联于所述负跨导单元的电源端与信号输入端之间。

4.根据权利要求3所述的有源电感,其特征在于,所述正跨导单元包括第一n型mos晶体管(m1),所述第一n型mos晶体管(m1)的漏极作为所述正跨导单元的电源端,源极作为所述正跨导单元的接地端,栅极作为所述正跨导单元的信号输入端;

5.根据权利要求4所述的有源电感,其特征在于,所述反馈单元包括第七n型mos晶体管(m7)、第八n型mos晶体管(m8)和第二调制端(vtune2),所述第七n型mos晶体管(m7)和第八n型mos晶体管(m8)的栅极相连并作为所述第二调制端(vtune2);所述第七n型mos晶体管(m7)的漏极作为所述反馈单元的输入端;所述第八n型mos晶体管(m8)的源极作为所述反馈单元的接地端;

6.根据权利要求5所述的有源电感,其特征在于,所述谐波失真抵消单元包括第十n型mos晶体管(m10)和第一无源电容(c1);所述第一无源电容(c1)串联于所述第十n型mos晶体管(m10)的漏极和栅极之间,所述第十n型mos晶体管(m10)的漏极连接于所述第四n型mos晶体管(m4)的漏极,所述第十n型mos晶体管(m10)的源极连接于所述第三n型mos晶体管(m3)的栅极。

技术总结

本发明一种有源电感,所述有源电感至少包括负跨导单元、正跨导单元、第一偏置单元、第二偏置单元;其中,所述负跨导单元的电源端通过所述第一偏置单元连接至电源,并且所述负跨导单元的电源端还连接所述正跨导单元的信号输入端;所述负跨导单元和所述正跨导单元的接地端通过所述第二偏置单元接地;所述负跨导单元的信号输入端作为所述有源电感的输入端,且该输入端与所述正跨导单元的接地端连接,所述正跨导单元的电源端连接至电源。本发明实施例采用负跨导单元和正跨导单元构成其主体架构,实现电感的基本性能,采用负跨导单元通过第二偏置单元接地,形成了浮地型负跨导单元,减小了电源电感的等效输入电容,进而提高了有源电感超宽工作频带。

技术研发人员:李白,王友华,董吉,万贤杰,徐茂加,罗永双,冉波,范佳淋

受保护的技术使用者:重庆吉芯科技有限公司

技术研发日:

技术公布日:2024/2/6

- 还没有人留言评论。精彩留言会获得点赞!