半导体结构的制备方法和半导体结构与流程

本发明涉及半导体,具体而言,涉及一种半导体结构的制备方法和半导体结构。

背景技术:

1、制造dram chip(dynamic random access memory,动态随机存取存储器)时,为了积累电荷进行cap(capacitance,电容)工程的话,cell领域和core,peri领域会发生相当大的高度断差。一般情况下,这种断差可能会导致后续的photo(曝光)在内的许多制程引发不良问题,所以为了消除这种断差差异,需要进行平坦化工艺。

2、常规的平坦化工艺,需要利用pr(光刻胶)图案化暴露cell领域后,利用dry etch(干法刻蚀)去除在电容上的一部分氧化膜质,并在后续进行cmp平坦化。但是,如果用这种一般的方法进行工程的话,图案化露出领域后部分区域进行刻蚀的loading现象会导致工程散波的不良,同时cmp时施加的压力会导致氧化膜质和柱状结构的破裂,很有可能发生后续不良情况。

技术实现思路

1、本发明的目的包括,例如,提供了一种半导体结构的制备方法和半导体结构,其能够实现氧化膜质的顺利平坦化,并且无需进行曝光显影以及研磨,简化了工艺,并能够防止结构破裂,安全可靠。

2、本发明的实施例可以这样实现:

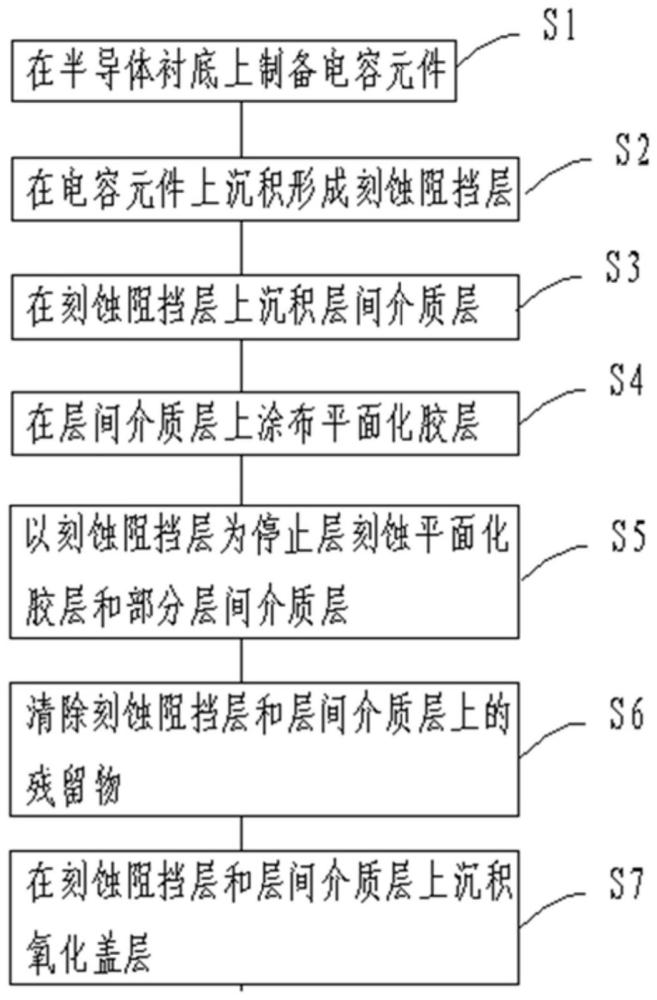

3、第一方面,本发明提供一种半导体结构的制备方法,包括:

4、在半导体衬底上制备电容元件;

5、在所述电容元件上沉积形成刻蚀阻挡层;

6、在所述刻蚀阻挡层上沉积层间介质层;

7、在所述层间介质层上涂布平面化胶层;

8、以刻蚀阻挡层为停止层刻蚀所述平面化胶层和部分所述层间介质层,并露出所述刻蚀阻挡层,以使所述刻蚀阻挡层和所述层间介质层实现平坦化。

9、在可选的实施方式中,在半导体衬底上制备电容元件的步骤,包括:

10、在半导体衬底上沉积sibn层;

11、在所述sibn层上形成电容元件;

12、在所述电容元件上形成tp层;

13、其中,所述tp层包覆所述电容元件,所述刻蚀阻挡层沉积在所述tp层的表面。

14、在可选的实施方式中,在所述电容元件上沉积形成刻蚀阻挡层的步骤,包括:

15、在所述tp层上通过化学气相沉积工艺形成刻蚀阻挡层;

16、其中,刻蚀阻挡层为sin层。

17、在可选的实施方式中,所述刻蚀阻挡层的厚度在100-200nm之间。

18、在可选的实施方式中,所述刻蚀阻挡层覆盖所述tp层和所述sibn层。

19、在可选的实施方式中,所述层间介质层的厚度在300-500nm之间。

20、在可选的实施方式中,以刻蚀阻挡层为停止层刻蚀所述平面化胶层和所述层间介质层至所述刻蚀阻挡层的步骤之后,所述制备方法还包括:

21、在所述刻蚀阻挡层和所述层间介质层上沉积氧化盖层。

22、在可选的实施方式中,以刻蚀阻挡层为停止层刻蚀所述平面化胶层和所述层间介质层至所述刻蚀阻挡层的步骤之后,所述制备方法还包括:

23、清除所述刻蚀阻挡层和所述层间介质层上的残留物。

24、在可选的实施方式中,在所述层间介质层上涂布平面化胶层的步骤,包括:

25、在所述层间介质层上均匀旋涂液态胶水;

26、在150℃-250℃之间烘烤所述胶水并固化后形成平面化的所述平面化胶层。

27、第二方面,本发明提供一种半导体结构,采用如前述实施方式任一项所述的半导体结构的制备方法制备而成,包括:

28、半导体衬底;

29、设置在所述半导体衬底上的电容元件;

30、设置在所述电容元件上的刻蚀阻挡层;

31、设置在所述刻蚀阻挡层上的层间介质层;

32、其中,所述层间介质层和所述刻蚀阻挡层平齐。

33、本发明实施例的有益效果包括,例如:

34、本发明实施例提供的半导体结构的制备方法和半导体结构,首先完成cap制程,在半导体衬底上制备电容元件,然后在电容元件上沉积形成刻蚀阻挡层,再在刻蚀阻挡层上沉积层间介质层,并在层间介质层上涂布平面化胶层消除层间介质层的高差,然后通过全面刻蚀的方式,以刻蚀阻挡层为停止层刻蚀平面化胶层和部分层间介质层,并露出刻蚀阻挡层,以使刻蚀阻挡层和层间介质层实现平坦化。相较于现有技术,本发明实施例提供的半导体结构的制备方法和半导体结构,能够实现氧化膜质的顺利平坦化,并且无需进行曝光显影以及研磨,简化了工艺,并能够防止结构破裂,安全可靠。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,在半导体衬底上制备电容元件的步骤,包括:

3.根据权利要求2所述的半导体结构的制备方法,其特征在于,在所述电容元件上沉积形成刻蚀阻挡层的步骤,包括:

4.根据权利要求3所述的半导体结构的制备方法,其特征在于,所述刻蚀阻挡层的厚度在100-200nm之间。

5.根据权利要求3所述的半导体结构的制备方法,其特征在于,所述刻蚀阻挡层覆盖所述tp层和所述sibn层。

6.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述层间介质层的厚度在300-500nm之间。

7.根据权利要求1所述的半导体结构的制备方法,其特征在于,以刻蚀阻挡层为停止层刻蚀所述平面化胶层和所述层间介质层至所述刻蚀阻挡层的步骤之后,所述制备方法还包括:

8.根据权利要求1所述的半导体结构的制备方法,其特征在于,以刻蚀阻挡层为停止层刻蚀所述平面化胶层和所述层间介质层至所述刻蚀阻挡层的步骤之后,所述制备方法还包括:

9.根据权利要求1所述的半导体结构的制备方法,其特征在于,在所述层间介质层上涂布平面化胶层的步骤,包括:

10.一种半导体结构,采用如权利要求1-9任一项所述的半导体结构的制备方法制备而成,其特征在于,包括:

技术总结

本发明的实施例提供了一种半导体结构的制备方法和半导体结构,涉及半导体技术领域,该制备方法首先完成Cap制程,在半导体衬底上制备电容元件,然后在电容元件上沉积形成刻蚀阻挡层,再在刻蚀阻挡层上沉积层间介质层,并在层间介质层上涂布平面化胶层消除层间介质层的高差,然后通过全面刻蚀的方式,以刻蚀阻挡层为停止层刻蚀平面化胶层和部分层间介质层,并露出刻蚀阻挡层,以使刻蚀阻挡层和层间介质层实现平坦化。相较于现有技术,本发明实施例提供的半导体结构的制备方法和半导体结构,能够实现氧化膜质的顺利平坦化,并且无需进行曝光显影以及研磨,简化了工艺,并能够防止结构破裂,安全可靠。

技术研发人员:裴俊植

受保护的技术使用者:成都高真科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!