一种基于FPGA的LZ4压缩与解压缩系统与介质的制作方法

本发明涉及数据实时压缩与解压缩领域,具体涉及一种基于fpga的lz4压缩与解压缩系统与介质。

背景技术:

1、由于现代信息技术的巨大进步,需要处理的数据量迅速增加。这给信息的存储和传输都带来了巨大的压力。于是,各种数据压缩的算法就被提了出来。数据压缩可以分为有损压缩和无损压缩。有损压缩本身会破坏原始数据,常用在图像压缩等多媒体应用领域。而无损压缩算法已经发展了数十年,根据重复字符被替换的具体方法不同,无损压缩可以分为字典类、统计类和预测类三种。其中,1977年提出的lz77算法是目前使用最多的字典类压缩算法。本发明所实现的lz4算法是lz77算法的一种提升,其优势在于其极快的压缩与解压缩速度,适用对实时性要求较高的系统。lz4压缩作为一种通过检索原始数据中的匹配项,用匹配数据代替匹配项的方式实现数据压缩的算法,其核心的去冗余方法可以化简为一系列的查字典、匹配、替换操作。

2、然而,现有的lz4压缩算法对硬件实现并不友好,当前亟需一种不仅在功能上能够保证支持lz4算法,还要在性能上拥有较高吞吐量的、易于在fpga上进行实现的压缩与解压缩系统。

技术实现思路

1、有鉴于此,本发明提供了一种基于fpga的lz4压缩与解压缩系统与介质,能够提升lz4算法在fpga硬件平台的可实现性。

2、为了解决上述技术问题,本发明是这样实现的:

3、一种基于fpga的lz4压缩与解压缩系统,包括:编码器单元和解码器单元;

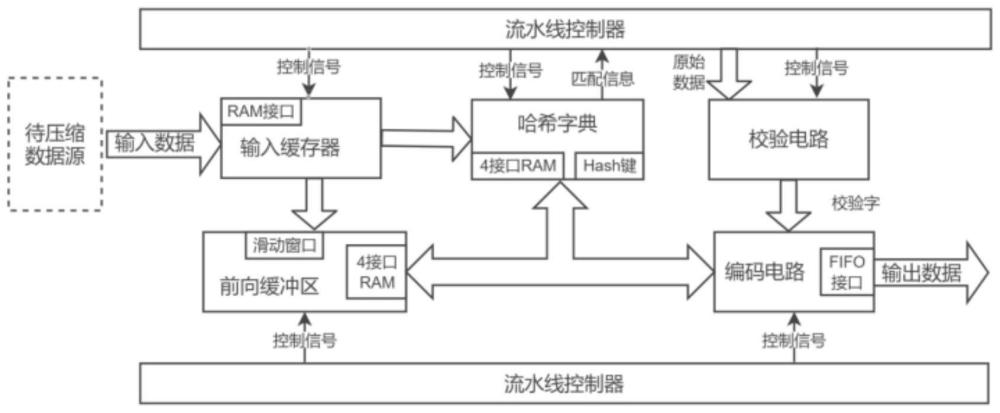

4、所述编码器单元,包括:输入缓存器、前向缓冲区、哈希字典和编码电路;

5、所述输入缓存器,分组缓存待压缩数据,得到分组后字符串数据;

6、所述前向缓冲区,对所述分组后字符串数据进行滑动窗口遍历,得到遍历数据;

7、所述哈希字典,判断所述遍历数据是首次出现的字符串还是重复字符串,将首次出现的字符串作为非匹配项存入字典并得到非匹配项信息,将重复字符串作为匹配项得到匹配项信息;

8、所述编码电路,根据设定的压缩数据帧格式将所述非匹配项信息和所述匹配项信息输出为压缩数据帧;

9、所述解码器单元,根据所述压缩数据帧格式对所述压缩数据帧进行解码,得到解压后的还原数据。

10、较佳地,所述哈希字典将首次出现的字符串作为非匹配项存入字典时,通过哈希函数得到首次出现的字符串的哈希键,以所述哈希键为非匹配项的存储地址;所述哈希字典将首次出现的字符串和对应的所述存储地址组成数据对一并存入字典。

11、较佳地,所述哈希字典,包括ram模块;所述ram模块通过端口复用得到多个虚拟端口以多路接收所述遍历数据。

12、较佳地,所述哈希字典得到匹配项信息,所述匹配项信息包括:匹配长度、偏移地址和匹配标志位。

13、较佳地,所述前向缓冲区,通过滑动窗口以设定的移动步长的对所述分组后字符串数据进行滑动遍历选取,得到所述遍历数据,相邻的每组所述遍历数据间存在一个所述设定的移动步长的偏移;各组所述遍历数据通过流水线机制并行地传输至所述哈希字典。

14、较佳地,所述前向缓冲区,采用环形队列的数据结构。

15、较佳地,所述编码电路将所述非匹配项信息和所述匹配项信息输出为压缩数据帧时,当非匹配项长度超出所述压缩数据帧格式的表达上限时,向所述压缩数据帧中添加非匹配项附加字节以表示非匹配项长度的超出部分;当匹配项长度超出所述压缩数据帧格式的表达上限时,向所述压缩数据帧中添加匹配项附加字节以表示匹配项长度的超出部分。

16、较佳地,所述编码器单元,进一步包括校验电路和流水线控制器;

17、所述校验电路,根据待压缩数据得到校验字以对所述编码电路的输出信息进行文件完整性校验;所述文件完整性校验正确的数据才能作为所述压缩数据帧输出,否则所述校验电路向所述流水线控制器报错;

18、所述流水线控制器,控制所述输入缓存器、所述前向缓冲区、所述哈希字典、所述编码电路和所述校验电路的工作。

19、较佳地,所述解码器单元进行解码,为:

20、所述解码器单元接收压缩数据帧,根据所述压缩数据帧格式对压缩数据帧中的压缩信息进行识别;通过状态机的跳转对所述压缩信息进行解码,并将全部压缩数据帧的解码结果进行拼接,得到解压后的还原数据;

21、所述压缩信息,包括:非匹配项长度、非匹配项数据、匹配长度和匹配偏移量。

22、一种基于fpga的lz4压缩与解压缩计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,所述计算机程序被执行时实现所述的系统。

23、有益效果:

24、1、本发明通过编码器单元中的各子单元的结构和功能设计,使其中每个子单元的功能实现与fpga硬件平台所能支撑的动作相互吻合,且各模块所调用的功能和占用的资源有序合理,所实现的算法逻辑清晰简单,从而在保证lz4算法实现的前提下,提升了整个系统对fpga硬件平台的可实现性,同时也提升了压缩任务的处理速度。进而通过对fpga的有效利用,减少cpu的计算负载,降低了cpu的处理压力和功耗,提升了设备整体的运行速度。

25、2、本发明针对非匹配项通过哈希函数生成字符串的哈希键,并将该哈希键作为非匹配项的存储地址,能够在识别重复字符串时通过哈希键的相同映射实现匹配项的快速查找,大幅提升压缩作业中识别环节的效率。

26、3、本发明通过将哈希字典中的ram通过端口复用的方式虚拟出更多接口的设计,进一步提升了系统的数据吞吐量,提升了系统的压缩效率。

27、4、本发明通过将滑动窗口得到的遍历数据通过流水线机制并行地传输至哈希字典,减少了可靠通信中的等待时间对系统处理速度的延迟,实现了压缩系统更高的处理速度。

28、5、本发明采用环形队列作为输入缓冲区的指针处理方式,进一步提高了系统吞吐量,提升了系统运行的稳定性。

29、6、本发明通过对压缩数据帧格式的设计,通过非匹配项附加字节和匹配项附加字节对压缩后的压缩数据帧长度进行了最大幅度的简化,提升了lz4文件压缩系统的压缩效果和效率。

30、7、本发明通过编码器单元中校验电路和流水线控制器的设计,进一步提升了lz4压缩系统的运行稳定性和压缩作业准确性,降低了文件错误压缩问题的出现机率。

技术特征:

1.一种基于fpga的lz4压缩与解压缩系统,其特征在于,包括:编码器单元和解码器单元;

2.如权利要求1所述的基于fpga的lz4压缩与解压缩系统,其特征在于,所述哈希字典将首次出现的字符串作为非匹配项存入字典时,通过哈希函数得到首次出现的字符串的哈希键,以所述哈希键为非匹配项的存储地址;所述哈希字典将首次出现的字符串和对应的所述存储地址组成数据对一并存入字典。

3.如权利要求1或2所述的基于fpga的lz4压缩与解压缩系统,其特征在于,所述哈希字典,包括ram模块;所述ram模块通过端口复用得到多个虚拟端口以多路接收所述遍历数据。

4.如权利要求1或2所述的基于fpga的lz4压缩与解压缩系统,其特征在于,所述哈希字典得到匹配项信息,所述匹配项信息包括:匹配长度、偏移地址和匹配标志位。

5.如权利要求1或2所述的基于fpga的lz4压缩与解压缩系统,其特征在于,所述前向缓冲区,通过滑动窗口以设定的移动步长的对所述分组后字符串数据进行滑动遍历选取,得到所述遍历数据,相邻的每组所述遍历数据间存在一个所述设定的移动步长的偏移;各组所述遍历数据通过流水线机制并行地传输至所述哈希字典。

6.如权利要求1或2所述的基于fpga的lz4压缩与解压缩系统,其特征在于,所述前向缓冲区,采用环形队列的数据结构。

7.如权利要求1或2所述的基于fpga的lz4压缩与解压缩系统,其特征在于,所述编码电路将所述非匹配项信息和所述匹配项信息输出为压缩数据帧时,当非匹配项长度超出所述压缩数据帧格式的表达上限时,向所述压缩数据帧中添加非匹配项附加字节以表示非匹配项长度的超出部分;当匹配项长度超出所述压缩数据帧格式的表达上限时,向所述压缩数据帧中添加匹配项附加字节以表示匹配项长度的超出部分。

8.如权利要求1或2所述的基于fpga的lz4压缩与解压缩系统,其特征在于,所述编码器单元,进一步包括校验电路和流水线控制器;

9.如权利要求1或2所述的基于fpga的lz4压缩与解压缩系统,其特征在于,所述解码器单元进行解码,为:

10.一种基于fpga的lz4压缩与解压缩计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机程序,所述计算机程序被执行时实现权利要求1-9中任意一项所述的系统。

技术总结

本发明公开了一种基于FPGA的LZ4压缩与解压缩系统与介质,包括:编码器单元和解码器单元;编码器单元,包括:输入缓存器、前向缓冲区、哈希字典和编码电路;输入缓存器,分组缓存待压缩的原始数据;前向缓冲区,对分组后字符串数据进行滑动窗口遍历;哈希字典,判断遍历数据是首次出现的字符串还是重复字符串,将首次出现的字符串作为非匹配项存入字典并得到非匹配项信息,将重复字符串作为匹配项得到匹配项信息;编码电路,根据设定的压缩数据帧格式将非匹配项信息和匹配项信息输出为压缩数据帧;解码器单元,根据压缩数据帧格式对压缩数据帧进行解码,得到解压后的还原数据;使用本发明能够提升LZ4算法在FPGA硬件平台的可实现性。

技术研发人员:冷文韬,孟繁毅

受保护的技术使用者:中科驭数(北京)科技有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!