失效延缓电路

本公开涉及集成电路领域,并且更具体地,涉及一种失效延缓电路。

背景技术:

1、集成芯片电路,如可编程逻辑器件、单片机、微处理器、数字信号处理器等,由众多逻辑器件组成,而逻辑器件,如锁存器、触发器、定时器、寄存器、计数器等,由基本逻辑门电路和组合逻辑门电路组成。目前,基本逻辑门电路和组合逻辑门电路通常由制造结构简单,功耗低的互补式金属氧化物半导体(complementary metal-oxide-semiconductor,cmos)逻辑门电路构成。cmos逻辑门电路是指同时使用nmos管和pmos管的电路。

2、逻辑门电路一般可以由p型金属-氧化物-半导体场效晶体管(p-type metal-oxide-semiconductor field-effect transistor,pmos管)以及n型金属-氧化物-半导体场效晶体管(n-type metal-oxide-semiconductor field-effect transistor,nmos晶体管)以对称互补的形式组成。

3、众所周知,mos晶体管的基本结构为:在掺杂的单晶硅上生成一层sio2绝缘层,然后用光刻工艺扩散两个高掺杂区,从高掺杂区引出电极(漏极d、源极s);在源极s和漏极d之间的sio2绝缘层上镀一层金属层作为栅极g;掺杂的单晶硅称为衬底,用符号b表示。

4、当mos晶体管开始工作时,需要对pmos晶体管的栅极施加负偏置电压或对nmos晶体管的栅极施加正偏置电压以在漏极d和源极s之间形成导电沟道,这个阶段可称为受压阶段。在受压阶段,si/sio2界面处作用力较弱的si-h键会发生断裂,失去氢原子的硅原子成为沟道中载流子的俘获中心,从而引起si/sio2界面处电荷的增加,这导致了负偏置温度不稳定性(negative bias temperature instability,nbti)效应或正偏置温度不稳定性(positive bias temperature instability,pbti)效应的产生,进而引起mos晶体管的性能的逐渐退化甚至失效。另外,由于sio2或高介电常数的材料(high k材料)中存在一些缺陷从而形成俘获中心,在mos晶体管导通时俘获中心会俘获电荷,从而引起nbti效应或pbti效应。

5、为了降低nbti效应和pbti效应对mos晶体管性能的影响,传统做法一是通过改进工艺以引入其他可以与si形成更高键能的元素来替代h,比如氘或氟(f),或者改善sio2绝缘层的材料,以减少sio2绝缘层材料的缺陷或杂质等,但是这种工艺上的改善存在极限,并不能消除nbti效应和pbti效应;二是通过断开逻辑门电路在待机状态下的电源以减少mos晶体管的导通时间,但是这种做法也会导致从待机状态进入工作状态的等待时间会较长,从而影响器件的性能。

技术实现思路

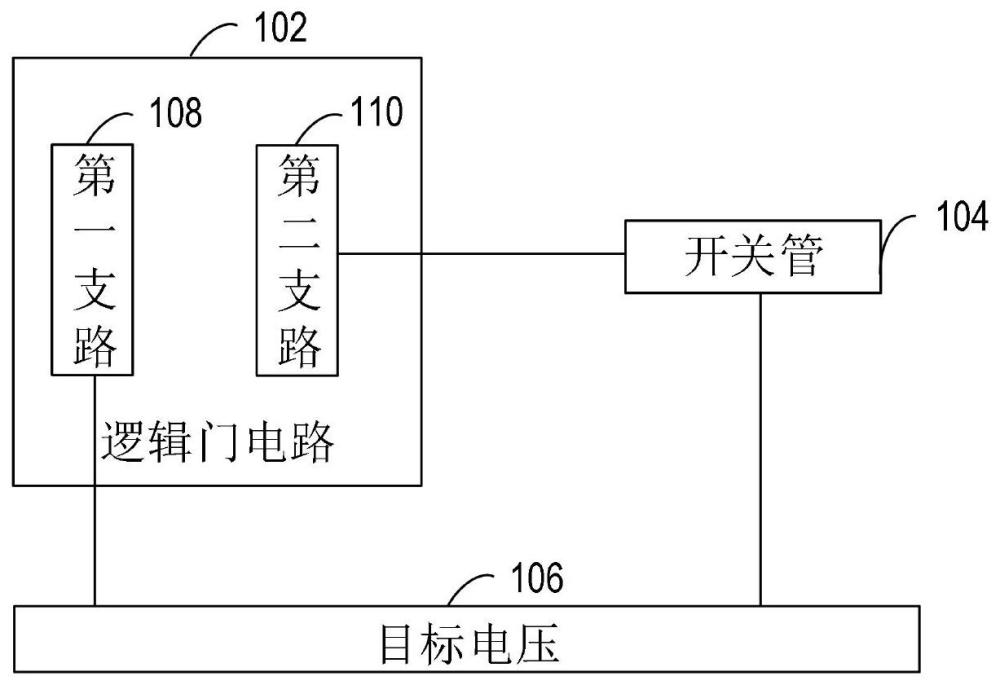

1、本公开的实施例涉及一种降低偏置温度不稳定性效应的电路,该电路包括至少一个逻辑门电路和至少一个开关管,逻辑门电路包括并联连接的第一支路和第二支路。第一支路与目标电压连接,第二支路通过开关管与目标电压连接,开关管被配置为在芯片处于待机状态时断开,处于工作状态时导通。目标电压的类型与第一支路和第二支路的类型相匹配,第一支路和第二支路在芯片处于工作状态时的输出状态与目标电压相关联。通过这种方式,利用开关管可以使得在芯片进入待机状态时第一支路导通而第二支路断开。这样,可以在保证逻辑输出的同时降低pbti效应和/或nbti效应对电路性能的影响。此外,这种方式保证了芯片进入工作状态时、退出工作状态时、及处于待机状态时,每个逻辑门电路的逻辑输出是相一致的,从而无需在状态切换时再转换每个逻辑门电路的逻辑输出,进而没有额外增加芯片进行状态切换所需的时间。

2、应当理解,

技术实现要素:

部分中所描述的内容并非旨在限定本公开的实施例的关键或重要特征,亦非用于限制本公开的范围。本公开的其他特征将通过以下的描述变得容易理解。

技术特征:

1.一种失效延缓电路,应用于芯片,其特征在于,所述失效延缓电路包括至少一个第一逻辑门电路、第一开关管、至少一个第二逻辑门电路、及第二开关管;其中,每个第一逻辑门电路均包括并联连接的第一支路和第二支路,所述第一支路与第一电源电压连接,所述第二支路通过所述第一开关管与所述第一电源电压连接,所述第一支路和所述第二支路均由pmos管构成;其中,所述第一开关管被配置为在所述芯片处于待机状态时断开,处于工作状态时导通;所述第一支路和所述第二支路被配置为在所述芯片处于所述工作状态时均输出高电平;每个第二逻辑门电路均包括并联连接的第三支路和第四支路,所述第三支路与第一接地电压连接,所述第四支路通过所述第二开关管与所述第一接地电压连接,所述第三支路和所述第四支路均由nmos管构成;其中,所述第二开关管被配置为在所述芯片处于待机状态时断开,处于工作状态时导通;所述第三支路和所述第四支路被配置为在所述芯片处于所述工作状态时均输出低电平。

2.根据权利要求1所述的失效延缓电路,其特征在于,当所述芯片的输入引脚上的信号处于预设电平或者所述芯片接收到外界所发送的待机命令时,所述芯片进入所述待机状态并控制所述第一开关管和所述第二开关管断开。

3.根据权利要求1所述的失效延缓电路,其特征在于,所述第一支路的导通电流小于所述第二支路的导通电流,所述第三支路的导通电流小于所述第四支路的导通电流。

4.根据权利要求1所述的失效延缓电路,其特征在于,所述第一支路包括一个pmos管或串联连接的多个pmos管;所述第二支路包括一个pmos管或串联连接的多个pmos管;所述第三支路包括一个nmos管或串联连接的多个nmos管;所述第四支路包括一个nmos管或串联连接的多个nmos管。

5.根据权利要求1所述的失效延缓电路,其特征在于,所述第一支路中的pmos管在进行版图设计时被设计为并联的多组pmos管单元时,选择其中的一组或几组pmos管单元与所述第一电源电压连接;所述第三支路中的nmos管在进行版图设计时被设计为并联的多组nmos管单元时,选择其中的一组或几组nmos管单元与所述第一接地电压连接。

6.根据权利要求1所述的失效延缓电路,其特征在于,所述第一支路包括第一pmos管,所述第二支路包括第二pmos管,其中,所述第一pmos管的第一端连接所述第一电源电压,所述第二pmos管的第一端通过所述第一开关管连接所述第一电源电压,所述第一pmos管的第二端连接所述第二pmos管的第二端;在所述芯片处于所述工作状态时,所述第一pmos管和所述第二pmos管均导通。

7.根据权利要求7所述的失效延缓电路,其特征在于,所述第一pmos管的宽长比小于所述第二pmos管的宽长比和/或所述第一pmos管的氧化层厚度大于所述第二pmos管的氧化层厚度。

8.根据权利要求1所述的失效延缓电路,其特征在于,所述第三支路包括第一nmos管,所述第四支路包括第二nmos管,其中,所述第一nmos管的第一端连接所述第二nmos管的第一端,所述第一nmos管的第二端连接所述第一接地电压,所述第二nmos管的第二端通过所述第二开关管连接所述第一接地电压;在所述芯片处于所述工作状态时,所述第一nmos管和所述第二nmos管均导通。

9.根据权利要求10所述的失效延缓电路,其特征在于,所述第一nmos管的宽长比小于所述第二nmos管的宽长比和/或所述第一nmos管的氧化层厚度大于所述第二nmos管的氧化层厚度。

10.根据权利要求1所述的失效延缓电路,其特征在于,所述第一开关管为第三pmos管;所述芯片进入所述待机状态时产生处于高电平的第一控制信号,以控制所述第三pmos管截止,进入所述工作状态时产生处于低电平的第一控制信号,以控制所述第三pmos管导通。

11.根据权利要求1所述的失效延缓电路,其特征在于,所述第二开关管为第三nmos管;所述芯片进入所述待机状态时产生处于低电平的第二控制信号,以控制所述第三nmos管截止,进入所述工作状态时产生处于高电平的第二控制信号,以控制所述第三nmos管导通。

技术总结

本申请是申请号为2023114149383的分案申请。本公开涉及失效延缓电路,应用于芯片,包括至少一个逻辑门电路和至少一个开关管,逻辑门电路包括并联连接的第一支路和第二支路。其中,第一支路与目标电压连接,第二支路通过开关管与目标电压连接。开关管被配置为在芯片处于待机状态时断开,处于工作状态时导通。目标电压的类型与第一支路和第二支路的类型相匹配,第一支路和第二支路在芯片处于工作状态时的输出状态与目标电压相关联。通过这种方式,利用开关管可以使得在芯片进入待机状态时第一支路导通而第二支路断开。这样,可以在保证逻辑输出的同时降低PBTI效应和/或NBTI效应对电路性能的影响。

技术研发人员:殷宁淳

受保护的技术使用者:河南省科学院集成电路研究所

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!