低噪声放大器及射频前端模组的制作方法

本申请涉及通信,尤其涉及一种低噪声放大器及射频前端模组。

背景技术:

1、在无线通信、雷达等射频微波系统中,低噪声放大器(low noise amplifier,lna)被广泛应用于各种接收链路中,用于对微弱信号进行放大。通常lna的输入端设置有输入匹配电路,以匹配lna的输入阻抗与前级电路的输出阻抗。当lna的输入端对应的输入信号的频段不同时,需要的输入匹配电感值不同。

2、对于宽频lna,为了处理至少两个频段的输入信号,通常设有多个输入端,其中,每个输入端可以传输一个频段的输入信号。相关技术中,在输入匹配电路的每个输入端后面各设置一组和该输入端的信号频段相匹配的输入匹配电感,n个输入端就需要对应设置n个输入匹配电感,且每个输入匹配电感的电感值都比较大,使得lna整体占用的面积较多。

技术实现思路

1、基于此,本申请实施例提供了一种低噪声放大器及射频前端模组。

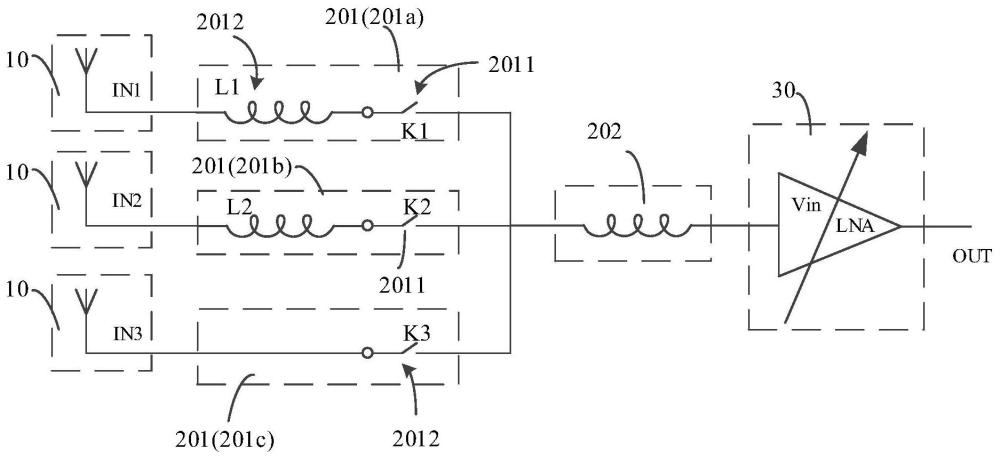

2、第一方面,本申请实施例提供了一种低噪声放大器,包括:至少两个信号输入端口、输入匹配电路及放大电路,放大电路的输入端与匹配电路的输出端连接,且被配置为接收经匹配电路输出的射频输入信号,并输出射频输出信号;

3、输入匹配电路包括匹配电感和至少两个匹配支路,每个匹配支路对应连接于一个信号输入端口,其中,每个匹配支路均包括支路开关,并且至少部分匹配支路还包括支路电感;

4、支路电感的第一端与对应匹配支路的信号输入端口连接,支路电感的第二端与对应匹配支路的支路开关的第一端连接,支路开关的第二端与匹配电感的第一端连接,匹配电感的第二端与放大电路的输入端连接。

5、在一些实施方式中,匹配电感的电感值大于至少部分匹配支路中支路电感的电感值。

6、在一些实施方式中,匹配电感的电感值大于或等于5nh;支路电感的电感值小于或等于7nh。

7、在一些实施方式中,至少两个匹配支路包括第一匹配支路和第二匹配支路;其中,第一匹配支路包括第一支路电感和第一支路开关,第一支路电感的第一端与第一匹配支路对应的信号输入端口连接,第一支路电感的第二端与第一支路开关的第一端连接,第一支路开关的第二端与匹配电感的第一端连接,匹配电感的第二端与放大电路的输入端连接;

8、第二匹配支路包括第二支路电感和第二支路开关,第二支路电感的第二端与第二匹配支路对应的信号输入端口连接,第二支路电感的第二端与第二支路开关的第一端连接,第二支路开关的第二端与匹配电感的第一端连接。

9、在一些实施方式中,至少两个匹配支路包括第一匹配支路和第二匹配支路;其中,第一匹配支路包括第一支路电感和第一支路开关,第一支路电感的第一端与第一匹配支路对应的信号输入端口连接,第一支路电感的第二端与第一支路开关的第一端连接,第一支路开关的第二端与匹配电感的第一端连接,匹配电感的第二端与放大电路连接;

10、第二匹配支路包括第二支路开关,第二支路开关的第一端与第二匹配支路对应的信号输入端口连接,第二支路开关的第二端与匹配电感的第一端连接。

11、在一些实施方式中,匹配电感和放大电路分别设置于不同的承载件,承载件包括基板和芯片。

12、在一些实施方式中,放大电路和至少一个匹配支路对应的支路开关集成于同一芯片;匹配电感设置于基板,匹配电感通过smd元件实现,或者通过设置于基板表面的传输线实现。

13、在一些实施方式中,支路电感设置于基板,支路电感通过smd元件实现,或者通过设置于基板表面的传输线实现;或者,支路电感集成于芯片。

14、在一些实施方式中,匹配电感通过设置于基板表面的传输线实现,并且至少部分的支路电感为贴装于基板表面的smd元件。

15、在一些实施方式中,当匹配支路对应的射频输入信号的频率高于2.4ghz时,匹配支路对应的支路电感的电感值小于1nh;并且支路电感集成于芯片或者通过设置于基板表面的传输线实现。

16、第二方面,本申请实施例提供了一种射频前端模组,所述射频前端模组至少包括前述低噪声放大器。

17、在一些实施方式中,射频前端模组还包括基板和芯片,低噪声放大器的放大电路设置于芯片,匹配电感设置于基板。

18、从上述技术方案可以看出,本申请所提供的低噪声放大器通过为多个匹配支路设置共用的匹配电感,从而无需为每个匹配支路对应设置一个独立的匹配电感,从而有效节省了低噪声放大器的占用面积,实现低噪声放大器的小型化。

19、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。

技术特征:

1.一种低噪声放大器,其特征在于,包括:至少两个信号输入端口、输入匹配电路及放大电路,所述放大电路的输入端与所述匹配电路的输出端连接,且被配置为接收经所述匹配电路输出的射频输入信号,并输出射频输出信号;

2.根据权利要求1所述的低噪声放大器,其特征在于,所述匹配电感的电感值大于至少部分所述匹配支路中所述支路电感的电感值。

3.根据权利要求2所述的低噪声放大器,其特征在于,所述匹配电感的电感值大于或等于5nh;所述支路电感的电感值小于或等于7nh。

4.根据权利要求1所述的低噪声放大器,其特征在于,至少两个匹配支路包括第一匹配支路和第二匹配支路;其中,所述第一匹配支路包括第一支路电感和第一支路开关,所述第一支路电感的第一端与所述第一匹配支路对应的所述信号输入端口连接,所述第一支路电感的第二端与所述第一支路开关的第一端连接,所述第一支路开关的第二端与所述匹配电感的第一端连接,所述匹配电感的第二端与所述放大电路的输入端连接;

5.根据权利要求1所述的低噪声放大器,其特征在于,至少两个匹配支路包括第一匹配支路和第二匹配支路;其中,所述第一匹配支路包括第一支路电感和第一支路开关,所述第一支路电感的第一端与所述第一匹配支路对应的所述信号输入端口连接,所述第一支路电感的第二端与所述第一支路开关的第一端连接,所述第一支路开关的第二端与所述匹配电感的第一端连接,所述匹配电感的第二端与所述放大电路连接;

6.根据权利要求1所述的低噪声放大器,其特征在于,所述匹配电感和所述放大电路分别设置于不同的承载件,所述承载件包括基板和芯片。

7.根据权利要求6所述的低噪声放大器,其特征在于,所述放大电路和至少一个所述匹配支路对应的所述支路开关集成于同一所述芯片;所述匹配电感设置于所述基板,所述匹配电感通过smd元件实现,或者通过设置于所述基板表面的传输线实现。

8.根据权利要求7所述的低噪声放大器,其特征在于,所述支路电感设置于所述基板,所述支路电感通过smd元件实现,或者通过设置于所述基板表面的传输线实现。

9.根据权利要求7所述的低噪声放大器,其特征在于,所述支路电感集成于所述芯片。

10.根据权利要求9所述的低噪声放大器,其特征在于,所述匹配电感通过设置于所述基板表面的传输线实现,并且至少部分的所述支路电感为贴装于所述基板表面的smd元件。

11.根据权利要求1-10任一项所述的低噪声放大器,其特征在于,当所述匹配支路对应的射频输入信号的频率高于2.4ghz时,所述匹配支路对应的所述支路电感的电感值小于1nh;并且所述支路电感集成于所述芯片或者通过设置于所述基板表面的传输线实现。

12.一种射频前端模组,其特征在于,所述射频前端模组至少包括如权利要求1-11任一项所述的低噪声放大器。

13.根据权利要求12所述的射频前端模组,其特征在于,所述射频前端模组还包括基板和芯片,所述低噪声放大器的放大电路设置于所述芯片,所述匹配电感设置于所述基板。

技术总结

本申请公开了一种低噪声放大器及射频前端模组,其中,低噪声放大器包括:至少两个信号输入端口、输入匹配电路及放大电路,放大电路的输入端与匹配电路的输出端连接;输入匹配电路包括匹配电感和至少两个匹配支路,每个匹配支路对应连接于一个信号输入端口,每个匹配支路均包括支路开关,并且至少部分匹配支路还包括支路电感;支路电感的第一端与对应匹配支路的信号输入端口连接,支路电感的第二端与对应匹配支路的支路开关的第一端连接,支路开关的第二端与匹配电感的第一端连接,匹配电感的第二端与放大电路的输入端连接。本申请可以有效减小低噪声放大器的占用面积,实现低噪声放大器的小型化。

技术研发人员:李镁钰,宋楠,吴昊,倪建兴

受保护的技术使用者:锐石创芯(深圳)科技股份有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!