一种半导体器件的制作方法

本技术属于半导体器,特别是关于一种具有垂直通道结构的半导体器件。

背景技术:

1、透过改善工艺技术、电路设计、程序设计算法和制作方法可使平面式的半导体器件缩至更小的尺寸。然而,随着半导体器件的特征尺寸逐渐接近下限,相关器件的制作方法变得极富挑战性并且高成本。现今,平面式半导体器件的发展已达瓶颈,为能解决上述平面式半导体器件的密度极限问题,具有立体结构的半导体器件已成为目前的主流发展趋势,诸如三维nand等半导体存储器件及相关制作工艺不断地改良,以在制作工艺简化的前提下维持良好的器件效能。

技术实现思路

1、为达上述目的,本实用新型之一实施例提供一种半导体器件。

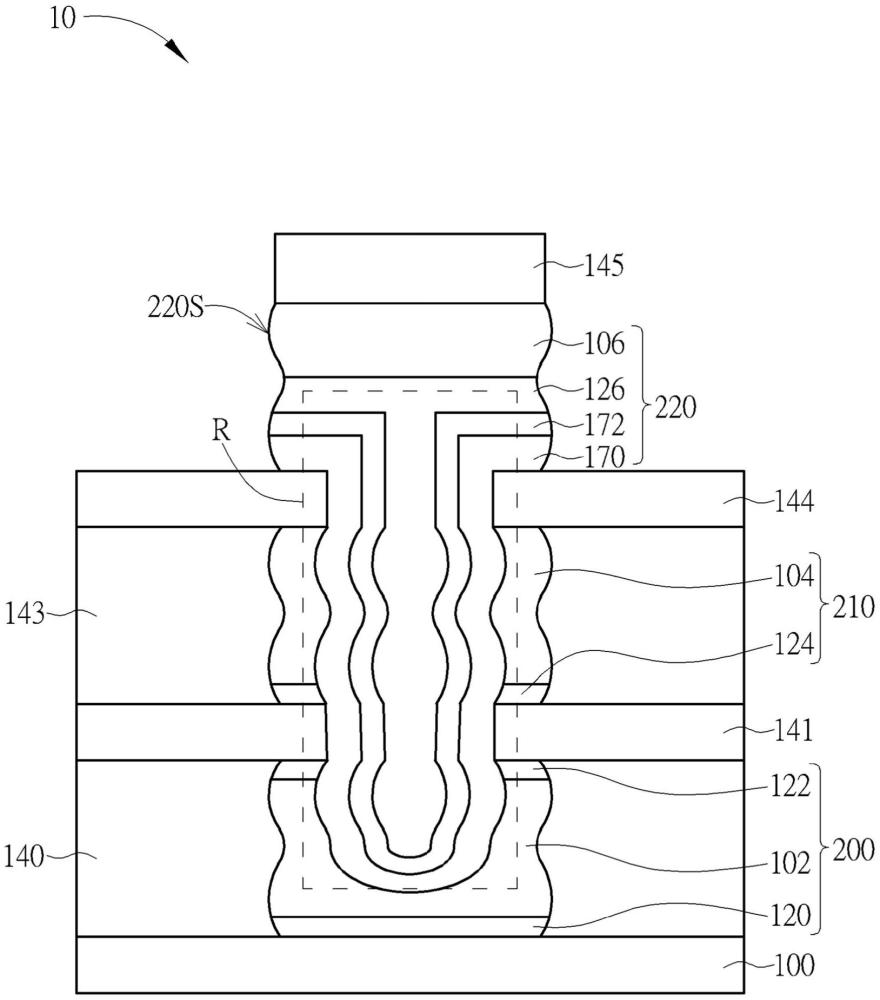

2、第一方面,本实用新型提供一种半导体器件,包括衬底、第一衬垫层、第二衬垫层及连接层。所述第一衬垫层与所述第二衬垫层在垂直方向上堆叠设置在所述衬底上。所述连接层的至少部分设置在所述第一衬垫层与所述第二衬垫层之间,其中,所述第一衬垫层、所述第二衬垫层、与所述连接层中至少一个具有波浪形侧壁。

3、可选的,所述连接层包括在水平方向上依序堆叠的通道层与电介质层,其中,所述通道层电性连接所述第一衬垫层与所述第二衬垫层,并具有波浪形侧壁。

4、可选的,所述电介质层也具有波浪形侧壁。

5、可选的,所述波浪形侧壁包括多个凹部与多个端部,相邻的所述凹部与所述端部在水平方向上具有阶梯差。

6、可选的,各所述阶梯差彼此相同。

7、可选的,各所述阶梯差在所述垂直方向上由下而上逐渐增大。

8、可选的,所述通道层的厚度大于所述波浪形侧壁上的所述阶梯差。

9、可选的,所述半导体器件,还包括:

10、阻隔层,在所述水平方向上设置在所述连接层与所述第一衬垫层或第二衬垫层之间,其中,所述阻隔层具有波浪形侧壁,且所述阻隔层的厚度大于所述通道层上的所述阶梯差。

11、可选的,所述阻隔层包括金属氮化物层或金属氧化物层。

12、可选的,所述半导体器件,还包括:

13、第一绝缘层;以及第二绝缘层,所述第一绝缘层与所述第二绝缘层依序设置在所述第一衬垫层、所述第二衬垫层与所述连接层之间。

14、可选的,所述连接层包括在水平方向上依序堆叠的电介质层与通道层,所述通道层电性连接所述第一衬垫层与所述第二衬垫层,并在垂直方向上位在所述第一衬垫层与所述第二衬垫层之间,所述通道层具有波浪形侧壁。

15、有益效果:

16、本实用新型提供一种半导体器件,系在源极、漏极及通道层中至少一者上设有波浪形侧壁,以在相同的占地面积下有效地增加半导体器件的载子通道宽度,优化电子传输信号的可靠性并降低漏电流发生。

技术特征:

1.一种半导体器件,其特征是,包括:

2.根据权利要求1所述的半导体器件,其特征是,所述连接层包括在水平方向上依序堆叠的通道层与电介质层,其中,所述通道层电性连接所述第一衬垫层与所述第二衬垫层,并具有波浪形侧壁。

3.根据权利要求2所述的半导体器件,其特征是,所述电介质层也具有波浪形侧壁。

4.根据权利要求2所述的半导体器件,其特征是,所述波浪形侧壁包括多个凹部与多个端部,相邻的所述凹部与所述端部在水平方向上具有阶梯差。

5.根据权利要求4所述的半导体器件,其特征是,各所述阶梯差彼此相同。

6.根据权利要求4所述的半导体器件,其特征是,各所述阶梯差在所述垂直方向上由下而上逐渐增大。

7.根据权利要求4所述的半导体器件,其特征是,所述通道层的厚度大于所述波浪形侧壁上的所述阶梯差。

8.根据权利要求4所述的半导体器件,其特征是,还包括:

9.根据权利要求8所述的半导体器件,其特征是,所述阻隔层包括金属氮化物层或金属氧化物层。

10.根据权利要求2所述的半导体器件,其特征是,还包括:

11.根据权利要求1所述的半导体器件,其特征是,所述连接层包括在水平方向上依序堆叠的电介质层与通道层,所述通道层电性连接所述第一衬垫层与所述第二衬垫层,并在垂直方向上位在所述第一衬垫层与所述第二衬垫层之间,所述通道层具有波浪形侧壁。

技术总结

本技术公开了一种半导体器件,属于半导体器技术领域,所述半导体器件包括衬底、第一衬垫层、第二衬垫层及连接层。第一衬垫层与第二衬垫层在垂直方向上堆叠设置在衬底上。连接层的至少一部分设置在第一衬垫层与第二衬垫层之间,其中,第一衬垫层、第二衬垫层、与连接层中至少一个具有波浪形侧壁。本技术可以在相同的占地面积下增加半导体器件的载子通道宽度,优化电子传输信号的可靠性并降低漏电流发生。

技术研发人员:郑俊义,许培育,江丽贞,张昊,陈炫彤,张许阳

受保护的技术使用者:福建省晋华集成电路有限公司

技术研发日:20230420

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!