半导体装置的制作方法

本揭示内容是关于一种半导体装置。

背景技术:

1、半导体制造过程包括许多制造步骤或工艺,每一制造步骤或工艺有助于形成一或多个半导体层。一些层为导电的且在电子系统的装置之间提供电连接。例如,可通过掺杂结晶半导体基板的部分来形成一些层。此外,可通过在结晶半导体基板上添加例如导电层、电阻层及/或绝缘层来形成一层或多层。

2、半导体配置用于多种电子装置,例如移动电话、膝上型计算机、桌上型计算机、平板计算机、钟表、游戏系统及各种其他工业、商业及消费电子产品。半导体配置通常包含半导体部分及形成在半导体部分内部的布线部分。

技术实现思路

1、在一些实施方式中,一种半导体装置包含半导体基板及位于半导体基板上的记忆单元。记忆单元包含底部触点、记忆层、顶部触点、第一电隔离结构及第二电隔离结构。记忆层位于底部触点上。顶部触点位于记忆层上。第一电隔离结构横向围绕顶部触点。第二电隔离结构不同于第一电隔离结构且横向围绕记忆层及底部触点。

2、在一些实施方式中,一种半导体装置包含半导体基板及位于半导体基板上的记忆单元。记忆单元包含底部触点、记忆层、顶部触点及第一电隔离结构。记忆层位于底部触点上。顶部触点位于记忆层上。第一电隔离结构横向围绕记忆层、底部触点及顶部触点的至少一部分。

3、在一些实施方式中,一种半导体装置包含半导体基板及位于半导体基板上的记忆单元。记忆单元包含底部触点、铁电结构、顶部触点及第一电隔离结构。铁电结构位于底部触点上。顶部触点位于铁电结构上。第一电隔离结构横向围绕铁电结构及底部触点。

4、附图说明

5、结合附图,根据以下详细描述可以最好地理解本揭示内容的各态样。注意,根据工业中的标准实务,各种特征未按比例绘制。实际上,为了讨论清楚起见,各种特征的尺寸可任意增加或减小。

6、图1为说明根据一些实施例的形成半导体装置的方法的流程图的示意性说明;

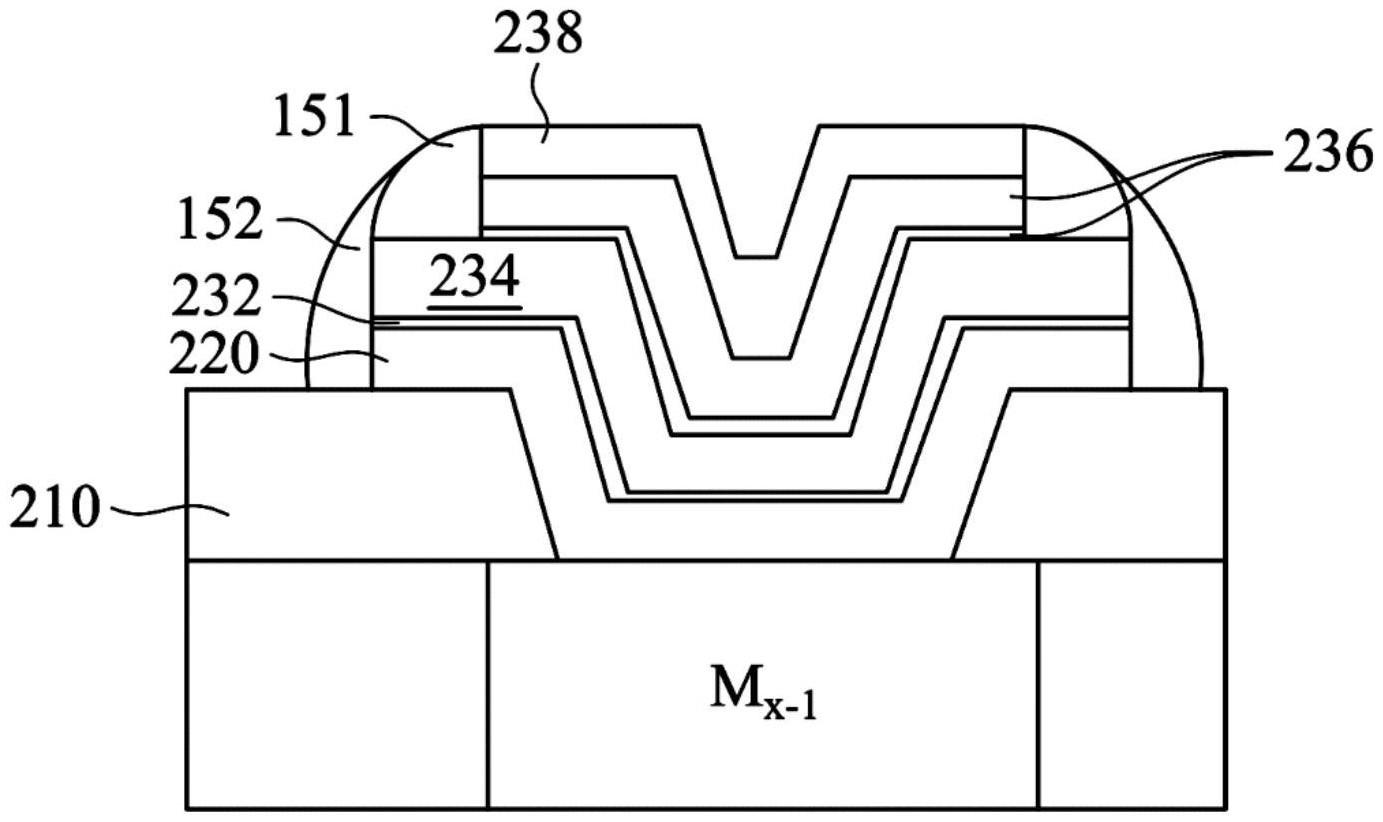

7、图2至图13说明根据一些实施例的在图1的方法的各个阶段的半导体装置的剖面图;

8、图14至图17说明可根据一些实施例形成的替代记忆单元结构。

9、在实务中,相似的附图标记表示相似的结构、特征或元件。

10、【符号说明】

11、10:方法

12、15、20、25、30、35、40、45、50、55、60、65、70:方块

13、100:半导体基板

14、110:第一区域

15、120:层间介电层

16、122:底部接触开口

17、130:第二区域

18、151:第一间隔物

19、152:第二间隔物

20、210:绝缘体层

21、212、214:绝缘体层

22、216:层间介电质(ild)

23、218:通孔

24、220:阻障层

25、230:底部电极

26、232:底部触点

27、234:记忆层

28、236:顶部触点

29、238:介电材料

30、a~h:尺寸

31、mx、mx-1:金属化层

技术特征:

1.一种半导体装置,其特征在于,包含:

2.如权利要求1所述的半导体装置,其特征在于,其中该第二电隔离结构实质上延伸至沿着该第一电隔离结构的最远离该半导体基板的一点。

3.如权利要求1所述的半导体装置,其特征在于,其中该第二电隔离结构实质上延伸至沿着该第一电隔离结构的最靠近该半导体基板的一点。

4.如权利要求1所述的半导体装置,其特征在于,其中该第二电隔离结构实质上延伸至沿着该第一电隔离结构的一点,该点位于该第一电隔离结构的最靠近及最远离该半导体基板的多个点之间的约一半处。

5.一种半导体装置,其特征在于,包含:

6.如权利要求5所述的半导体装置,其特征在于,进一步包含横向围绕该顶部触点的至少一部分的一第二电隔离结构,其中该第一电隔离结构实质上延伸至沿着该第二电隔离结构的最远离该半导体基板的一点。

7.如权利要求5所述的半导体装置,其特征在于,进一步包含横向围绕该顶部触点的至少一部分的一第二电隔离结构,其中该第一电隔离结构实质上延伸至沿着该第二电隔离结构的最靠近该半导体基板的一点。

8.如权利要求5所述的半导体装置,其特征在于,进一步包含横向围绕该顶部触点的至少一部分的一第二电隔离结构,其中该第一电隔离结构实质上延伸至沿着该第二电隔离结构的一点,该点位于该第二电隔离结构的最靠近及最远离该半导体基板的多个点之间的约一半处。

9.一种半导体装置,其特征在于,包含:

10.如权利要求9所述的半导体装置,其特征在于,进一步包含横向围绕该顶部触点的至少一部分的一第二电隔离结构,其中该第一电隔离结构实质上延伸至沿着该第二电隔离结构的一点。

技术总结

揭示一种半导体装置。半导体装置包括半导体基板及位于半导体基板上的记忆单元,其中记忆单元包括底部触点、位于底部触点上的记忆层、位于记忆层上的顶部触点、横向围绕顶部触点的第一电隔离结构,以及横向围绕记忆层及底部触点的第二电隔离结构。

技术研发人员:陈姿妤,石昇弘,张富宸,涂国基

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230509

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!