一种半导体器件的制作方法

本技术涉及一种半导体,尤其涉及一种半导体器件。

背景技术:

1、随着各种电子产品朝小型化发展之趋势,半导体器件的设计也必须符合高积集度及高密度之要求。对于具备凹入式闸极结构之动态随机存取存储器(dynamic randomaccess memory,dram)而言,由于其可以在相同的半导体衬底内获得更长的载子通道长度,以减少电容结构之漏电情形产生,因此在目前主流发展趋势下,其已逐渐取代仅具备平面闸极结构的动态随机存取记忆体。一般来说,具备凹入式闸极结构的动态随机存取存储器是由数目庞大的存储单元(memory cell)聚集形成阵列区,用来存储信息,而每一个存储单元可由晶体管组件与电容器组件串联组成,以接收来自字线(word line,wl)及位线(bitline,bl)的电压信息。因应产品需求,所述阵列区中的存储单元密度须持续提升,造成相关制作工艺与设计上的困难度与复杂度不断增加,导致相关存储器件的效能及可靠度降低。

技术实现思路

1、本实用新型之一目的在于提供一种半导体器件,以解决存储单元密度须持续提升,造成相关制作工艺与设计上的困难度与复杂度不断增加,导致相关存储器件的效能及可靠度降低的技术问题。

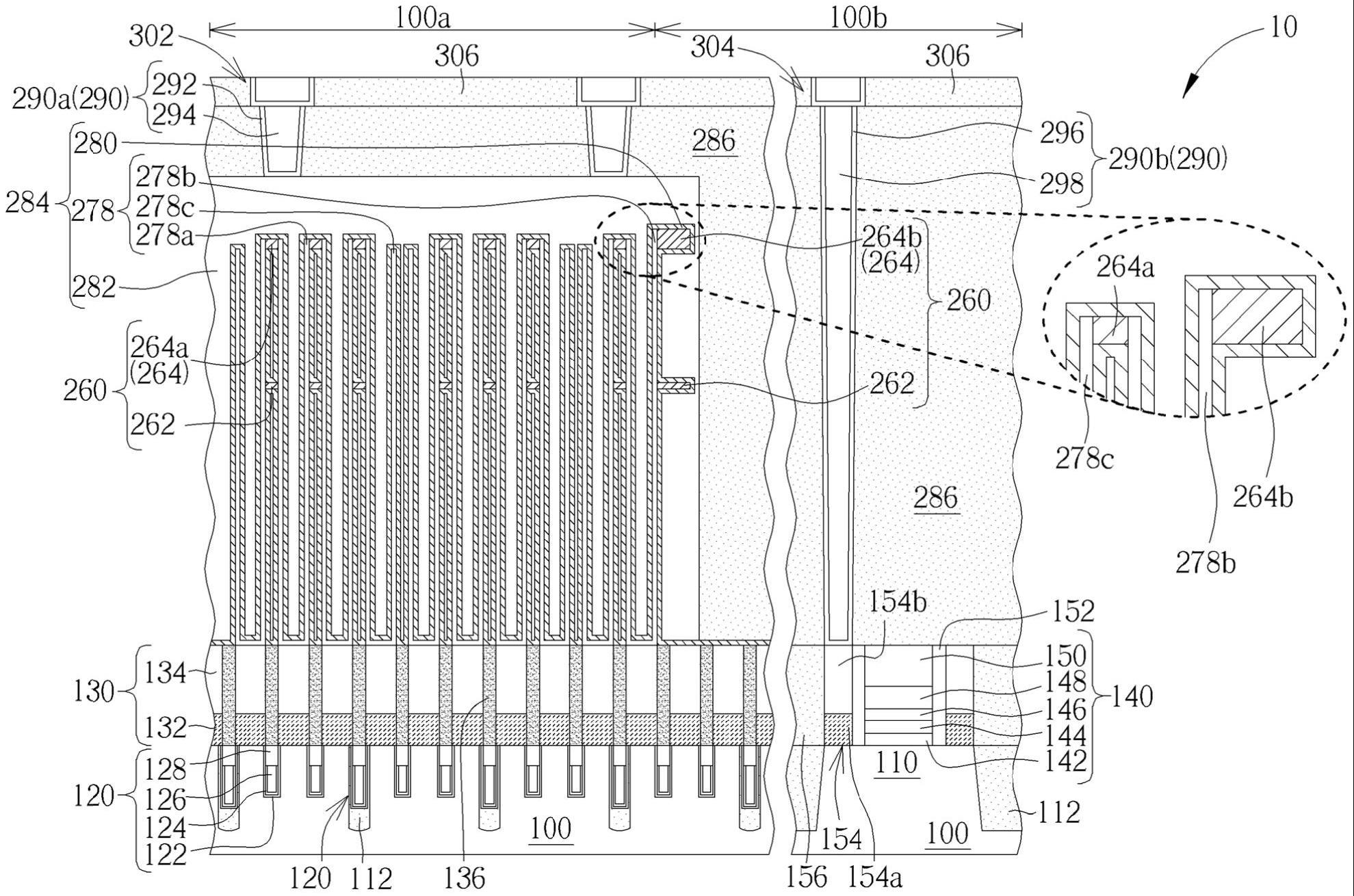

2、为达上述目的,本实用新型之一实施例提供一种半导体器件包括衬底、存储节点焊盘、电容结构以及支撑结构。衬底,包括存储区与周边区;多个存储节点焊盘,设置在所述衬底上并位在所述存储区内;设置在所述存储节点焊盘上的电容结构,包括多个分别与所述存储节点焊盘接触的底电极;以及设置在所述存储节点焊盘上的支撑结构,所述支撑结构设置于所述底电极之间并物理性接触所述底电极,所述支撑结构包括由下而上依序设置的第一支撑层以及第二支撑层,所述第二支撑层具有第一厚度及第二厚度,其中,所述第二厚度大于所述第一厚度,具有所述第一厚度的第二支撑层位在所述存储区,且具有所述第二厚度的第二支撑层位在所述存储区与所述周边区之间。

3、有益效果

4、本公开实施例与现有技术相比存在的有益效果至少包括:通过在存储区与周边区之间形成局部厚度较大的支撑结构,对电容结构提供更为优化的结构支撑性,从而大大提高半导体器件的效能及可靠度。

技术特征:

1.一种半导体器件,其特征在于包括:

2.根据权利要求1所述的半导体器件,其特征在于,具有所述第一厚度的第二支撑层的顶面与所述底电极的顶面共平面,具有所述第二厚度的第二支撑层的最高顶面高于具有所述第一厚度的第二支撑层的顶面。

3.根据权利要求2所述的半导体器件,其特征在于,具有所述第二厚度的第二支撑层的底面与具有所述第一厚度的第二支撑层的底面共平面。

4.根据权利要求2所述的半导体器件,其特征在于,所述电容结构还包括依序堆叠的电容电介质层以及顶电极层,具有所述第二厚度的第二支撑层的侧壁同时物理性接触所述电容电介质层及所述底电极。

5.根据权利要求4所述的半导体器件,其特征在于,具有所述第二厚度的第二支撑层的两相对侧壁分别靠近/远离所述存储区,靠近所述存储区的侧壁物理性接触所述底电极,远离所述存储区的侧壁物理性接触所述电容电介质层。

6.根据权利要求1所述的半导体器件,其特征在于,具有所述第二厚度的第二支撑层相对于所述衬底顶面的高度大于具有所述第一厚度的第二支撑层相对于所述衬底顶面的高度。

7.根据权利要求1所述的半导体器件,其特征在于,所述第二支撑层具有位在所述存储区与所述周边区之间的阶梯状结构。

8.根据权利要求1所述的半导体器件,其特征在于,具有所述第二厚度的第二支撑层的最高顶面与任一所述底电极的顶面共平面,具有所述第一厚度的第二支撑层的顶面低于所述底电极的所述顶面。

9.根据权利要求8所述的半导体器件,其特征在于,具有所述第二厚度的第二支撑层的底面与具有所述第一厚度的第二支撑层的底面共平面。

10.根据权利要求8所述的半导体器件,其特征在于,具有所述第二厚度的第二支撑层具有位在所述存储区与所述周边区之间的阶梯状结构。

11.根据权利要求1所述的半导体器件,其特征在于,所述电容结构还包括依序堆叠的电容电介质层以及顶电极层,同时覆盖在具有所述第二厚度的第二支撑层、具有所述第一厚度的第二支撑层及所述底电极上,所述电容电介质层同时物理性接触具有所述第二厚度的所述第二支撑层的两相对侧壁。

12.根据权利要求1所述的半导体器件,其特征在于,各所述底电极具有u型电极结构或柱状电极结构。

技术总结

本技术公开了一种半导体器件,包括:衬底,包括存储区与周边区;多个存储节点焊盘,设置在所述衬底上并位在所述存储区内;设置在所述存储节点焊盘上的电容结构,包括多个分别与所述存储节点焊盘接触的底电极;以及设置在所述存储节点焊盘上的支撑结构,所述支撑结构设置于所述底电极之间并物理性接触所述底电极,所述支撑结构包括由下而上依序设置的第一支撑层以及第二支撑层,所述第二支撑层具有第一厚度及第二厚度,其中,所述第二厚度大于所述第一厚度,具有所述第一厚度的第二支撑层位在所述存储区,且具有所述第二厚度的第二支撑层位在所述存储区与所述周边区之间,本公开实施例可以提高半导体器件的效能及可靠度。

技术研发人员:冯立伟

受保护的技术使用者:福建省晋华集成电路有限公司

技术研发日:20230613

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!