一种非交叠时钟电路、调制电路和芯片的制作方法

本申请涉及集成电路领域,尤其涉及一种非交叠时钟电路、调制电路和芯片。

背景技术:

1、在集成电路特别是adc等芯片中,时钟信号用于控制其中开关的导通与关断,而现有的时钟电路产生的时钟信号之间的间隔时长一般不够精确,这样会影响开关电路的实际性能,进而直接影响芯片的性能,因此,如何通过提高时钟电路产生的时钟信号的准确性来提高芯片的性能是本领域亟需解决的技术问题。

技术实现思路

1、鉴于上述问题,本申请提出一种非交叠时钟电路、调制电路和芯片。

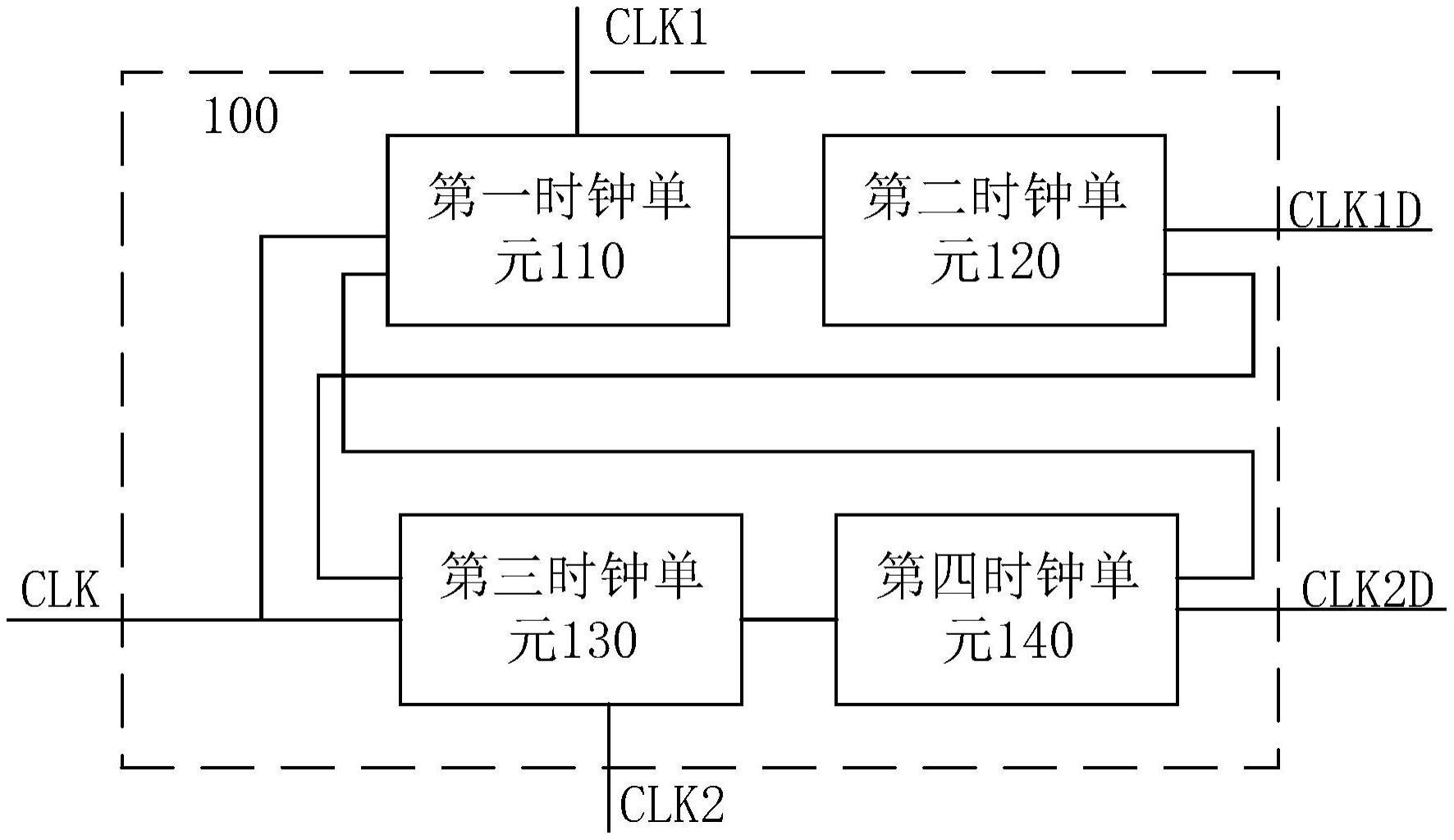

2、本申请实施例提出一种非交叠时钟电路,包括第一时钟单元、第二时钟单元、第三时钟单元和第四时钟单元;

3、所述第一时钟单元,连接时钟信号输入端、第一信号输出端和第四时钟单元,用于对所述时钟信号输入端输出的原始时钟信号进行第一调制,以经所述第一信号输出端输出第一时钟信号;

4、所述第二时钟单元,连接所述第一时钟单元、第二信号输出端和所述第三时钟单元,用于对第一调制后的原始时钟信号进行延时,以经所述第二信号输出端输出第二时钟信号,所述第二时钟信号的下降沿晚于所述第一时钟信号的下降沿;

5、所述第三时钟单元,连接时钟信号输入端、第三信号输出端和所述第二时钟单元,用于对所述时钟信号输入端输出的原始时钟信号进行第二调制,以经所述第三信号输出端输出第三时钟信号,所述第三时钟信号与所述第一时钟信号互不交叠;所述第四时钟单元,连接第四信号输出端和所述第三时钟单元,用于对第二调制后的原始时钟信号进行延时,以经所述第四信号输出端输出第四时钟信号,所述第四时钟信号的下降沿晚于所述第三时钟信号的下降沿。

6、在上述的非交叠时钟电路中,所述第一时钟单元包括反相器、第一调制单元、第一延时单元和第一反相驱动单元;

7、在所述第一时钟单元中,所述反相器的输入端连接所述时钟信号输入端,所述反相器的输出端与所述第一调制单元连接,所述第一调制单元经所述第一反相驱动单元与所述第一信号输出端连接,所述第一调制单元经所述第一延时单元与所述第二时钟单元的第一输入端连接,所述第一调制单元还与所述第二时钟单元的第二输入端连接;

8、所述反相器中包括第一mos管,所述第一延时单元中包括第二mos管,所述第一mos管的长宽比小于所述第二mos管的长宽比。

9、在上述的非交叠时钟电路中,所述第一调制单元包括第一与非门和第一类非门,所述第一类非门用于对输入端接入的信号进行反相;

10、所述第一反相驱动单元包括第二类非门,所述第二类非门用于提升输入端接入的信号的驱动能力并对接入的信号进行反相;

11、所述第一与非门的第一输入端与所述反相器的输出端连接,所述第一与非门的第二输入端与所述第四时钟单元连接;

12、所述第一与非门的输出端与所述第二类非门之间设置有m个第一类非门,所述第一与非门与所述第一延时单元之间设置有n个第一类非门;

13、所述第一与非门与所述第二时钟单元的第二输入端之间设置有y个第一类非门,其中m,n和y均为偶数。

14、在上述的非交叠时钟电路中,m=n=y=2。

15、在上述的非交叠时钟电路中,所述第二时钟单元包括第二调制单元、第二延时单元和第二反相驱动单元;

16、在所述第二时钟单元中,所述第二调制单元的第一输入端和第二输入端分别与所述第一时钟单元连接,所述第二调制单元经所述第二延时单元与所述第三时钟单元的第一输入端连接,所述第二调制单元还经第二反相驱动单元与所述第二信号输出端连接。

17、在上述的非交叠时钟电路中,所述第二调制单元包括第二与非门和第一类非门;

18、所述第二反相驱动单元包括第二类非门,所述第二类非门用于提升输入端接入的信号的驱动能力并对接入的信号进行反相;

19、所述第二与非门的第一输入端为所述第二时钟单元的第一输入端连接,所述第二与非门的第二输入端为所述第二时钟单元的第二输入端连接;

20、所述第二与非门的输出端与所述第二延时单元之间还设置有f个第一类非门,其中,f为奇数,所述第一类非门用于对其输入端接入的信号进行反相;

21、所述第二与非门的输出端与所述第二类非门之间设置有z个第一类非门,其中,z为奇数,所述第二类非门用于提升输入端接入的信号的驱动能力并对接入的信号进行反相。

22、在上述的非交叠时钟电路中,所述第三时钟单元包括第三调制单元、第三延时单元和第三反相驱动单元;

23、在所述第三时钟单元中,所述时钟信号输入端与所述第三调制单元的第二输入端连接,所述第三调制单元的第一输入端与所述第二时钟单元连接,所述第三调制单元经所述第三反相驱动单元与所述第三信号输出端连接,所述第三调制单元经所述第三延时单元与所述第四时钟单元的第二输入端连接,所述第三调制单元还与所述第四时钟单元的第一输入端连接;

24、所述第四时钟单元包括第四调制单元、第四延时单元和第四反相驱动单元;

25、在所述第四时钟单元中,所述第四调制单元的第一输入端和第二输入端分别与所述第三时钟单元连接,所述第四调制单元经所述第四延时单元与所述第一调制单元连接,所述第四调制单元还经第四反相驱动单元与所述第四信号输出端连接。

26、在上述的非交叠时钟电路中,每个延时单元均包括偶数个串联设置的支持延时预设时长的非门。

27、本申请的另一实施例还提出一种调制电路,包括基本调制电路,以及如上述的非交叠时钟电路。

28、本申请的另一实施例还提出一种芯片,包括如上述的非交叠时钟电路或上述的调制电路。

29、本申请的实施例具有以下的有益效果:

30、本申请实施例借助第一时钟单元和第三时钟单元的结构设置,能够产生两相不交叠的时钟信号,且还分别借助第二时钟单元和第四时钟单元的连接设置,能够仅对两相不交叠的时钟信号进行下降沿的延时,能实现多种下降沿滞后功能,有利于非交叠间隔时长的控制,结构简单,可应用于多种需要时钟电路的结构中,还能减少集成电路电荷注入效应,提升芯片性能。

技术特征:

1.一种非交叠时钟电路,其特征在于,包括第一时钟单元、第二时钟单元、第三时钟单元和第四时钟单元;

2.根据权利要求1所述的非交叠时钟电路,其特征在于,所述第一时钟单元包括反相器、第一调制单元、第一延时单元和第一反相驱动单元;

3.根据权利要求2所述的非交叠时钟电路,其特征在于,所述第一调制单元包括第一与非门和第一类非门,所述第一类非门用于对输入端接入的信号进行反相;

4.根据权利要求3所述的非交叠时钟电路,其特征在于,m=n=y=2。

5.根据权利要求2所述的非交叠时钟电路,其特征在于,所述第二时钟单元包括第二调制单元、第二延时单元和第二反相驱动单元;

6.根据权利要求5所述的非交叠时钟电路,其特征在于,所述第二调制单元包括第二与非门和第一类非门;

7.根据权利要求2~6任一项所述的非交叠时钟电路,其特征在于,所述第三时钟单元包括第三调制单元、第三延时单元和第三反相驱动单元;

8.根据权利要求2~6任一项所述的非交叠时钟电路,其特征在于,每个延时单元均包括偶数个串联设置的支持延时预设时长的非门。

9.一种调制电路,其特征在于,包括基本调制电路,以及如权利要求1~8任一项所述的非交叠时钟电路。

10.一种芯片,其特征在于,包括如权利要求1~8任一项所述的非交叠时钟电路或如权利要求9所述的调制电路。

技术总结

本申请涉及集成电路领域,尤其涉及一种非交叠时钟电路、调制电路和芯片。该时钟包括:第一至第四时钟单元;第一时钟单元连接时钟信号输入端和第四时钟单元,用于对时钟信号输入端输出的原始时钟信号进行第一调制并输出第一时钟信号;第二时钟单元连接第一和第三时钟单元,用于对第一调制后的信号进行延时并输出第二时钟信号;第三时钟单元连接时钟信号输入端和第二时钟单元,用于对原始时钟信号进行第二调制并输出第三时钟信号;第四时钟单元连接第三时钟单元,用于对第二调制后的信号进行延时并输出第四时钟信号。本申请的时钟电路用于集成电路芯片中,可提高时钟信号之间间隔时长的准确性,进而提高芯片性能。

技术研发人员:李洁颖

受保护的技术使用者:湖南国科微电子股份有限公司

技术研发日:20230704

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!