一种四路功分器电路结构的制作方法

本技术涉及一种四路功分器电路结构,属于四路功分器。

背景技术:

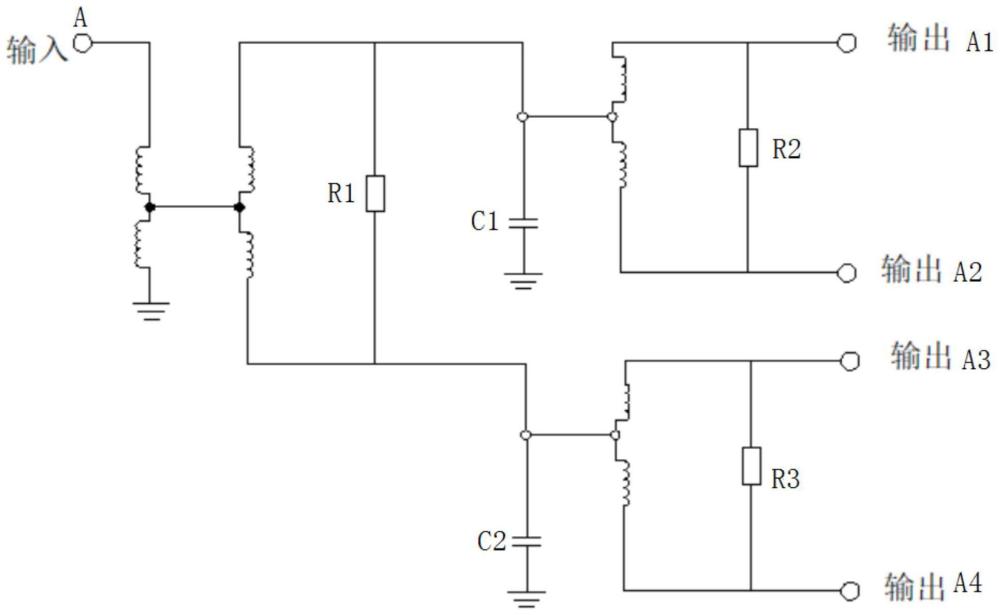

1、如图1所示的四路功分器电路结图,输入端设置有电容,在高频时,会增加耦合损耗,输入输出端均采用相同结构的电感(三电感+两电感模式),该结构在输出端时容易导致二级输出损耗增加。

技术实现思路

1、本实用新型要解决的技术问题是:提供一种四路功分器电路结构,以解决上述现有技术中存在的问题。

2、本实用新型采取的技术方案为:一种四路功分器电路结构,包括第一电感组、第二电感组、第三电感组和第四电感组,第一电感组连接到信号输入端,第二电感组的抽头连接到第一电感组的抽头,第二电感组两端并联有第一电阻,两端分别连接到第三电感组的抽头和第四电感组的抽头,第三电感组和第四电感组输出两端分别并联有第二电阻和第三电阻,第三电感组的抽头和第四电感组的抽头还并联连接有第一电容和第二电容,第二电阻和第三电阻的两端为四路信号输出端。

3、进一步地,上述第一电感组包括串联的两个电感,串联后的一端为信号输入端,另一端接地,相邻两个电感之间的抽头连接到第二电感组的抽头。

4、进一步地,上述第二电感组包括串联的两个电感。

5、进一步地,上述第三电感组和第四电感组均包括串联的两个电感。

6、进一步地,上述第一电感组、第二电感组、第三电感组和第四电感组采用双线方式绕制。

7、本实用新型的有益效果:本实用新型的优化后电路比常规电路在输入端少了一个电容,降低高频耦合损耗,为了降低损耗二级输出,采用直接输出方式;常规电路图使用单条漆包线绕制输入输出绕组;优化后电路图双线方式绕制输入输出绕组,改变了传输阻抗,优化了匹配,从而降低了优化后电路图驻波比,大大降低制造成本,降低产品制造难度,缩小了产品尺寸,使得四路功分器能够实现全密封,一级输入减少电容,二级输出减少线圈(所用磁芯变小接近一半,之前电路的磁芯用的双孔,改进后为单孔),四路功分器整体尺寸变得更小,更容易实现小型化,重量也变轻。

技术特征:

1.一种四路功分器电路结构,其特征在于:包括第一电感组、第二电感组、第三电感组和第四电感组,第一电感组连接到信号输入端,第二电感组的抽头连接到第一电感组的抽头,第二电感组两端并联有第一电阻,两端分别连接到第三电感组的抽头和第四电感组的抽头,第三电感组和第四电感组输出两端分别并联有第二电阻和第三电阻,第三电感组的抽头和第四电感组的抽头还并联连接有第一电容和第二电容,第二电阻和第三电阻的两端为四路信号输出端。

2.根据权利要求1所述的一种四路功分器电路结构,其特征在于:第一电感组包括串联的两个电感,串联后的一端为信号输入端,另一端接地,相邻两个电感之间的抽头连接到第二电感组的抽头。

3.根据权利要求1或2所述的一种四路功分器电路结构,其特征在于:第二电感组包括串联的两个电感。

4.根据权利要求1或2所述的一种四路功分器电路结构,其特征在于:第三电感组和第四电感组均包括串联的两个电感。

5.根据权利要求1或2所述的一种四路功分器电路结构,其特征在于:第一电感组、第二电感组、第三电感组和第四电感组采用双线方式绕制。

技术总结

本技术公开了一种四路功分器电路结构,包括第一电感组、第二电感组、第三电感组和第四电感组,第一电感组连接到信号输入端,第二电感组的抽头连接到第一电感组的抽头,第二电感组两端并联有第一电阻,两端分别连接到第三电感组的抽头和第四电感组的抽头,第三电感组和第四电感组输出两端分别并联有第二电阻和第三电阻,第三电感组的抽头和第四电感组的抽头还并联连接有第一电容和第二电容,第二电阻和第三电阻的两端为四路信号输出端。本技术的电路比常规电路在输入端少了一个电容,降低高频耦合损耗,采用直接输出方式,降低损耗二级输出。

技术研发人员:王勇,蒋国益,黄永芬

受保护的技术使用者:贵阳顺络迅达电子有限公司

技术研发日:20230726

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!