一种基于双振荡器的低功耗真随机数发生器电路

本技术属于cmos模拟集成电路设计,具体地涉及一种基于双振荡器的低功耗真随机数发生器电路。

背景技术:

1、随机数分为真随机数(true random number generator,trng)和伪随机数(pseudo random number generator,prng)两大类。伪随机数依赖算法产生,其本身具有不可避免的周期性,而真随机数可以通过提取互补金属氧化物半导体电路或者新型器件(阻变存储器)中的随机性来生成随机数。与prng相比,trng能够生成无限长且在理论上不可预测的随机数序列,具有更高的安全性和更好的随机性,因此更加安全可靠。另一方面,真随机数在蒙特卡洛模拟、随机过程建模等数学、仿真方法中也有着广泛的应用。

2、真随机数发生器作为信息安全芯片的重要模块,对整体芯片性能起着至关重要的作用。在智能卡、销售机等终端应用中,真随机数发生器芯片输出比特率速率通常在百khz即可满足应用,但其对功耗、面积有着极其严苛的要求。

技术实现思路

1、本实用新型的目的在于提供一种基于双振荡器的低功耗真随机数发生器电路用以解决上述问题。

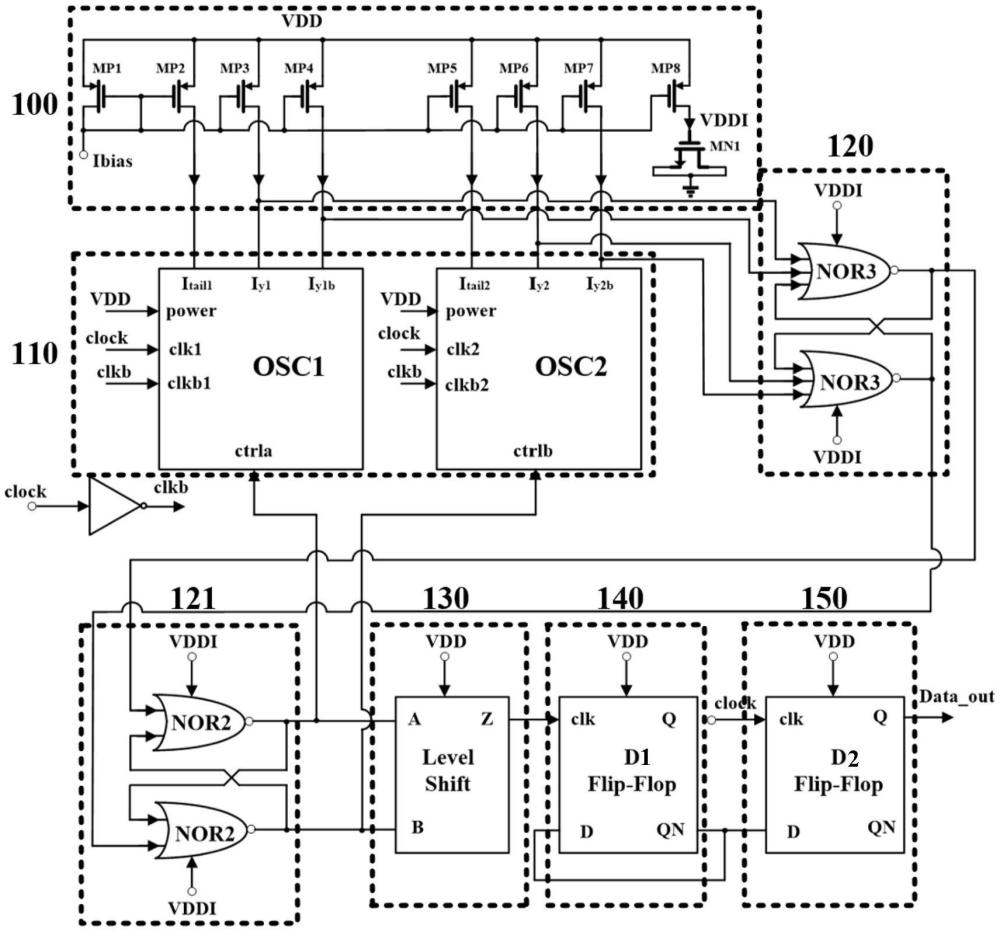

2、为实现上述目的,本实用新型采用的技术方案为:一种基于双振荡器的低功耗真随机数发生器电路,包括电流镜电路、高频振荡器电路、sr锁存器电路、电平提升电路、占空比调整电路和d触发器电路,高频振荡器电路由两个高频振荡器构成,电流镜电路的输入接电源电压vdd,电流镜电路用于为两个高频振荡器的输出提供初始偏置电压,并产生用于sr锁存器电路的供电电压,供电电压低于电源电压vdd,两个高频振荡器用于产生高频时钟信号并输出至sr锁存器电路,sr锁存器电路用于提高高频时钟信号的输出抖动,并输出至电平提升电路,sr锁存器电路的输出同时接高频振荡器的反馈控制端;电平提升电路用于提升sr锁存器电路的输出电压,并输出至占空比调整电路,占空比调整电路用于恢复出陡峭的时钟上升沿,占空比调整电路的输出接d触发器电路的输入,d触发器电路用于输出具有随机性的序列。

3、进一步的,所述电流镜电路包括pmos晶体管mp1-mp8,pmos晶体管mp2和mp5分别为两个高频振荡器的尾电流晶体管,pmos晶体管mp3、mp4、mp6和mp7为两个高频振荡器输出提供初始偏置电压,pmos晶体管mp8作为sr锁存器电路的尾电流晶体管,用于产生一定的压降,生成低于电源电压vdd的供电电压给sr锁存器电路供电。

4、更进一步的,所述高频振荡器包括pmos晶体管mp01、mp02以及nmos晶体管mn01-mn08,nmos晶体管mn03和mn04的源极接地,nmos晶体管mn03和mn04的漏极分别接高频振荡器的输出iy1b和iy1,nmos晶体管mn03和mn04的栅极接sr锁存器电路的输出,pmos晶体管mp01和mp02的源极接尾电流输出信号itail1,pmos晶体管mp01的漏极同时接nmos晶体管mn01的漏极、nmos晶体管mn04的漏极和nmos晶体管mn05的源极,nmos晶体管mn01的源极接地,nmos晶体管mn01的栅极接主时钟信号clok,nmos晶体管mn05的漏极同时接nmos晶体管mn07的栅极和pmos晶体管mp02的栅极,nmos晶体管mn05的栅极接反相主时钟信号clkb,nmos晶体管mn07的源极和漏极同时接地,pmos晶体管mp02的漏极同时接nmos晶体管mn02的漏极、nmos晶体管mn03的漏极和nmos晶体管mn06的源极,nmos晶体管mn02的源极接地,nmos晶体管mn02的栅极接反相主时钟信号clkb,nmos晶体管mn06的漏极同时接nmos晶体管mn08的栅极和pmos晶体管mp01的栅极,nmos晶体管mn08的源极和漏极同时接地,nmos晶体管mn06的栅极接主时钟信号clok。

5、进一步的,所述sr锁存器电路为二级sr锁存器电路。

6、更进一步的,所述sr锁存器电路包括一级三输入sr锁存器和一级二输入sr锁存器。

7、进一步的,所述电平提升电路用于将sr锁存器的输出恢复至电源电压vdd。

8、更进一步的,所述电平提升电路包括pmos晶体管mp11-mp14以及nmos晶体管mn11-mn13,pmos晶体管mp12的漏极接同时接pmos晶体管mp13的栅极、nmos晶体管mn11的漏极和nmos晶体管mn12的漏极,nmos晶体管mn11的源极接地,nmos晶体管mn11的栅极和pmos晶体管mp12的栅极作为该电平提升电路的输入端a,pmos晶体管mp12的源极接pmos晶体管mp11的漏极,pmos晶体管mp11和mp13的源极作为该电平提升电路的电源端,pmos晶体管mp13的漏极接nmos晶体管mn14的源极,nmos晶体管mn14的漏极同时接pmos晶体管mp11的栅极、nmos晶体管mn12的栅极和nmos晶体管mn13的漏极,nmos晶体管mn12的源极接地,nmos晶体管mn12的栅极作为该电平提升电路的输出端z,nmos晶体管mn13的源极接地,nmos晶体管mn13和pmos晶体管mp14的栅极作为该电平提升电路的输入端b。

9、进一步的,所述占空比调整电路由一个连接为二分频结构的d触发器构成。

10、本实用新型的有益技术效果:

11、本实用新型具有随机性好、功耗低、规模小、单片全集成的优点,适用于智能卡、销售机等终端应用中。

技术特征:

1.一种基于双振荡器的低功耗真随机数发生器电路,其特征在于:包括电流镜电路、高频振荡器电路、sr锁存器电路、电平提升电路、占空比调整电路和d触发器电路,高频振荡器电路由两个高频振荡器构成,电流镜电路的输入接电源电压vdd,电流镜电路用于为两个高频振荡器的输出提供初始偏置电压,并产生用于sr锁存器电路的供电电压,供电电压低于电源电压vdd,两个高频振荡器用于产生高频时钟信号并输出至sr锁存器电路,sr锁存器电路用于提高高频时钟信号的输出抖动,并输出至电平提升电路,sr锁存器电路的输出同时接高频振荡器的反馈控制端;电平提升电路用于提升sr锁存器电路的输出电压,并输出至占空比调整电路,占空比调整电路用于恢复出陡峭的时钟上升沿,占空比调整电路的输出接d触发器电路的输入,d触发器电路用于输出具有随机性的序列。

2.根据权利要求1所述的基于双振荡器的低功耗真随机数发生器电路,其特征在于:所述电流镜电路包括pmos晶体管mp1-mp8,pmos晶体管mp2和mp5分别为两个高频振荡器的尾电流晶体管,pmos晶体管mp3、mp4、mp6和mp7为两个高频振荡器输出提供初始偏置电压,pmos晶体管mp8作为sr锁存器电路的尾电流晶体管,用于产生一定的压降,生成低于电源电压vdd的供电电压给sr锁存器电路供电。

3.根据权利要求2所述的基于双振荡器的低功耗真随机数发生器电路,其特征在于:所述高频振荡器包括pmos晶体管mp01、mp02以及nmos晶体管mn01-mn08,nmos晶体管mn03和mn04的源极接地,nmos晶体管mn03和mn04的漏极分别接高频振荡器的输出iy1b和iy1,nmos晶体管mn03和mn04的栅极接sr锁存器电路的输出,pmos晶体管mp01和mp02的源极接尾电流输出信号itail1,pmos晶体管mp01的漏极同时接nmos晶体管mn01的漏极、nmos晶体管mn04的漏极和nmos晶体管mn05的源极,nmos晶体管mn01的源极接地,nmos晶体管mn01的栅极接主时钟信号clok,nmos晶体管mn05的漏极同时接nmos晶体管mn07的栅极和pmos晶体管mp02的栅极,nmos晶体管mn05的栅极接反相主时钟信号clkb,nmos晶体管mn07的源极和漏极同时接地,pmos晶体管mp02的漏极同时接nmos晶体管mn02的漏极、nmos晶体管mn03的漏极和nmos晶体管mn06的源极,nmos晶体管mn02的源极接地,nmos晶体管mn02的栅极接反相主时钟信号clkb,nmos晶体管mn06的漏极同时接nmos晶体管mn08的栅极和pmos晶体管mp01的栅极,nmos晶体管mn08的源极和漏极同时接地,nmos晶体管mn06的栅极接主时钟信号clok。

4.根据权利要求1所述的基于双振荡器的低功耗真随机数发生器电路,其特征在于:所述sr锁存器电路为二级sr锁存器电路。

5.根据权利要求4所述的基于双振荡器的低功耗真随机数发生器电路,其特征在于:所述sr锁存器电路包括一级三输入sr锁存器和一级二输入sr锁存器。

6.根据权利要求1所述的基于双振荡器的低功耗真随机数发生器电路,其特征在于:所述电平提升电路用于将sr锁存器的输出恢复至电源电压vdd。

7.根据权利要求6所述的基于双振荡器的低功耗真随机数发生器电路,其特征在于:所述电平提升电路包括pmos晶体管mp11-mp14以及nmos晶体管mn11-mn13,pmos晶体管mp12的漏极接同时接pmos晶体管mp13的栅极、nmos晶体管mn11的漏极和nmos晶体管mn12的漏极,nmos晶体管mn11的源极接地,nmos晶体管mn11的栅极和pmos晶体管mp12的栅极作为该电平提升电路的输入端a,pmos晶体管mp12的源极接pmos晶体管mp11的漏极,pmos晶体管mp11和mp13的源极作为该电平提升电路的电源端,pmos晶体管mp13的漏极接nmos晶体管mn14的源极,nmos晶体管mn14的漏极同时接pmos晶体管mp11的栅极、nmos晶体管mn12的栅极和nmos晶体管mn13的漏极,nmos晶体管mn12的源极接地,nmos晶体管mn12的栅极作为该电平提升电路的输出端z,nmos晶体管mn13的源极接地,nmos晶体管mn13和pmos晶体管mp14的栅极作为该电平提升电路的输入端b。

8.根据权利要求1所述的基于双振荡器的低功耗真随机数发生器电路,其特征在于:所述占空比调整电路由一个连接为二分频结构的d触发器构成。

技术总结

本技术公开了种基于双振荡器的低功耗真随机数发生器电路,包括电流镜电路、高频振荡器电路、SR锁存器电路、电平提升电路、占空比调整电路和D触发器电路,电流镜电路的输入接电源电压VDD,电流镜电路用于为高频振荡器电路的两个高频振荡器的输出提供初始偏置电压,并给SR锁存器电路提供低于电源电压VDD的供电电压,两个高频振荡器用于产生高频时钟信号并输出至SR锁存器电路,SR锁存器电路用于提高高频时钟信号的输出抖动,并输出至电平提升电路和高频振荡器的反馈控制端;电平提升电路用于提升SR锁存器电路的输出电压,并输出至占空比调整电路,占空比调整电路的输出接D触发器电路的输入,D触发器电路用于输出具有随机性的序列。

技术研发人员:甘巧莹,廖文丽,陈智峰,宋长坤,陈铖颖

受保护的技术使用者:厦门理工学院

技术研发日:20230809

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!