一种超声波模数转换电路的制作方法

本技术涉及一种控制电路,特别是涉及一种超声波模数转换电路。

背景技术:

1、现有技术中,由于fpga是操控层次更低,自由度更大的芯片,对它的编程在解译后转化为fpga内的连线,相当于它内部提供了大量的各种门电路,触发器等各种基本数字器件,编程决定了有多少器件被使用及它们自建的连接,因此,只要fpga足够大,它们在理论上可以形成一切数字电路,包括单片机甚至cpu,fpga在抗干扰能力上,数据传输速度上很大的优势。但是,在现有技术中,都没有很好的利用fpga烧写文件去配置查找表(lut)的内容,从而在相同的电路的情况下实现不同的逻辑功能的技术效果。同时,在第一级信号处理器的处理上没有采用较为适合的带宽,从而影响了谐波失真率,并且输出的增益和相位匹配不平衡,从而没有达到抑制偶数阶谐波的效果。

技术实现思路

1、针对上述问题中存在的不足之处,本实用新型提供一种超声波模数转换电路,使其对信号进行处理,并向上位机(软件系统)反馈处理好的数据,并根据上位机指令向下级单元发送指令。

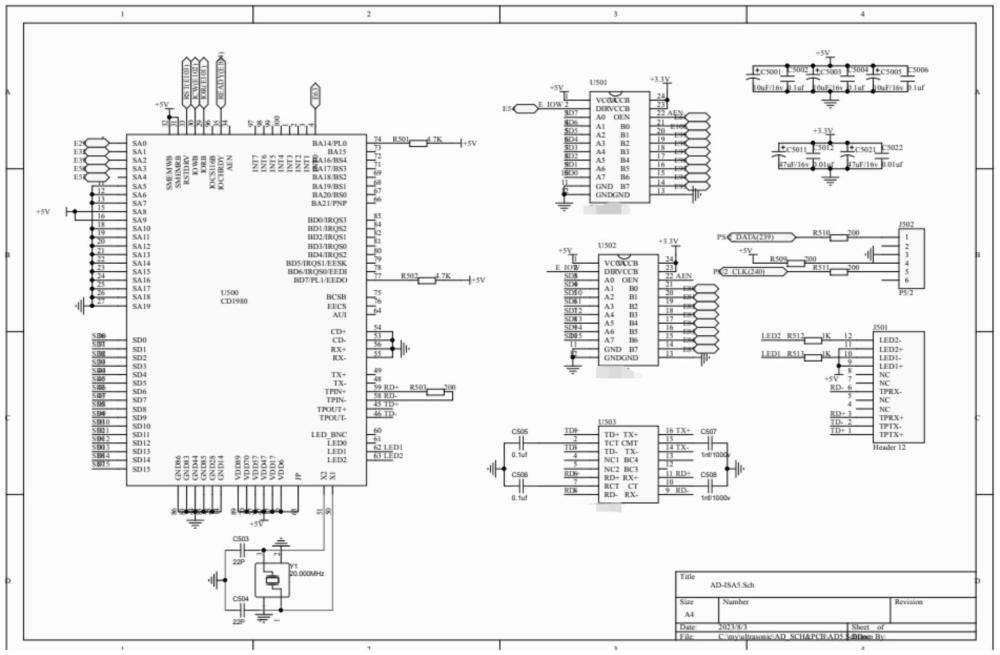

2、为了解决上述问题,本实用新型提供一种超声波模数转换电路,其中,包括中央控制单元电路及时序电路、模数转换电路、存储电路和零延迟缓冲器电路,所述中央控制单元电路及时序电路中,由u501,u502组成时序电路并且与采用fpga模块的u500相匹配,所述模数转换电路中,上级单元电路输出的信号输送至signal端,经过分压电阻r303,r307得到同一基准电压后,送至信号处理器u302的输入端,u302的输出信号送至下一级信号处理单元u301,所述存储电路中,u101-u104为八位单元收发器,在发送和接收方向上都具有非反向三态总线兼容输出,所述零延迟缓冲器电路中,由u203组成的电路是用来分配高速时钟,它可以驱动输出五个低斜率时钟。

3、优选的,在所述模数转换电路中,由r304,r306,r307,c303,c312构成的偏置电路可以使芯片u302得到的偏置电压的预期值和实际值相差在10mv内,由r308,r309构成的反馈电路使电路更加的稳定。

4、优选的,在所述模数转换电路中,u301实际是一个模数转换器,u301将由u302来的模拟信号转换为数字信号并输送至中央处理单元电路。

5、与现有技术相比,本实用新型具有以下优点:

6、1、本实用新型在抗干扰能力上,数据传输速度上很大的优势,通过烧写文件去配置查找表(lut)的内容,从而在相同的电路的情况下实现不同的逻辑功能,同时,非常适合超声探伤设备高速处理信号的要求,数量众多的存储单元,可以根据不同的客户要求量身订制控制、测试、显示等内容。

7、2、本实用新型中的第一级信号处理器u302,具有较宽的带宽(320mhz-3db),谐波失真极低,并且输出的增益和相位匹配平衡,从而抑制偶数阶谐波,同时,第一级信号处理器u302还可以实现将单端输入变成差分输出的功能。

技术特征:

1.一种超声波模数转换电路,其特征在于,包括中央控制单元电路及时序电路、模数转换电路、存储电路和零延迟缓冲器电路,所述中央控制单元电路及时序电路中,由u501,u502组成时序电路并且与采用fpga模块的u500相匹配,所述模数转换电路中,上级单元电路输出的信号输送至signal端,经过分压电阻r303,r307得到同一基准电压后,送至信号处理器u302的输入端,u302的输出信号送至下一级信号处理单元u301,所述存储电路中,u101-u104为八位单元收发器,在发送和接收方向上都具有非反向三态总线兼容输出,所述零延迟缓冲器电路中,由u203组成的电路是用来分配高速时钟,它可以驱动输出五个低斜率时钟。

2.如权利要求1所述的一种超声波模数转换电路,其特征在于,在所述模数转换电路中,由r304,r306,r307,c303,c312构成的偏置电路可以使芯片u302得到的偏置电压的预期值和实际值相差在10mv内,由r308,r309构成的反馈电路使电路更加的稳定。

3.如权利要求1所述的一种超声波模数转换电路,其特征在于,在所述模数转换电路中,u301实际是一个模数转换器,u301将由u302来的模拟信号转换为数字信号并输送至中央处理单元电路。

技术总结

本技术提供一种超声波模数转换电路,涉及一种控制电路技术领域。该技术包括中央控制单元电路及时序电路、模数转换电路、存储电路和零延迟缓冲器电路,由U501,U502组成时序电路并且与采用FPGA模块的U500相匹配,上级单元电路输出的信号输送至signal端,经过分压电阻R303,R307得到同一基准电压后,送至信号处理器U302的输入端,U302的输出信号送至下一级信号处理单元U301,U101‑U104为八位单元收发器,由U203组成的电路是用来分配高速时钟。本技术能够对信号进行处理,并向上位机反馈处理好的数据,并根据上位机指令向下级单元发送指令。

技术研发人员:胡凯

受保护的技术使用者:沈阳佰仕超声设备有限公司

技术研发日:20230901

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!