一种消除时钟频率过冲的振荡器电路及方法与流程

本发明属于半导体设计领域,尤其涉及使用滤波电路实现消减rc振荡器频率启动过冲的方法及电路,具体为一种消除时钟频率过冲的振荡器电路及方法。

背景技术:

1、振荡器本质上是时钟信号,时钟信号对于芯片系统是不可或缺的一部分。张弛振荡器能兼容标准cmos工艺,电路结构不复杂且所占用的芯片面积小,因此受到了广泛应用。产生稳定的时钟,是目前需要解决的问题。

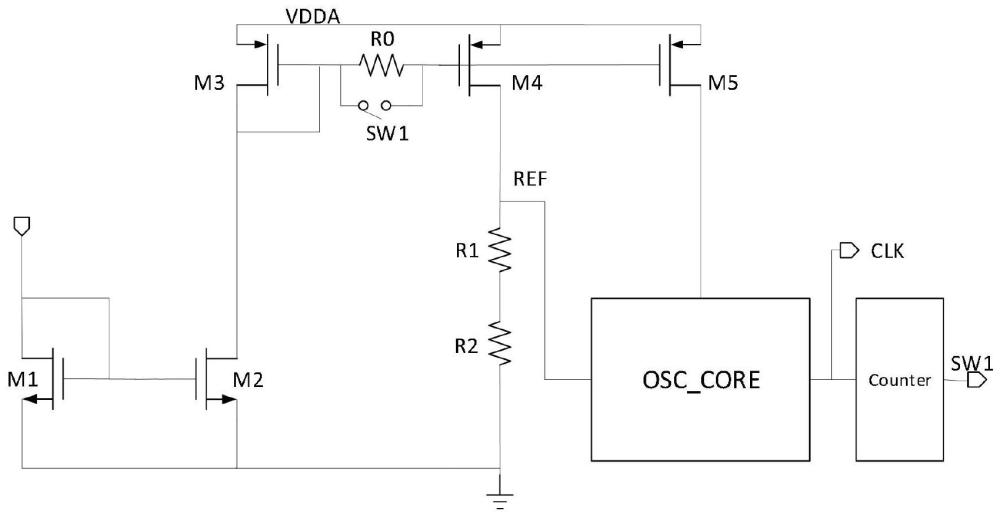

2、图1是现有振荡器的基本结构,由两个nmos电流镜,三个pmos电流镜,两个电阻,振荡核心osc_core组成,该结构较为简单,控制逻辑不复杂,稳定性好,得到广泛应用。现有振荡器是利用恒定电流对电容进行充放电并与参考电压进行比较,从而控制比较器翻转,进而控制恒定电流的充放电状态,使得电路最终得以产生周期性的振荡信号。但是在电路启动过程中,电流镜m4和m5在启动过程中,会发生电流过冲,而rc振荡器频率公式为:vref=i×r,从公式可知振荡器频率与电流成正比。当电流镜的电流发生过冲,i值增大期间,如图2所示振荡器频率也会随电流增大,超过系统规定的时钟过高的频率可能造成系统异常,逻辑运行出错等状况。

技术实现思路

1、本发明的目的是针对现有技术存在的问题,提供一种消除时钟频率过冲的振荡器电路及方法,通过增设一路电阻和开关的简单电路改进,解决了振荡器在启动过程中的频率过冲问题,保证了芯片正常运行。

2、根据本发明说明书的一方面,提供一种消除时钟频率过冲的振荡器电路,包括两个nmos管、三个pmos管、两个电阻及振荡核心,在与其中一nmos管连接的两个pmos管的栅极之间串接一滤波电阻,所述滤波电阻的两端跨接一切换开关,所述切换开关的通断由振荡核心的输出信号控制。

3、上述技术方案在现有rc振荡电路中增设一路滤波电阻和开关且滤波电阻与开关并联,当电路启动过程中,滤波电阻主路导通,切换开关断开,统计振荡核心输出的时钟信号数量,当达到预设数量时,控制切换开关闭合,此时滤波电阻被旁路,电路回到正常工作状态。该技术方案利用输出频率与输出电流正相关,而输出电流又与栅极节点电压的压差绝对值正相关的特性,通过简单的电路改进,避免由于时钟过冲引起的系统时钟异常和频率剧烈快速波动造成flash存储器读写错误的缺陷,克服了振荡器在启动过程中频率过冲的问题,保证了芯片运行正常。

4、作为进一步的技术方案,所述振荡电路包括第一nmos管、第二nmos管、第三pmos管、第四pmos管、第五pmos管、第一电阻、第二电阻和振荡核心,所述第一nmos管的漏极和栅极均连接于第二nmos管的栅极,所述第二nmos管的漏极连接于第三pmos的漏极和栅极,所述第四pmos管和第五nmos管的栅极相连,所述第一电阻和第二电阻串联连接于第四pmos管的漏极,所述滤波电阻串接于第三pmos管的栅极与第四pmos管的栅极之间。

5、作为进一步的技术方案,所述振荡核心的第一输入端连接参考电压,第二输入端连接第五pmos管的漏极,输出端输出时钟信号。

6、作为进一步的技术方案,所述振荡核心的输出端还连接一计数器,所述计数器的输出端连接切换开关。

7、作为进一步的技术方案,所述计数器预设有计数个数,在达到预设的计数个数时,输出信号使切换开关闭合。

8、作为进一步的技术方案,所述滤波电阻的阻值为2~3m欧姆。

9、作为进一步的技术方案,所述切换开关在启动时断开,振荡器稳定工作后,切换开关闭合,滤波电阻被旁路。

10、根据本发明说明书的一方面,提供一种消除时钟频率过冲的方法,采用所述的电路实现,包括:

11、初始化,切换开关处于断开状态,滤波电阻主路导通;

12、振荡电路开始启动,计数器计数振荡输出的时钟信号;

13、在输出的时钟信号个数达到预设值时,计数器输出切换信号;

14、切换开关闭合,滤波电阻被旁路,振荡电路回到正常工作状态。

15、与现有技术相比,本发明的有益效果是:

16、本发明在现有rc振荡电路中增设一路滤波电阻和开关且滤波电阻与开关并联,当电路启动过程中,滤波电阻主路导通,切换开关断开,统计振荡核心输出的时钟信号数量,当达到预设数量时,控制切换开关闭合,此时滤波电阻被旁路,电路回到正常工作状态,有效消除了rc振荡器启动过程中的频率过冲现象。

17、本发明利用输出频率与输出电流正相关,而输出电流又与栅极节点电压的压差绝对值正相关的特性,通过简单的电路改进,避免由于时钟过冲引起的系统时钟异常和频率剧烈快速波动造成flash存储器读写错误,克服了振荡器在启动过程中频率过冲的问题,保证了芯片运行正常。

技术特征:

1.一种消除时钟频率过冲的振荡器电路,包括两个nmos管、三个pmos管、两个电阻及振荡核心,其特征在于,在与其中一nmos管连接的两个pmos管的栅极之间串接一滤波电阻,所述滤波电阻的两端跨接一切换开关,所述切换开关的通断由振荡核心的输出信号控制。

2.根据权利要求1所述一种消除时钟频率过冲的振荡器电路,其特征在于,所述振荡电路包括第一nmos管、第二nmos管、第三pmos管、第四pmos管、第五pmos管、第一电阻、第二电阻和振荡核心,所述第一nmos管的漏极和栅极均连接于第二nmos管的栅极,所述第二nmos管的漏极连接于第三pmos的漏极和栅极,所述第四pmos管和第五nmos管的栅极相连,所述第一电阻和第二电阻串联连接于第四pmos管的漏极,所述滤波电阻串接于第三pmos管的栅极与第四pmos管的栅极之间。

3.根据权利要求2所述一种消除时钟频率过冲的振荡器电路,其特征在于,所述振荡核心的第一输入端连接参考电压,第二输入端连接第五pmos管的漏极,输出端输出时钟信号。

4.根据权利要求3所述一种消除时钟频率过冲的振荡器电路,其特征在于,所述振荡核心的输出端还连接一计数器,所述计数器的输出端连接切换开关。

5.根据权利要求4所述一种消除时钟频率过冲的振荡器电路,其特征在于,所述计数器预设有计数个数,在达到预设的计数个数时,输出信号使切换开关闭合。

6.根据权利要求1所述一种消除时钟频率过冲的振荡器电路,其特征在于,所述滤波电阻的阻值为2~3m欧姆。

7.根据权利要求1所述一种消除时钟频率过冲的振荡器电路,其特征在于,所述切换开关在启动时断开,振荡器稳定工作后,切换开关闭合,滤波电阻被旁路。

8.一种消除时钟频率过冲的方法,采用权利要求1-7中任一项所述的电路实现,其特征在于,包括:

技术总结

本发明公开一种消除时钟频率过冲的振荡器电路及方法,振荡器电路包括两个NMOS管、三个PMOS管、两个电阻及振荡核心,在与其中一NMOS管连接的两个PMOS管的栅极之间串接一滤波电阻,所述滤波电阻的两端跨接一切换开关,所述切换开关的通断由振荡核心的输出信号控制。本发明通过增设一路电阻和开关的简单电路改进,解决了振荡器在启动过程中的频率过冲问题,保证了芯片正常运行。

技术研发人员:张喜

受保护的技术使用者:武汉芯必达微电子有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!