半导体存储装置的制作方法

本发明的实施方式涉及一种半导体存储装置及其制造方法。

背景技术:

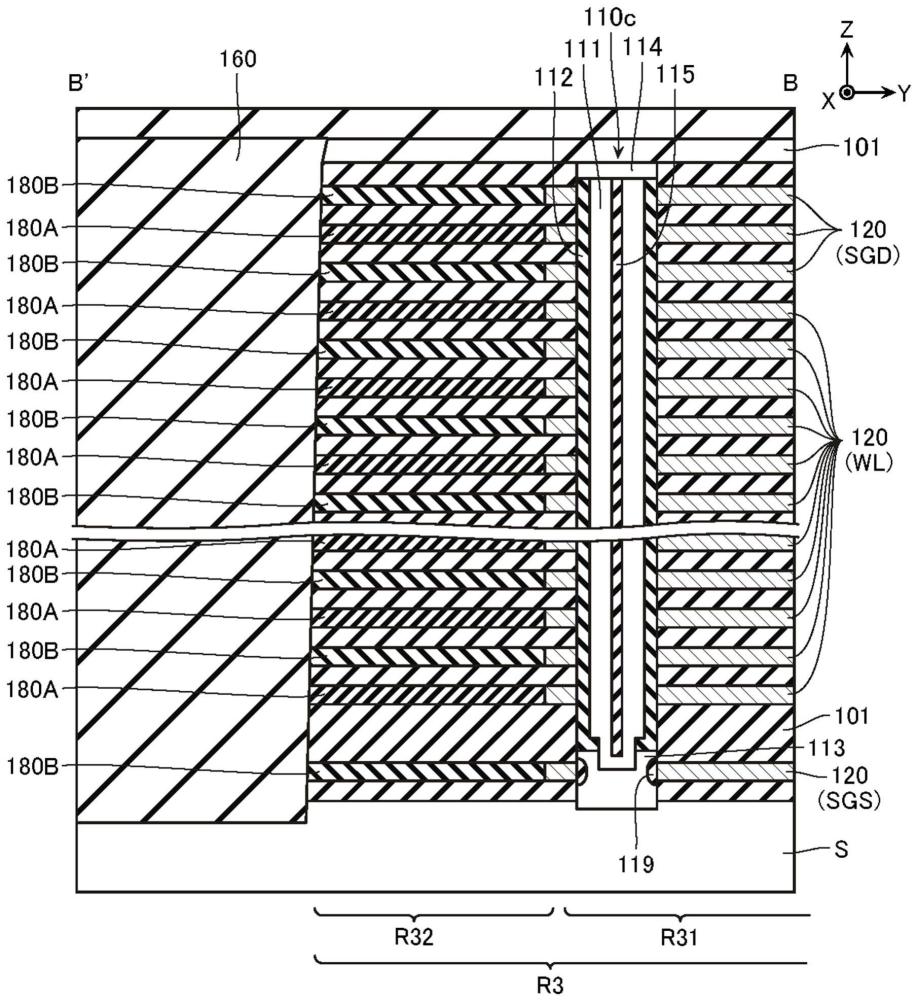

1、已知有一种半导体存储装置,具备:衬底;多个导电层,配设在与衬底的表面交叉的第1方向,且在与第1方向交叉的第2方向延伸;多个绝缘层,分别设置在多个导电层之间;半导体层,在第1方向延伸,与多个导电层及多个绝缘层对向;及栅极绝缘层,设置在多个导电层与半导体层之间。

技术实现思路

1、实施方式提供一种能够改善制造良率的半导体存储装置及其制造方法。

2、一实施方式的半导体存储装置具备:衬底;多个导电层,配设在与衬底的表面交叉的第1方向,且在与第1方向交叉的第2方向延伸;多个绝缘层,分别设置在多个导电层之间;半导体层,在第1方向延伸,与多个导电层及多个绝缘层对向;及栅极绝缘层,设置在多个导电层与半导体层之间;且具有形成多个导电层、多个绝缘层、半导体层及栅极绝缘层的衬底上的第1区域、以及衬底上的与第1区域不同的第2区域,多个导电层包含多个第1导电层及多个第2导电层,且所述半导体存储装置在第2区域的与多个第1导电层相同的层具备与第1导电层不同的多个第1膜,在第2区域的与多个第2导电层相同的层具备与第2导电层及第1膜不同的多个第2膜。

技术特征:

1.一种半导体存储装置,具备:

2.根据权利要求1所述的半导体存储装置,其中

3.根据权利要求1所述的半导体存储装置,其中

4.根据权利要求1所述的半导体存储装置,其中

5.根据权利要求4所述的半导体存储装置,其中

6.根据权利要求5所述的半导体存储装置,其中

7.根据权利要求1所述的半导体存储装置,其中

8.根据权利要求7所述的半导体存储装置,其中

9.一种半导体存储装置,具备:

10.根据权利要求9所述的半导体存储装置,其中

11.根据权利要求9所述的半导体存储装置,其中

12.根据权利要求9所述的半导体存储装置,其中

13.根据权利要求12所述的半导体存储装置,其中

14.根据权利要求11所述的半导体存储装置,其中

15.根据权利要求14所述的半导体存储装置,其中

16.根据权利要求9所述的半导体存储装置,其中

17.一种半导体存储装置,具备:

18.根据权利要求17所述的半导体存储装置,其中

19.根据权利要求17所述的半导体存储装置,其中

20.根据权利要求17所述的半导体存储装置,其中

21.根据权利要求20所述的半导体存储装置,其中

22.根据权利要求19所述的半导体存储装置,其中

23.根据权利要求22所述的半导体存储装置,其中

24.根据权利要求17所述的半导体存储装置,其中

25.一种半导体存储装置,具备:

26.根据权利要求25所述的半导体存储装置,其中所述积层构造还包含材料与所述第1层的材料不同的多个绝缘层,所述导电层及所述绝缘层在所述衬底上,于所述衬底的所述第1区域内,在所述第2方向上交替积层,且所述第1层及所述绝缘层在所述衬底上,于所述衬底的所述第2区域内,在所述第2方向上交替积层。

27.根据权利要求26所述的半导体存储装置,其中

28.根据权利要求27所述的半导体存储装置,其中在所述衬底上,于所述衬底的所述第3区域内,没有配设所述第2导电层及所述第1膜。

29.根据权利要求27所述的半导体存储装置,其中所述绝缘层设置在所述衬底上,跨于所述衬底的所述第1、第2及第3区域。

30.根据权利要求29所述的半导体存储装置,其中所述第2膜的上表面及下表面各个与所述衬底的所述第3区域内的对应一个所述绝缘层接触。

31.根据权利要求30所述的半导体存储装置,其中所述第2膜包含氮化硅。

32.根据权利要求30所述的半导体存储装置,其中所述绝缘层包含氧化硅。

33.根据权利要求27所述的半导体存储装置,其中在所述衬底的所述第3区域内,所述第2膜的一部分配设在所述第1导电层上,且所述第2膜的另一部分配设在所述第1导电层下。

34.根据权利要求25所述的半导体存储装置,其中所述第1膜的相对于磷酸的蚀刻速率与所述第2膜的相对于磷酸的蚀刻速率不同。

技术总结

实施方式涉及一种半导体存储装置及其制造方法。实施方式的半导体存储装置具备:衬底;多个导电层,配设在与衬底的表面交叉的第1方向,且在与第1方向交叉的第2方向延伸;多个绝缘层,分别设置在多个导电层之间;半导体层,在第1方向延伸,与多个导电层及多个绝缘层对向;及栅极绝缘层,设置在多个导电层与半导体层之间;且具有形成多个导电层、多个绝缘层、半导体层及栅极绝缘层的第1区域、以及与该第1区域不同的第2区域,多个导电层包含多个第1导电层及多个第2导电层,所述半导体存储装置在第2区域的与多个第1导电层相同的层具备与第1导电层不同的多个第1膜,在第2区域的与多个第2导电层相同的层具备与第2导电层及第1膜不同的多个第2膜。

技术研发人员:志摩祐介

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!