时域交织模数转换器的自纠错时钟偏差片上校准方法及装置

本发明属于集成电路超高速数据转换器,尤其涉及一种时域交织模数转换器的自纠错时钟偏差片上校准装置及方法。

背景技术:

1、在新兴的通信系统中,由于信号带宽扩大,对模数转换器的转换速率要求比以往任何时候都高。由于模数转换器的转换速度必须在千兆赫兹以上,时间交织结构变得必不可少。此外,由于现代cmos工艺的发展,具有数字友好结构的逐次逼近型模数转换器表现出优异的功率效率。因此,许多最先进的时域交织模数转换器都采用逐次逼近型模数转换器作为子信道,具有良好的功率效率。然而,在时域交织模数转换器中,信道间的增益、失调量和采样时间等误差会严重降低性能。增益和失调误差相对容易检测,因为它们的功率与输入频率和转换速率无关。然而,随着采样时间偏差引起的误差功率随着输入频率的增加而增大,时序偏差已成为时域交织模数转换器的主要问题。采样时序偏差校准方案可根据检测方法分为模拟域检测和数字域检测。模拟域校准通常需要专用的输入信号,如时钟或已知的正弦输入信号。然而,模拟域校准不能反映芯片上出现的所有失配方面,例如子信道之间的信号/时钟路径失配。相反,数字域标定可以包含所有的时序偏差,但计算量大。因此,如何开发出一种高效可靠的时间偏差校准方法成为了工业界和学术界研究的重点。

技术实现思路

1、发明目的:为了解决上述现有技术存在的问题,本发明提供了一种时域交织模数转换器的自纠错时钟偏差片上校准装置及方法。

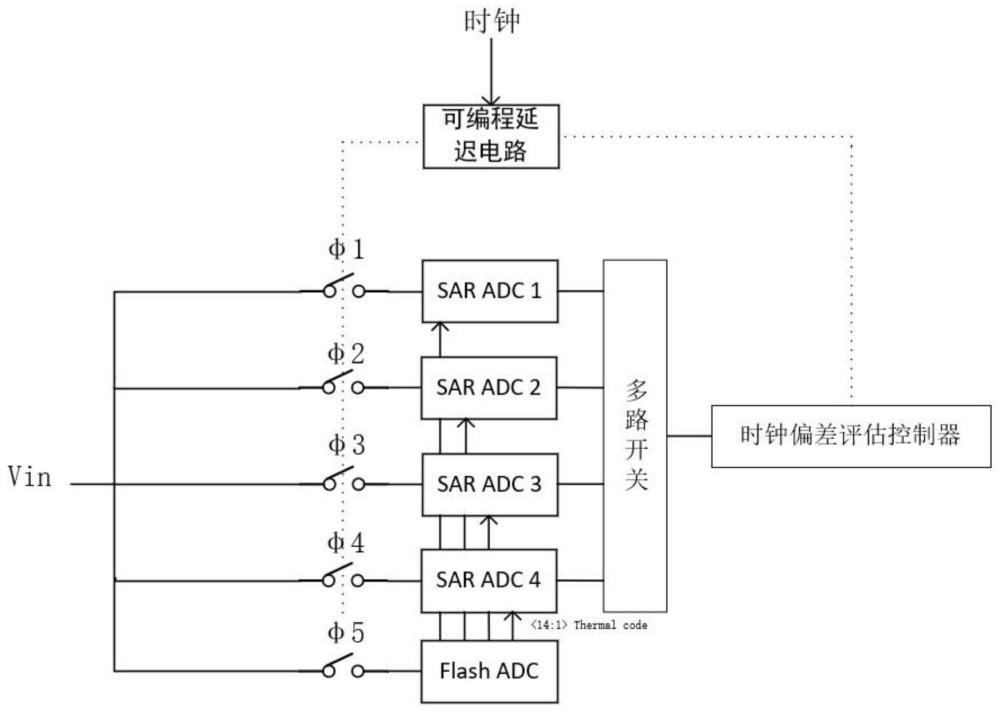

2、技术方案:本发明提供了一种时域交织模数转换器的自纠错时钟偏差片上校准方法,在所有子逐次逼近模数转换电路的高位和低位之间设置第一冗余位,在子逐次逼近模数转换电路低位中插入第二冗余位和第三冗余位;该方法具体为:

3、步骤1: 令m=(dsar[5]*dsar[4])⊕(d[n+1]-d[n-1]),其中d[n+1]为当前第n个子逐次逼近模数转换器的下一个子逐次逼近模数转换器的总的输出码,d[n-1]为当前第n个子逐次逼近模数转换器的上一个子逐次逼近模数转换器的总的输出码,dsar[4]为第二冗余位的输出码,sar[5]为第三冗余位的输出码;

4、步骤2:若m=1,则令输入至可编程延迟电路的控制码delay code加1,直到m=0;若m=0,则令输入至可编程延迟电路的控制码delay code减1,直到m=1,从而通过可编程延迟电路来校准每个逐次逼近模数转换电路时钟偏差;

5、步骤3:当校准完毕,若dsar[7]=0,则认定时域交织模数转换器的输出没有超出量程,若dsar[7]=1,则判断交织模数转换器的输出与失调电压之和是否超出量程,若超出量程,则转步骤1重新进行校准,dsar[7]为第一冗余位的输出。

6、进一步的,包括:快闪型模数转换电路、n个子逐次逼近模数转换电路,可编程延迟电路以及时钟偏差评估控制器;所有子逐次逼近模数转换电路的高位和低位之间设置第一冗余位,每个子逐次逼近模数转换电路低位中插入第二冗余位和第三冗余位;

7、所述快闪型模数转换电路的时钟由外部时钟直接提供,子逐次逼近模数转换电路的多相时钟由可编程延迟电路提供,所述快闪型模数转换电路输出的14位thermal码提供给每个子逐次逼近模数转换电路的高位,所述时钟偏差评估控制器根据步骤1-步骤2进行时钟偏差评估,并给可编程延迟电路提供时钟延迟增加或减小的指令,从而控制可编程延迟电路来校准子逐次逼近模数转换电路的时钟偏差,时钟偏差评估控制器还根据步骤3判断校准是否超出量程。

8、进一步的,可编程延迟电路包括第一~第六反相器和第一~第四延迟开关单元,第一反相器的输入端作为可编程延迟电路的时钟输入端,第一~第六反相器依次连接,第一反相器的输出端连接第一延迟开关单元,第二反相器的输出端连接第二延迟开关单元,第三反相器的输出端连接第三延迟开关单元,第四反相器的输出端连接第四延迟开关单元;第一~第四延迟开关单元结构相同均包括第一~第八开关和第一~第八mos电容,一个开关对应一个mos电容,开关的动端连接相应反相器的输出端,不动端连接对应的mos电容,所述mos电容包括第一mos管和第二mos管,第一、第二mos管的栅极相互连接后连接对应的开关,第一mos管的源级和漏极连接电源,第二mos管的源级和漏极接地;第一延迟开关单元控制码为<15:8>,第二延迟开关单元控制码为<7:0>,第三延迟开关单元控制码为<31:24>,第四mos延迟开关单元控制码为<23:16>。

9、进一步的,所述子逐次逼近模数转换电路包括失调校准控制器和比较器失调校准电路,所述比较器失调校准电路在比较器输出端加入开关电容阵列,失调校准控制器调整比较器输出端开关电容阵列控制码并通过观察比较器输出是否翻转来判断失调校准是否完成。

10、有益效果:

11、1.本发明通过在快闪型模数转换器和子逐次逼近模数转换电路之间添加冗余位来进行自纠错,并且可以仅仅只需要调整纠错范围就可以覆盖可能存在的快闪型模数转换器和子逐次逼近模数转换电路的失调电压,具有很好的适应能力。

12、2.本发明通过在子逐次逼近模数转换电路中添加两位冗余位并通过一定的逻辑作为符号位一,下一个子模数转换器的输出减去上一个子模数转换器的输出作为符号位二,两个符号位异或就可以判断时钟偏差校准的方向,该校准方法逻辑简单,收敛速度快,仅需要数字逻辑门电路就可以实现。

13、3.本发明只需要简单的比较器失调校准就可以把逐次逼近模数转换器的输入失调电压降到一个比较低的范围,并且通过对于不同的子逐次逼近模数转换器使用不同的dsar[offset]位来解决不同子逐次逼近模数转换器之间输入失调电压不一致所导致的时钟偏差校准错误的问题

14、4.本发明提出的模数转换器的一时钟偏差校准方法完全片上进行,数字与模拟结合,校准灵活,可以有效解决系统随着温度、老化等变化引起的误差难以校准的问题。

15、5.本发明应用于超高速时域交织模数转换器,为业界生产更快速度、更高性能的数据转换器提供技术支撑。

技术特征:

1.时域交织模数转换器的自纠错时钟偏差片上校准方法,其特征在于,在所有子逐次逼近模数转换电路的高位和低位之间设置第一冗余位,在子逐次逼近模数转换电路低位中插入第二冗余位和第三冗余位;该方法具体为:

2.应用于权利要求1所述的时域交织模数转换器的自纠错时钟偏差片上校准方法的校准装置,其特征在于,包括:快闪型模数转换电路、n个子逐次逼近模数转换电路,可编程延迟电路以及时钟偏差评估控制器;所有子逐次逼近模数转换电路的高位和低位之间设置第一冗余位,每个子逐次逼近模数转换电路低位中插入第二冗余位和第三冗余位;

3.根据权利要求2所述的时域交织模数转换器的自纠错时钟偏差片上校准装置,其特征在于,可编程延迟电路包括第一~第六反相器和第一~第四延迟开关单元,第一反相器的输入端作为可编程延迟电路的时钟输入端,第一~第六反相器依次连接,第一反相器的输出端连接第一延迟开关单元,第二反相器的输出端连接第二延迟开关单元,第三反相器的输出端连接第三延迟开关单元,第四反相器的输出端连接第四延迟开关单元;第一~第四延迟开关单元结构相同均包括第一~第八开关和第一~第八mos电容,一个开关对应一个mos电容,开关的动端连接相应反相器的输出端,不动端连接对应的mos电容,所述mos电容包括第一mos管和第二mos管,第一、第二mos管的栅极相互连接后连接对应的开关,第一mos管的源级和漏极连接电源,第二mos管的源级和漏极接地;第一延迟开关单元控制码为<15:8>,第二延迟开关单元控制码为<7:0>,第三延迟开关单元控制码为<31:24>,第四mos延迟开关单元控制码为<23:16>。

4.根据权利要求2所述的时域交织模数转换器的自纠错时钟偏差片上校准装置,其特征在于,所述子逐次逼近模数转换电路包括失调校准控制器和比较器失调校准电路,所述比较器失调校准电路在比较器输出端加入开关电容阵列,失调校准控制器调整比较器输出端开关电容阵列控制码并通过观察比较器输出是否翻转来判断失调校准是否完成。

技术总结

本发明公开了时域交织模数转换器的自纠错时钟偏差片上校准方法及装置,包括快闪型模数转换电路、子逐次逼近模数转换电路、时钟偏差评估控制器。子逐次逼近模数转换电路使用基于符号相等的时钟偏差校准方法,快闪型模数转换电路工作在模数转换器全采样率下来进行粗转换,子逐次逼近模数转换电路进行时域交织并进行细转换,在快闪型模数转换电路和子逐次逼近模数转换电路之间添加一位冗余来判断校准是否出错。对逐次逼近模数转换电路的比较器进行基于电容的失调校准方案。该时钟偏差校准装置控制逻辑简单,电路复杂度低,可以达到以较小的代价实现完全片上校准时钟偏差的目的。

技术研发人员:勾庆瑞,郑丽霞,吴金,孙伟锋

受保护的技术使用者:东南大学

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!