半导体存储器及其形成方法与流程

本公开涉及一种半导体制造,特别涉及一种半导体存储器及其形成方法。

背景技术:

1、半导体存储器通常包括存储电容器以及连接到所述存储电容器的存储晶体管。存储电容器用来存储代表存储信息的电荷,存储晶体管中形成有源区、漏区和栅极。其中,栅极用于控制源区和漏区之间的电流流动,并连接至字线,源区用于构成位线接触区,以连接至位线,漏区用于构成存储节点接触区,以连接至存储电容器。

2、随着半导体制作工艺中集成度的增加,位线之间的间距变得越来越小。因此,在位线之间,容易形成寄生电容,随着这种寄生电容的增加,对半导体器件的性能的影响越来越大,例如半导体器件的动作速度变慢,数据刷新的特性变差。

3、例如,可以利用rc延迟时间来评价半导体存储器由于寄生效应引起的电信号传输速率的延迟。rc延迟时间满足如下公式:

4、trc=(ρ0·l1/td)(kd/ε0)

5、其中,ρ0:金属的线电阻;

6、l1:金属的长度;

7、kd:绝缘材料的介电常数;

8、ε0:金属的导电率;

9、td:绝缘材料的厚度。

10、随着集成度的增加,布线的长度增加,绝缘材料的厚度变薄,因此根据上式,rc延迟时间开始变大。

11、图1是说明半导体存储器的特征尺寸与延迟时间之间的关系的图。如图1所示,在以几mm为单位的设计尺寸中,门的信号传输速度比布线引起的rc延迟效应更占主导,因此布线引起的rc延迟不是大问题,但进入1mm或更小的区域时,布线引起的rc延迟效应迅速呈指数增长。

12、因此,相比于门的信号传输速率的轻微增加,rc延迟效应占据主导地位,导致信号处理速度的严重延迟。

13、定性检验上述rc延迟的等式,由小型化导致的布线长度的增加和绝缘材料厚度的减少是不可避免的,因此为了减少这种延迟,布线材料的考虑例如布线材料的替换是不可避免的。此外,考虑绝缘材料以降低寄生电容也是必要的。

14、根据上述公式,由于小型化,l1/td必然会增加,这是小型化的负面影响。由于小型化,l1增加,td减少,trc增加。为了补偿这一点,需要从ε0、kd方面进行调整。但ε0、kd等是材料的固有值,因此期望更换材料。

技术实现思路

1、本公开是为了解决上述问题而完成的,其目的在于提供一种半导体存储器及其形成方法,能降低位线之间的寄生电容,提升半导体存储器的性能。

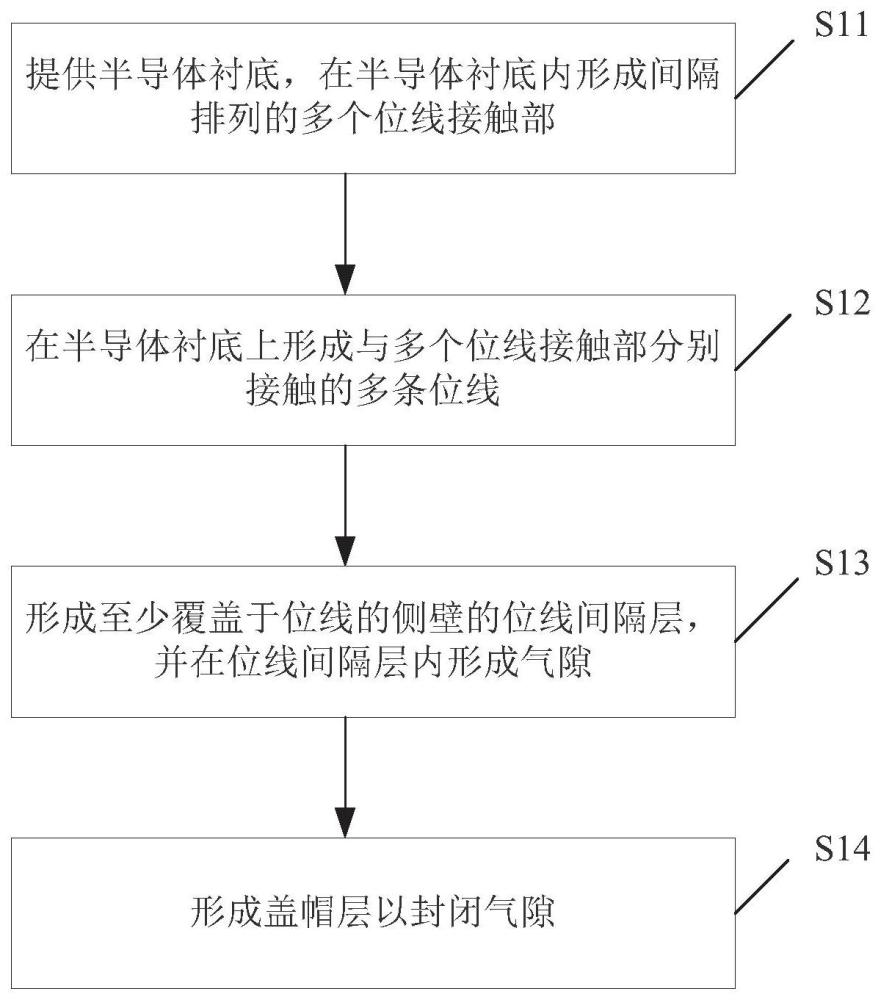

2、本公开提供一种半导体存储器的形成方法,其包括如下步骤:提供半导体衬底,在所述半导体衬底内形成间隔排列的多个位线接触部的步骤;在所述半导体衬底上形成与多个所述位线接触部分别接触的多条位线的步骤;形成至少覆盖于所述位线的侧壁的位线间隔层,并在所述位线间隔层内形成气隙的步骤;以及形成盖帽层以封闭所述气隙的步骤。

3、可选地,在半导体存储器的形成方法中,形成至少覆盖于所述位线的侧壁的位线间隔层,并在所述位线间隔层内形成气隙的步骤包括:在所述位线、所述半导体衬底上依次形成第一隔离层及牺牲掩膜层的步骤;刻蚀所述牺牲掩膜层,仅保留所述牺牲掩膜层在所述位线的侧壁上的部分的步骤;通过原子层沉积ald方式形成覆盖所述第一隔离层的顶部和所述牺牲掩膜层的第二隔离层的步骤;刻蚀所述第二隔离层的顶部和底部以露出所述牺牲掩膜层的步骤;利用旋涂玻璃sog填充所述位线之间的间隙并进行平坦化处理的步骤;以及刻蚀所述牺牲掩膜层以形成气隙的步骤。

4、可选地,在半导体存储器的形成方法中,所述牺牲掩膜层为旋涂硬掩模soh。

5、可选地,在半导体存储器的形成方法中,通过原子层沉积ald方式形成所述第二隔离层的步骤在室温下进行。

6、可选地,在半导体存储器的形成方法中所述牺牲掩膜层为氧碳化硅sioc。

7、可选地,在半导体存储器的形成方法中,还包括在所述位线与所述位线接触部之间形成自对准硅化物的步骤。

8、可选地,在半导体存储器的形成方法中,在所述位线与所述位线接触部之间形成自对准硅化物的步骤包括:在形成所述位线接触部时,对所述位线接触部的多晶硅进行离子注入掺杂的步骤;沉积外围栅的金属层的步骤;以及进行离子注入掺杂后的快速热退火,使所述金属层与多晶硅进行反应以生成自对准硅化物的步骤。

9、可选地,在半导体存储器的形成方法中,所述金属层为tin,所述自对准硅化物为tisi。

10、本公开还提供一种半导体存储器,其包括:半导体衬底,所述半导体衬底内形成有间隔排列的多个位线接触部;多条位线,所述多条位线形成在所述半导体衬底上方且与多个所述位线接触部分别接触;位线间隔层,所述位线间隔层至少覆盖于所述位线的侧壁,且所述位线间隔层内形成有气隙;以及盖帽层,所述盖帽层封闭所述气隙。

11、可选地,在半导体存储器中,在所述位线与所述位线接触部之间形成有自对准硅化物。

12、根据本公开的半导体存储器及其形成方法,通过在位线间隔层中形成气隙,使用介电常数低的空气作为位线绝缘材料,从而能降低位线之间的寄生电容,提升半导体存储器的性能。

13、此外,根据本公开的半导体存储器及其形成方法,通过在位线与位线接触部之间形成有自对准硅化物,从而能降低位线与位线接触部之间的接触电阻,抑制接触电阻和寄生电容的干扰,提升半导体存储器的性能。

技术特征:

1.一种半导体存储器的形成方法,其特征在于,包括如下步骤:

2.如权利要求1所述的半导体存储器的形成方法,其特征在于,

3.如权利要求2所述的半导体存储器的形成方法,其特征在于,

4.如权利要求3所述的半导体存储器的形成方法,其特征在于,

5.如权利要求2所述的半导体存储器的形成方法,其特征在于,

6.如权利要求1所述的半导体存储器的形成方法,其特征在于,

7.如权利要求6所述的半导体存储器的形成方法,其特征在于,

8.如权利要求7所述的半导体存储器的形成方法,其特征在于,

9.一种半导体存储器,其特征在于,包括:

10.如权利要求9所述的半导体存储器,其特征在于,

技术总结

本公开提供一种半导体存储器及其形成方法,能降低位线之间的寄生电容,提升半导体存储器的性能。半导体存储器的形成方法包括如下步骤:提供半导体衬底,在所述半导体衬底内形成间隔排列的多个位线接触部的步骤;在所述半导体衬底上形成与多个所述位线接触部分别接触的多条位线的步骤;形成至少覆盖于所述位线的侧壁的位线间隔层,并在所述位线间隔层内形成气隙的步骤;以及形成盖帽层以封闭所述气隙的步骤。

技术研发人员:郑明勋

受保护的技术使用者:东芯半导体股份有限公司

技术研发日:

技术公布日:2024/5/12

- 还没有人留言评论。精彩留言会获得点赞!