压缩比可调的模拟信息转换电路、芯片和设备

本发明属于混合信号集成电路设计,具体涉及一种基于压缩感知的模拟信息转换电路、芯片和设备。

背景技术:

1、随着压缩感知理论的成熟,越来越多的电路设计人员被吸引到这项技术的实际应用和硬件实现上,为了解决从连续信号直接得到离散观测点的问题,saini kirolos等人提出了一套将压缩采样应用于模拟信号的解决方案,它摒弃了传统压缩系统先以奈奎斯特采样速率采样再压缩的方法,而是边采样边压缩,即实现的不再是模拟数字转换器(analog-to-digital converter,adc),而是模拟信息转换器(analog-to-information convertor,aic),模拟信息转换器无须将模拟信号数字化,可直接采样模拟信号。

2、目前的模拟信息转换器架构可分为四类:随机解调器(random demodulator,rd),随机调制预积分器(random-modulation pre-integrator,rmpi),调制宽带转换器(modulated wideband converter,mwc)和非均匀采样器(non-uniform sampler,nus)。然而,随机调制预积分器(rmpi)和调制宽带转换器(mwc)架构为每个信号路径都配置一个adc的方案会占用过大的芯片面积。非均匀采样器(nus)可能无法检测到信号中包含的短持续时间脉冲,导致信息丢失,应用范围和灵活性有限。随机解调器(rd)的实现方案通常涉及用于连续时间积分(或低通滤波)的有源放大器,由于放大器的工作电流仍然受到信号带宽的限制,因此前端的总功耗难以降低。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种。本发明要解决的技术问题通过以下技术方案实现:

2、第一方面,本发明提供了一种压缩比可调的模拟信息转换电路,包括:

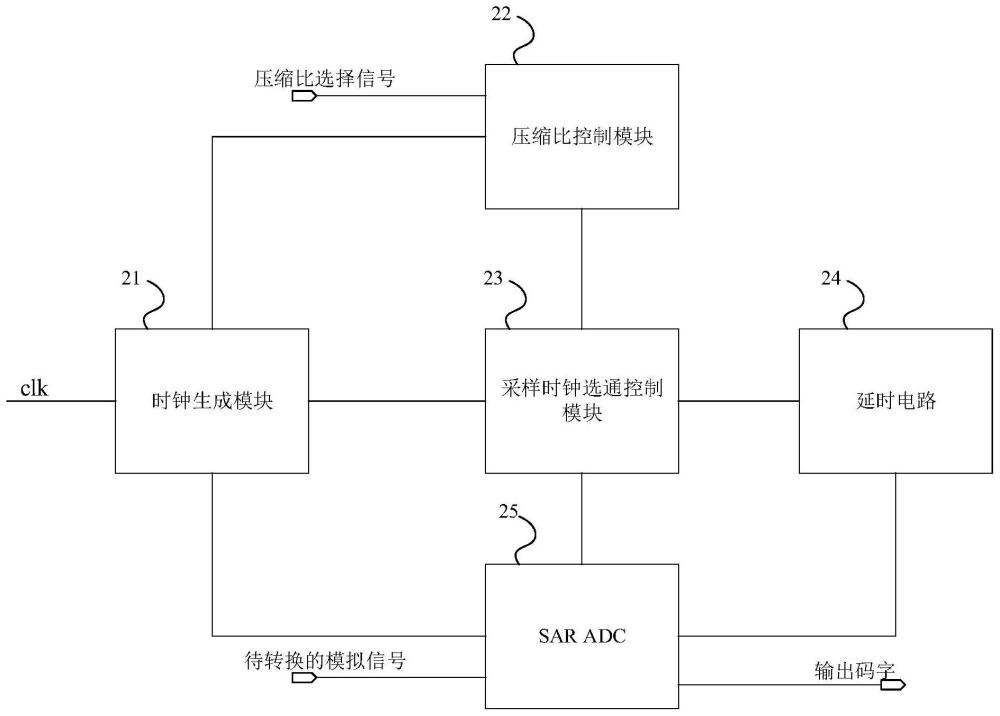

3、时钟生成模块、压缩比控制模块、采样时钟选通控制模块、延时电路、sar adc;

4、时钟生成模块的第一输入端接时钟信号clk,时钟生成模块的第一输出端与采样时钟选通控制模块的第一输入端连接,第二输出端与sar adc的第四输入端连接,第三输出端与压缩比控制模块的第一输出端连接;

5、采样时钟选通控制模块的第二输入端与压缩比控制模块的第二输出端连接,采样时钟选通控制模块的输出端分别与延时电路的输入端和sar adc的第一输入端连接;

6、延时电路的输出端与sar adc的第二输入端连接;

7、sar adc的第三输入端为信号输入端,接待转换的模拟信号,sar adc的输出端为压缩比可调的模拟信息转换电路的输出端,输出待转换的模拟信号所对应的码字;

8、压缩比控制模块的输入端接外部输入的压缩比选择信号;

9、压缩比控制模块,用于根据外部输入的压缩比选择信号,生成第一控制信号和第二控制信号;

10、时钟生成模块,用于根据时钟信号clk以及第一控制信号,生成量化时钟信号和至少一路第一采样时钟信号;

11、采样时钟选通控制模块,用于根据第二控制信号和各第一采样时钟信号,生成至少一路第二采样时钟信号;

12、延时模块,用于对各第二采样时钟信号进行延时操作,生成相应的第三采样时钟信号;

13、sar adc模块,用于根据各第二采样时钟信号、各第三采样信号、量化时钟信号对待转换的模拟信号进行模拟数字转换,得到相应的码字。

14、第二方面,本发明提供了一种芯片,包括如第一方面所提供的任一压缩比可调的模拟信息转换电路。

15、第二方面,本发明提供了一种电子设备,包括如第二方面所提供的芯片。

16、本发明的有益效果:

17、本发明提供的压缩比可调的模拟信息转换电路、芯片和设备,通过直接将压缩感知嵌入到sar adc中,利用sar adc中开关电容无源采样网络的特点,将乘法和求和都整合到sar adc的开关电容采样网络中,以离散时间求和取代连续时间积分。无源采样网络和电路结构复用降低了电路的功耗和面积。

18、以下将结合附图及实施例对本发明做进一步详细说明。

技术特征:

1.一种压缩比可调的模拟信息转换电路,其特征在于,包括:

2.根据权利要求1所述的电路,其特征在于,所述sar adc,包括:

3.根据权利要求2所述的电路,其特征在于,所述信号极性转换单元,包括:

4.根据权利要求3所述的电路,其特征在于,子电容阵列,包括:依次连接的n个电容单元,n为大于或等于1的正整数;

5.根据权利要求2-4任一所述的电路,其特征在于,所述时钟生成模块,包括:

6.根据权利要求5所述的电路,其特征在于,所述第一时钟生成单元,包括:

7.根据权利要求5所述的电路,其特征在于,所述量化时钟生成单元,包括:

8.根据权利要求6或7所述的电路,其特征在于,所述时钟选通模块,包括:

9.一种芯片,其特征在于,包括如权利要求1-8任一所述的压缩比可调的模拟信息转换电路。

10.一种电子设备,其特征在于,包括如权利要求9所述的芯片。

技术总结

本发明提供了一种压缩比可调的模拟信息转换电路、芯片和设备,包括:时钟生成模块、压缩比控制模块、采样时钟选通控制模块、延时电路、SAR ADC;时钟生成模块分别与时钟信号clk、采样时钟选通控制模块、SAR ADC、压缩比控制模块连接;采样时钟选通控制模块还与压缩比控制模块、延时电路的输入端和SAR ADC连接;延时电路还与SAR ADC连接;SAR ADC的第三输入端为信号输入端,接待转换的模拟信号,SAR ADC的输出端为压缩比可调的模拟信息转换电路的输出端,输出待转换的模拟信号所对应的码字;压缩比控制模块还接外部输入的压缩比选择信号,该电路通过无源采样网络和电路结构复用降低了电路的功耗和面积。

技术研发人员:靳刚,白志威,汤华莲,刘伟峰,包军林,李登超,李振荣

受保护的技术使用者:西安电子科技大学

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!