一种具有高输入阻抗的电容斩波仪表放大器

本发明涉及微电信号放大技术,尤其涉及一种具有高输入阻抗的电容斩波仪表放大器。

背景技术:

1、生物仪表放大器是将生物电位读出的重要部分,重要的生物电位包括了心电图、脑电图。通常生物电位是低频低振幅信号,频率为几赫兹至几百赫兹,幅度在几十微伏至几毫伏。低频特性通常与1/f噪声重叠,为了缓解这种情况,仪器放大器会采用斩波技术,可以有效的降低仪表放大器的噪声。然而,加入斩波技术会使得电极偏移(eos)会调制到高频,从而干扰输出,可以在电路中集成直流伺服环路(dsl)构建高通转角频率去抑制电极偏移。dsl通常由积分器组成,要构建一个较低的高通转角频率,会要求积分器中的电阻极其大,并且要求电阻的稳定性要好。另外在电容耦合仪表放大器中加入斩波技术,会引起仪表放大器的输入阻抗急剧下降。

技术实现思路

1、本发明目的在于提供一种具有高输入阻抗的电容斩波仪表放大器,以解决上述现有技术存在的问题。

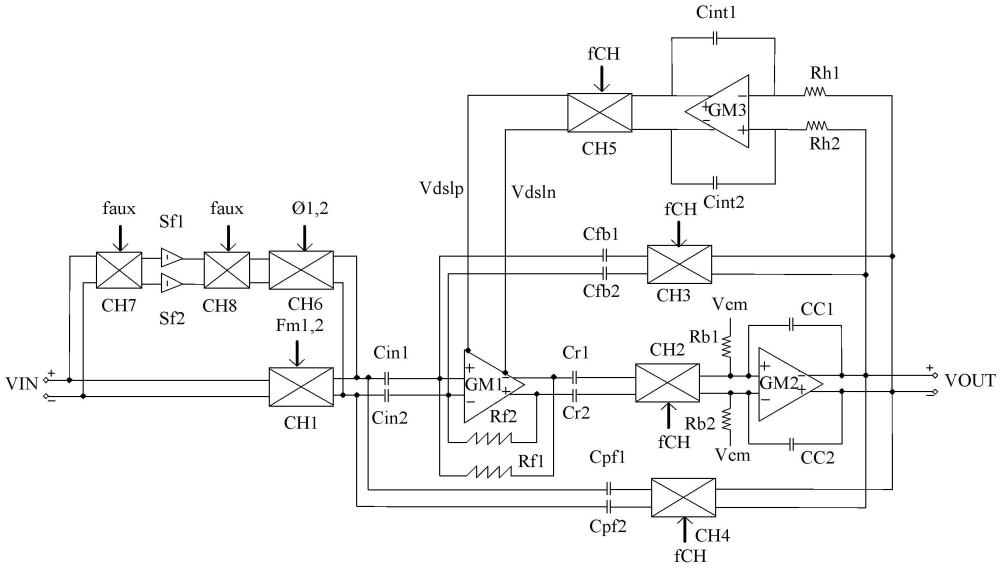

2、本发明中所述一种具有高输入阻抗的电容斩波仪表放大器,在最前端的斩波调节器两端并联一路阻抗提升辅助回路,以在所述斩波调节器的调节信号非交叠区间对斩波调节器后端的输入电容进行预充电。

3、具体结构如下:

4、差分输入信号vin的正相信号依次经过第七斩波调节器正相输入端、第一源跟随器、第八斩波调节器正相输入端、第六斩波调节器正相输入端后连接第一输入电容上极板,以及经过第一斩波调节器正相输入端后连接第一输入电容上极板;第一输入电容下极板连接第一运算放大器正相输入端;第一运算放大器正相输出端分别串接第一反馈电阻后连接第一运算放大器反相输入端,以及串接第一纹波抑制电容后连接第二斩波调节器正相输入端;第二斩波调节器正相输出端分别连接第二运算放大器正相输入端,以及串接第一mos伪电阻后连接共模电平;第二运算放大器正相输出端作为差分输出信号vout的正相输出端,以及串联第一密勒电容后连接第二运算放大器反相输入端;第三斩波调节器正相输入端连接第二运算放大器正相输出端,第三斩波调节器正相输出端串接第一负反馈电容后连接第一运算放大器正相输入端;第三运算放大器反相输入端串接第一逻辑门伪电阻后连接第二运算放大器正相输出端,第三运算放大器正相输出端连接第五斩波调节器正相输入端,第五斩波调节器正相输出端连接第一运算放大器正相高频输入端;第四斩波调节器正相输入端连接第二运算放大器正相输出端,第四斩波调节器正相输出端串接第一正反馈电容后连接第一输入电容上极板;第三运算放大器的反相输入端与第三运算放大器的第三运算放大器的正相输出端之间串接第一积分电容;

5、差分输入信号vin的反相信号依次经过第七斩波调节器反相输入端、第二源跟随器、第八斩波调节器反相输入端、第六斩波调节器反相输入端后连接第二输入电容上极板,以及经过第一斩波调节器反相输入端后连接第二输入电容上极板;第二输入电容下极板连接第一运算放大器反相输入端;第一运算放大器反相输出端分别串接第二反馈电阻后连接第一运算放大器正相输入端,以及串接第二纹波抑制电容后连接第二斩波调节器反相输入端;第二斩波调节器反相输出端分别连接第二运算放大器反相输入端,以及串接第二mos伪电阻后连接共模电平;第二运算放大器反相输出端作为差分输出信号vout的反相输出端,以及串联第二密勒电容后连接第二运算放大器正相输入端;第三斩波调节器反相输入端连接第二运算放大器反相输出端,第三斩波调节器反相输出端串接第二负反馈电容后连接第一运算放大器反相输入端;第三运算放大器正相输入端串接第二逻辑门伪电阻后连接第二运算放大器反相输出端,第三运算放大器反相输出端连接第五斩波调节器反相输入端,第五斩波调节器反相输出端连接第一运算放大器反相高频输入端;第四斩波调节器反相输入端连接第二运算放大器反相输出端,第四斩波调节器反相输出端串接第二正反馈电容后连接第二输入电容上极板;第三运算放大器的正相输入端与第三运算放大器的第三运算放大器的反相输出端之间串接第二积分电容。

6、所述第一运算放大器具体结构如下:

7、第七pmos管源极连接vdd,第七pmos管漏极分别连接第一pmos管的源极和第二pmos管的源极,第七pmos管栅极连接第五偏置电压;

8、第一pmos管漏极连接第三nmos管漏极,第一pmos管栅极作为第一运算放大器正相输入端;

9、第二pmos管漏极连接第四nmos管漏极,第二pmos管栅极作为第一运算放大器反相输入端;

10、第三pmos管源极连接vdd,第三pmos管漏极连接第五pmos管源极并同时作为第一运算放大器正向高频输入端,第三pmos管栅极连接第四pmos管栅极并同时连接第一偏置电压;

11、第四pmos管源极连接vdd,第四pmos管漏极连接第六pmos管源极并同时作为第一运算放大器反向高频输入端;

12、第五pmos管漏极连接第一nmos管漏极并同时作为第一运算放大器反相输出端,第五pmos管栅极连接第六pmos管栅极并同时连接第二偏置电压;

13、第六pmos管漏极连接第二nmos管漏极并同时作为第一运算放大器正相输出端;

14、第一nmos管源极连接第三nmos管漏极,第一nmos管栅极连接第二nmos管栅极并同时连接第三偏置电压;

15、第二nmos管源极连接第四nmos管漏极;

16、第三nmos管源极和第四nmos管源极共地。第三nmos管栅极连接第四nmos管栅极并同时连接第四偏置电压。

17、所述第一mos伪电阻和第二mos伪电阻结构相同,均分别由背靠背mos管构成。

18、所述第一逻辑门伪电阻和第二逻辑门伪电阻结构相同,均分别由若干串联的传输门构成,并且传输干路通过第一电容接地。

19、本发明中所述一种具有高输入阻抗的电容斩波仪表放大器,其优点在于,将斩波电路、运算放大电路、纹波抑制电容、阻抗提升辅助回路及内嵌式直流伺服回路相结合,能够极大的提升仪表放大器的输入阻抗。同时在保持低功耗的前提下,能有效的降低仪表放大器的等效输入噪声。并且在直流伺服回路中,采用传输门电路做伪电阻,可以有效的构建一个较低的高通转角频率去抑制电极偏移。

技术特征:

1.一种具有高输入阻抗的电容斩波仪表放大器,其特征在于,在最前端的斩波调节器两端并联一路阻抗提升辅助回路,以在所述斩波调节器的调节信号非交叠区间对斩波调节器后端的输入电容进行预充电。

2.根据权利要求1所述一种具有高输入阻抗的电容斩波仪表放大器,其特征在于,具体结构如下:

3.根据权利要求2所述一种具有高输入阻抗的电容斩波仪表放大器,其特征在于,所述第一运算放大器(gm1)具体结构如下:

4.根据权利要求2所述一种具有高输入阻抗的电容斩波仪表放大器,其特征在于,所述第一mos伪电阻(rb1)和第二mos伪电阻(rb2)结构相同,均分别由背靠背mos管构成。

5.根据权利要求2所述一种具有高输入阻抗的电容斩波仪表放大器,其特征在于,所述第一逻辑门伪电阻(rh1)和第二逻辑门伪电阻(rh2)结构相同,均分别由若干串联的传输门构成,并且传输干路通过第一电容(c1)接地。

技术总结

本发明公开了一种具有高输入阻抗的电容斩波仪表放大器,涉及微电信号放大技术,针对现有技术中输入阻抗急剧下降的问题提出本方案。在最前端的斩波调节器两端并联一路阻抗提升辅助回路,以在所述斩波调节器的调节信号非交叠区间对斩波调节器后端的输入电容进行预充电。优点在于,将斩波电路、运算放大电路、纹波抑制电容、阻抗提升辅助回路及内嵌式直流伺服回路相结合,能够极大的提升仪表放大器的输入阻抗。同时在保持低功耗的前提下,能有效的降低仪表放大器的等效输入噪声。并且在直流伺服回路中,采用传输门电路做伪电阻,可以有效的构建一个较低的高通转角频率去抑制电极偏移。

技术研发人员:姚翊锋,李志坚,吴朝晖,李斌

受保护的技术使用者:华南理工大学

技术研发日:

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!