成像电路的制作方法

[0001]

本发明总体涉及成像电路,更具体地,涉及在堆叠于其他图像读出/信号处理晶片上的晶片上具有图像传感器像素的用于执行模拟域像素级特征提取的成像设备。

背景技术:

[0002]

图像传感器常常在电子设备诸如移动电话、相机和计算机中用来捕获图像。在典型布置方式中,图像传感器包括被布置成像素行和像素列的图像像素阵列。可将电路耦接至每个像素列以从图像像素读出图像信号。

[0003]

成像系统可实施卷积神经网络(cnn)以执行特征提取(即检测图像中的一个或多个对象、形状、边缘或其他场景信息)。可在具有比整个像素阵列较低的分辨率的较小的感兴趣区域(roi)中执行特征提取。通常,较低分辨率roi中的模拟像素值将被读出、数字化并存储,以进行特征提取和卷积步骤的后续处理。

技术实现要素:

[0004]

根据第一方面,提供一种成像电路,所述成像电路包括:第一像素,所述第一像素被配置为输出第一像素值;第二像素,所述第二像素被配置为输出第二像素值;第一可调电路,所述第一可调电路被配置为向所述第一像素值施加第一加权因子以产生第一加权像素值;第二可调电路,所述第二可调电路被配置为向所述第二像素值施加第二加权因子以产生第二加权像素值;以及输出电路,所述输出电路被配置为将所述第一加权像素值和所述第二加权像素值组合以产生模拟输出电压。

[0005]

根据第二方面,提供一种成像电路,所述成像电路包括:第一像素,所述第一像素具有第一源极跟随器漏极端子,其中所述第一像素被配置为输出第一像素值;第二像素,所述第二像素具有第二源极跟随器漏极端子,其中所述第二像素被配置为输出第二像素值;以及电流镜电路,所述电流镜电路具有用于向所述第一像素值施加第一权重的第一组可调开关和用于向所述第二像素值施加第二权重的第二组可调开关。

[0006]

根据第三方面,提供一种成像电路,所述成像电路包括:第一组有源像素,所述第一组有源像素被配置为产生有源像素值;加权电路,所述加权电路被配置为从所述第一组有源像素接收所述有源像素值并产生对应的加权像素值;输出电路,所述输出电路被配置为接收和组合所述加权像素值以产生对应的输出电压;以及第二组空闲像素,所述第二组空闲像素被配置为临时存储所述输出电压以避免必须在数字域中存储所述输出电压。

附图说明

[0007]

图1是根据一些实施方案的具有用于使用图像像素阵列来捕获图像的图像传感器和处理电路的例示性电子设备的图。

[0008]

图2是根据实施方案的示出的堆叠成像系统的图。

[0009]

图3是根据实施方案的耦接至数字处理电路和模拟处理电路的例示性图像传感器

阵列的图。

[0010]

图4a是示出根据实施方案的图像像素如何可经由各种开关网络被连接到特定的感兴趣区域(roi)的图。

[0011]

图4b是根据实施方案的例示性roi单元格的图。

[0012]

图4c是示出根据实施方案的如何可经由对角路由线连接roi的图。

[0013]

图5是示出根据实施方案的如何可将卷积核应用于roi以提取特征的图。

[0014]

图6a是根据实施方案的用于支持例示性充电模式操作的像素读出结构的图。

[0015]

图6b是根据实施方案的用于支持暗像素选项以允许多个核的非破坏性处理的像素读出结构的图。

[0016]

图6c是根据实施方案的用于操作图6b的像素电路的例示性步骤的流程图。

[0017]

图7a是示出根据实施方案的使用可调电容器的充电模式特征提取电路的一种合适实施方式的图。

[0018]

图7b是根据实施方案的用于操作图7a所示的充电模式特征提取电路的例示性步骤的流程图。

[0019]

图7c是根据实施方案的示出用于操作图7a所示的电路的相关信号的时序图。

[0020]

图7d是示出根据实施方案的中间模拟结果可如何被临时存储在空闲像素中的图。

[0021]

图8a是示出根据实施方案的使用可调电阻器的充电模式特征提取电路的另一合适实施方式的图。

[0022]

图8b是示出根据实施方案的和/差电荷积分器块的一种合适实施方式的图。

[0023]

图8c是示出根据实施方案的可如何选择性地使用可调电流镜电路来提供不同权重的图。

[0024]

图9a是示出根据实施方案的使用耦接至开关电容积分器的可调电阻器的充电模式特征提取电路的又一合适实施方式的图。

[0025]

图9b是根据实施方案的用于操作图9a所示的充电模式特征提取电路的例示性步骤的流程图。

[0026]

图10是示出根据实施方案的使用差分放大器电路来计算不同像素组的值之间的差的充电模式特征提取电路的又一合适实施方式的图。

具体实施方式

[0027]

电子设备诸如数字相机、计算机、移动电话和其他电子设备可包括图像传感器,该图像传感器收集入射光以捕获图像。图像传感器可包括图像像素阵列。图像传感器中的像素可包括光敏元件,诸如将入射光转换成图像信号的光电二极管。图像传感器可具有任何数量(例如,数百或数千或更多)的像素。典型图像传感器可例如具有数十万或数百万像素(例如,数兆像素)。图像传感器可包括控制电路(诸如,用于操作图像像素的电路)和用于读出图像信号的读出电路,该图像信号与光敏元件所生成的电荷相对应。

[0028]

图1为示例性成像系统(诸如,电子设备)的示意图,该成像系统使用图像传感器捕获图像。图1的电子设备10可为便捷式电子设备,诸如相机、蜂窝电话、平板计算机、网络相机、摄像机、视频监控系统、机动车成像系统、具有成像能力的视频游戏系统或者捕获数字图像数据的任何其他所需的成像系统或设备。相机模块12可用于将入射光转换成数字图像

数据。相机模块12可包括一个或多个透镜14以及一个或多个对应图像传感器16。透镜14可包括固定透镜和/或可调透镜,并且可包括形成于图像传感器16的成像表面上的微透镜。在图像捕获操作期间,可通过透镜14将来自场景的光聚焦到图像传感器16上。图像传感器16可包括用于将模拟像素数据转换成要提供给存储和处理电路18的对应的数字图像数据的电路。如果需要,相机模块12可设置有透镜14的阵列和对应图像传感器16的阵列。

[0029]

存储和处理电路18可包括一个或多个集成电路(例如,图像处理电路、微处理器、存储设备诸如随机存取存储器和非易失性存储器等),并且可使用与相机模块12分开和/或形成相机模块12的一部分的部件(例如,形成包括图像传感器16的集成电路或者与图像传感器16相关联的模块12内的集成电路的一部分的电路)来实施。可使用处理电路18处理和存储已被相机模块12捕获的图像数据(例如,使用处理电路18上的图像处理引擎、使用处理电路18上的成像模式选择引擎等)。可根据需要使用耦接至处理电路18的有线通信路径和/或无线通信路径将处理后的图像数据提供给外部设备(例如,计算机、外部显示器或其他设备)。

[0030]

根据一个实施方案,可以处理模拟域中的像素值的组以提取与场景中的对象相关联的特征。像素信息没有被数字化到的低分辨率的感兴趣区域。使用此模拟实施方式,可(例如)在卷积神经网络的多个步骤中处理从像素阵列提取的特征信息,以识别用于系统的场景信息,然后可使用该场景信息来决定是否以该场景区域中更高的分辨率输出像素信息。

[0031]

可利用管芯堆叠来允许像素阵列连接到对应的感兴趣区域(roi)处理器,以实现有效的模拟域特征提取(例如,检测感兴趣的对象特征和未通过正常数字信号处理路径以全分辨率读出的阵列区域的时间变化)。所提取的特征可被临时存储在模拟域中,其可用于检查特征值随时间的变化并检测与场景中的对象有关的关键特征的变化。图2是示出的堆叠的成像系统200的图。如图2所示,系统200可包括作为顶部管芯的图像传感器管芯202、作为底部管芯的数字信号处理器管芯206以及竖直堆叠在顶部管芯202和底部管芯206之间的模拟特征提取管芯204。图像传感器像素阵列驻留在顶部图像传感器管芯202内;正常数字读出电路位于底部管芯206内;并且模拟域特征提取电路形成在中间管芯204内。如果需要,也可使用堆叠各种成像器管芯的其他方式。

[0032]

图3是耦接至数字处理电路和模拟处理电路的例示性图像传感器阵列302的图。数字信号处理电路由虚线框320描绘,虚线框包括被配置为经由行控制线312驱动阵列302内的所有像素行的全局行解码器310、被配置为通过正常读出路径316经由每个像素列接收像素值的模数转换器(adc)块314和传感器控制器318。这些数字信号处理电路320可驻留在底部管芯206(参见图2)内。

[0033]

图像像素阵列302可形成在顶部图像传感器管芯202上。像素阵列302可被组织成有时被称为“图块”304的组。每个图块304可例如包括256

×

256个图像传感器像素。该图块大小仅是例示性的。通常,每个图块304可具有任何合适尺寸的正方形、矩形或不规则形状(即,图块304可包括任何合适数量的像素)。

[0034]

每个图块304可对应于用于执行特征提取的相应的“感兴趣区域”(roi)。单独的roi处理器330可形成在每个图块304下方的模拟管芯204中。每个roi处理器330可包括行移位器寄存器332、列移位寄存器336以及如会聚线336表示的用于选择性地组合来自多个相

邻像素的值的行控制和开关矩阵电路。从每个roi处理器330读出的信号可被馈送到模拟处理和多路复用电路340并被提供给电路342。电路342可包括模拟滤波器、比较器、高速adc阵列等。传感器控制器318可将信号发送到roi控制器344,该roi控制器控制如何经由roi处理器330读出像素。例如,roi控制器344可以任选地控制像素复位、像素电荷转移、像素行选择、像素双转换增益模式、全局读出路径使能信号、本地读出路径使能信号、用于确定模拟读出方向的开关、roi快门控制等。电路330、340、342和344可全部形成在模拟管芯204内。

[0035]

以这种方式配置的成像系统可支持内容感知感测。模拟读出路径支持快速扫描以进行形状/特征检测、非破坏性强度阈值、时间事件,并且还可使用板载视觉智能组件来处理形状。高速roi读出路径还可允许数字累加和突发读出,而不影响正常的帧读出。基于该场景部分的重要性,这种内容感知传感器架构以不同的分辨率(空间、时间、位深度)读出不同区域。智能传感器用于监测未以全分辨率读出的图像区域中的活动/事件,以确定何时唤醒该区域以进行更高分辨率的处理。模拟特征提取支持监测那些特定感兴趣区域中的活动,而不进入数字域。由于模拟特征提取不需要通过adc进行处理,因此可节省大量功率。

[0036]

图4a是示出可如何经由各种开关网络将图像像素连接到特定感兴趣区域(roi)的图。如图4a所示,图像传感器像素诸如像素400可包括经由电荷转移晶体管耦接至浮动扩散节点fd的光电二极管pd、耦接在fd节点与重置漏极节点rst_d之间的重置晶体管、双转换增益(dcg)晶体管(具有连接到fd节点的第一端子和电浮置的第二端子)、源极跟随器晶体管(具有漏极节点sf_d、连接到fd节点的栅极端子、经由对应的行选择晶体管耦接至roi像素输出线的源极节点)。像素404的部分402可以另选地包括共享单个浮动扩散节点的多个光电二极管,如配置404所示。

[0037]

在图4a的示例中,8

×

8像素簇内的每个重置漏极节点rst_d可耦接至一组重置漏极开关420。这仅仅是示例性的。通常,共享开关420的像素簇可具有任何合适的大小和尺寸。开关420可包括选择性地将rst_d连接到正电源电压vaa的重置漏极功率使能开关、选择性地将rst_d连接到对应的水平路由线routeh的水平合并开关binh、选择性地将rst_d连接到对应的竖直路由线routev的竖直合并开关binv等。以这种方式配置的开关网络420使得能够连接到电源、合并来自其他像素的电荷、进行焦平面电荷处理。

[0038]

像素簇内的每个源极跟随器漏极节点sf_d也可耦接至一组sf漏极开关430。开关网络430可包括选择性地将sf_d连接到电源电压vaa的sf漏极功率使能开关pwr_en_sfd、选择性地将sf_d连接到水平线voutp_h的开关hx、选择性地将sf_d连接到竖直线voutp_v的开关vx、选择性地将sf_d连接到第一对角线voutp_d1的开关dx、选择性地将sf_d连接到第二对角线voutp_d2的开关ex等。以这种方式配置的开关430使得能够对来自多个像素源极跟随器的电流进行转向,以允许求和/求差以检测形状和边缘以及连接到可变电源。

[0039]

像素簇内的每个像素输出线roi_pix_out(y)也可耦接至一组像素输出开关410。开关网络410可包括用于选择性地将像素输出线连接到全局列输出总线pix_out_col(y)的第一开关global_roix_out_en和用于选择性地将像素输出线连接到可在不同列之间共享的本地roi串行输出总线serial_pix_out_roix的第二本地开关local_roix_col(y)。以此方式配置,开关410将来自roi的每个像素输出连接到用于读出的标准全局输出总线中的一个、连接到串行读出总线以形成用于检测形状/边缘的电路、连接到高速本地读出信号链或可变电源。

[0040]

图4b是例示性roi单元格450的图。在图4b的示例中,每个roi单元格450可包括共享结合图4a所描述的各种开关网络的四个8

×

8像素簇452。在图4b的示例中,每个簇452可具有不同数量的sf_d开关。例如,左上簇可耦接至五个sf_d开关,而右上簇仅可耦接至三个sf_d开关。这仅仅是示例性的。如果需要,每个簇452可耦接至任何合适数量的sf_d开关。在图4b的示例中,各个簇452可耦接至共享的水平和竖直合并开关。此外,沿着每一列的簇可耦接至相应的全局输出总线,而单元格450中的所有簇可耦接至公共的本地roi串行输出总线。

[0041]

图4c是示出如何可经由对角路由线来连接roi的图。经由第一组对角读出线读出的信号可产生第一输出电流ioutp_d,而经由第二组对角读出线读出的信号可产生第二输出电流ioutn_d。这些输出电流可经由本地roi sf_d开关(例如,图4a中的开关420)或经由本地roi rst_d开关(例如,图4a中的开关430)读出。可使不同的对角线能够检测不同的形状(例如,对角线边缘)。

[0042]

图5是示出可如何将卷积核502应用于图块304或roi以提取特征506的图。卷积核502可包括权重的集合。卷积核502可应用于在roi 304上滑动的对应窗口500。在图5的示例中,核502被示为3

×

3矩阵。不过,这仅仅是示例性的。核502可以是5x5的权重矩阵,也可以是任何适当大小或尺寸的矩阵。每个核窗口500执行模拟乘法累加(mac)运算以获得产生的卷积特征506。多个卷积特征506可被组合成具有相同大小或者任选地小于图块304的特征图504。也可实施产生cnn层的其他方式。

[0043]

图6a是根据实施方案的用于支持例示性充电模式操作的像素读出结构的图。可以在不改变图像像素电路的情况下发生模拟电平特征提取,并且由将连接配置到像素阵列中的roi控制器来启用模拟电平特征提取(例如,参见图4a中的开关410、420和430)。如图6a所示,第一像素400-a可被配置为经由第一本地/串行读出总线602将第一像素值输出至第一可变电容器cin1,而第二像素400-b可被配置为经由第二本地/串行读出总线604将第二像素值输出至第二可变电容器cin2。像素400-a和400-b两者的sf_d节点可经由路径606耦接至共享输出电容器cout。电容器cin1针对核操作对像素400-a的值加权,而电容器cin2针对核操作对像素400-b的值加权。可以根据核操作所需的期望权重来调整电容器cin1和cin2的电容。电容器cout、cin1和cin2可形成在每个roi处理器330的外围或中间模拟管芯的外围(见图3)。

[0044]

在充电模式操作期间,存储在浮动扩散节点上的像素信号是假定的。基于关联的fd电压,电容器cout可预充电到高电压,而电容器cin1和cin2则被充电。然后可关断对电容器cout的预充电,并重置fd节点。因此,电容器cout将被放电与fd信号电平乘以与该像素相连的cin电容器大小成比例的量。最终的加权像素值将在cout处求和。如果需要,可使用第二cout电容器和纵横开关(例如,参见图7a)来实施负权重系数(如果需要)。神经元输出(例如,卷积特征)的激活通过施加到cout电容器的偏移来启用。如果需要,可以通过随后的模拟处理来启用负值(“relu”)的非线性钳位,在该模拟处理中,该值存储在fd节点上,并限制为像素fd重置电平。然后可经由rst_d连接将模拟值存储回像素阵列中。

[0045]

图6b是用于支持暗像素选项以允许多个核的非破坏性处理的像素读出结构的图。如图6b所示,电容器cin1也可经由路径602耦接至第一暗参考像素400-a',并且电容器cin2也可经由路径604耦接至第二暗参考像素400-b'。这些“暗”参考像素可以是单独的光学黑

色像素。两个暗参考像素中的sf_d端子都可以经由路径606连接到电容器cout。代替关断对cout的预充电和重置fd节点,可在将cin1、cin2和cout连接到暗参考像素时关断对cout的预充电。在通过像素400-a和400-b给cin1/2充电后,多个暗像素可同时连接到本地/串行读出总线。在另一合适的布置方式中,单个暗像素可串行连接到每个本地读出总线。在又一合适的布置方式中,可使用中间模拟管芯将预定的参考电压供应给sf_d节点。

[0046]

每个暗参考像素都应将它们的fd节点重置为预定的重置电压电平。这些“黑色”参考像素的重置晶体管应被始终导通或周期性地被施加脉冲。此黑色像素选项允许在到cout的加权电荷转移时间期间设置全局重置电平,以允许将该电容器重新用于(多个核的)多个加权处理,并允许(对于多个核)对fd节点进行多次非破坏性感测。在这种情况下,像素仅将cin值充电到初始预充电值,然后连接到cout和像素输出线的全局暗像素将每个cin充电到重置电平。以这种方式操作的暗参考像素有时可被称为暗像素参考驱动器。由于源极跟随器晶体管上的阈值电压变化,这可能导致固定模式噪声(fpn)略微升高,这对于具有低位分辨率权重的应用是可以接受的。

[0047]

图6c是用于操作图6b中所示的像素电路的例示性步骤的流程图。在步骤680处,电容器cout可被重置为高电压电平。在步骤682处,可导通行选择晶体管,以将对应的cin充电到由相关的浮动扩散节点确定的对应的输出电平(例如,像素400-a的fd节点可用于给cin1充电,而像素400-b的fd节点可用于给cin2充电)。

[0048]

在步骤684处,可使行选择晶体管关断。在步骤686处,可根据暗像素重置电平来接通select_ref_level开关,以进一步对对应的cin充电(例如,可通过使select_ref_level1生效来导通第一暗参考像素的行选择晶体管以对cin1充电,而可通过使select_ref_level2生效来导通第二暗参考像素的行选择晶体管以对cin2充电)。在步骤688处,可读出并捕获最终的cout值(每当cin的拉电荷中的任何一个远离cout时,该cout值应该已经从重置电平减小)。在步骤690处,可任选地调节cin电容器以施加不同的权重而不破坏fd节点处的像素值。然后,处理可以如路径692所示循环回到步骤680,而不覆写或重置fd节点。

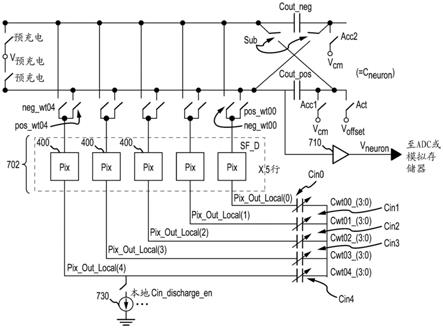

[0049]

图7a是示出使用可调电容器的充电模式特征提取电路的一个合适的实施方式的图。如图7a所示,部分702可表示具有5

×

5像素400的核窗口(作为示例)。窗口中的第一列像素经由本地roi串行输出总线pix_out_local(0)耦接至第一可调电容器组cin0;窗口中的第二列像素经由本地roi串行输出总线pix_out_local(1)耦接至第二可调电容器组cin1;窗口中的第三列像素经由本地roi串行输出总线pix_out_local(2)耦接至第三可调电容器组cin2;等等。通过选择性地使本地cin放电使能信号localcin_discharge_en生效,可使用耦接至电流吸收器730的对应下拉开关来对每个串行输出总线处的cin进行单独放电。这些各种电容器组可显示可调节电容值,可使用控制位cwtxx_(3:0)调整该可调节电容值。可存在任何适当数量的电容控制位,以提供期望电平来调整粒度。

[0050]

每一列核窗口702中的每个像素的sf_d节点可经由开关pos_wt选择性地耦接至正输出电容器cout_pos,并且可经由开关neg_wt选择性地耦接至负输出电容器cout_neg。电容器cout_pos和cout_neg可经由一对预充电开关被选择性地预充电到电压vprecharge。

[0051]

电容器cout_pos可经由开关acc1选择性地耦接至共模电压vcm。类似地,电容器cout_neg可经由开关acc2选择性地耦接至共模电压vcm。偏移电压voffset可仅经由开关act选择性地施加到电容器cout_pos。当期望执行求差/减法运算时,开关sub可都接通以交

叉耦接电容器cout_pos和cout_neg。这些各种开关可以是中间模拟管芯204上的外围电路。电容器cout_pos连接到缓冲器710,该缓冲器产生最终输出电压vneuron。电压vneuron可馈送到adc、模拟存储器以进行临时存储,或随后在数字或模拟域中进行其他处理以标记特征。

[0052]

以这种方式配置,图7a的电路可用于对模拟像素值阵列执行加权以及求和,而不事先进行adc转换。vneuron输出可等于(w*x+b),其中w是权重值,x是像素值,b是偏移。像素值的乘法累加(mac)运算是通过使用电容器比率来实现的,其中将多个结果相加在一起以产生最终的神经元结果。中间结果的模拟存储是通过将vneuron馈送回到当时未用于成像的空闲区域中的像素阵列fd节点中完成的(如结合图7d所述)。像素阵列中的模拟存储允许直接使用fd存储节点通过加权和激活功能(偏移)对神经元网络中的更多层进行处理。最终,将模拟特征处理的输出转换为数字值,以进行附加处理,以标记待用于理解场景内容的特征。通过存储来自先前特征提取操作的结果,该输出还可用于标记与感兴趣的对象相关的主要特征中的时间变化(例如,执行智能事件感测)。

[0053]

图7b的流程图中示出用于操作图7a的电路的示例性步骤。最初,可设置电容器权重值;像素行可连接到本地串行输出总线;并且假定像素信号存在于fd节点处。在步骤750处,在激活开关acc1和acc2以施加vcm的同时,通过接通预充电开关来对输出电容器cout_pos和cout_neg(可统称为cneuron)进行预充电。此后,可关断预充电开关,并以预充电水平对cneuron进行充电。

[0054]

在步骤752处,每个像素列可经由sf_d路径上的对应开关选择性地耦接至cout_pos或cout_neg。在步骤754处,可导通行选择晶体管,这使得本地roi串行输出总线能够对对应的cin电容器进行充电。在步骤756处,可在开关acc1和acc2保持接通的同时使行选择晶体管关断,使预充电开关关断。

[0055]

在步骤758处,可(例如,通过接通图6b中的开关select_ref_level)选择暗参考像素,以考虑像素重置电平来拉高cneuron。另选地,可重置fd节点。在步骤760处,可(例如,通过在关断开关acc1和acc2的同时首先对cin电容器进行预充电以避免破坏先前的cneuron值)读出相邻的图像像素。

[0056]

在步骤762处,开关acc2被关断,并且开关sub可被接通以执行减法(例如,从cout_pos去除cout_neg的贡献)。在步骤764处,断开开关acc1,并且接通开关act,以施加偏移电压voffset。在步骤766处,最终的vneuron值可由缓冲器710输出并且随后被捕获。这些步骤和各种相关信号的电压电平在图7c的时序图中示出。

[0057]

在时间t1处,可使给定的行选择信号生效以选择要读出的行(或者,如果需要,并行选择多个行,或者支持并行生成加权像素值)。在时间t2处,本地cin放电使能信号可被施加脉冲而变高,以使cin电容器临时放电。在时间t3处,预充电、acc1、acc2、pos_wt和neg_wt开关都接通,以开始为cin充电。在图7c的示例中,第0列、第1列和第2列被正加权(由激活开关pos_wt00/01/02的事实指示),而第3列和第4列被负加权(由激活开关neg_wt03/04的事实指示)。在此期间,对应的本地串行输出总线可充电到浮动扩散节点的电压减去源极跟随器晶体管的阈值电压(即v

fd0-v

th,sf

)。在时间t4处,预充电晶体管关断。

[0058]

在时间t5处,可选择暗参考像素以重置串行输出总线,如通过输出电压vneuron的下降所看到,该串行输出总线将电荷拉离cout并使cout放电。如上所述,使用暗参考像素执

行重置实施了非破坏性重置采样,而简单地重置像素(即,fd节点)本身将实施破坏性重置采样。在时间t6处,开关pos_wtxx和neg_wtxx关断以将像素与cout解耦。在时间t7处,可使行选择和重置信号失效。在时间t8处,开关acc2被关断。

[0059]

在时间t9处,可临时接通sub开关以执行减法(例如,获得存储在cout_pos上的电荷与存储在cout_neg上的电荷之差)。在时间t10处,关断开关acc1,同时接通开关act以施加voffset。在时间t11处,可关断开关act,并且此时,可读出并捕获vneuron。

[0060]

为了顺序处理多行,仅对cneuron进行一次预充电操作,并且cin电容器由sf_d节点连接到电源电压vaa的像素驱动,并且开关pos_wtxx和neg_wtxx均关断。对于神经网络中每一层结果,在模拟域中以这种方式使用无源电容器执行充电模式mac操作,通过避免了将数据移至常规数字存储器的需要而节省功率和面积。

[0061]

图7d是示出可如何将中间模拟结果临时存储在像素阵列的其他部分中的空闲像素中的图。因此,与使用数字域中的数字电路处理中间结果相反,用于存储中间结果的像素可用作模拟存储器。如图7d所示,缓冲器710(见图7a)可将输出vneuron驱动到模拟存储器上。除了帮助驱动vneuron外,缓冲器710还可提供附加功能,即将小于零伏的值钳位到0v或共模电压,以对中间结果执行非线性“relu”操作。电压vneuron可经由开关storage_result1选择性地耦接至第一空闲像素400-c1',经由开关storage_result2耦接至第二空闲像素400-b',并且经由开关storage_result3耦接至第三空闲像素400-a1。以这种方式布置,电压vneuron可被存储在像素阵列的临时空闲或未使用的fd节点上,这些fd节点经由相应的rst_d路径被访问。该重置漏极路径可与下降到每个像素列的电源线共享。具有共享的重置控制的像素组可利用重置漏极节点rst_d处的电容chold来保持模拟值,然后在准备好存储所有结果时将保持的电压存储到每个fd中。所存储的中间模拟结果可用于被模拟mac处理器进行后续处理。该模拟存储部分可以是像素阵列的时间多路复用部分,或可使用不需要捕获图像数据的roi图块。以这种方式存储在模拟域中的输出电压vneuron可在处理与不同权重集相关的信号、与神经网络中不同层相关的信号时使用,或者可执行其他类型的递归操作,同时避免了必须访问数字存储器(诸如底部数字管芯上的随机存取存储器)。换句话说,被读出的像素值不用于通过模数转换器的后续读出,而是可在数字域中被处理之前与附加的加权像素值组合。

[0062]

结合图6至图7描述的无源充电模式特征提取电路仅是例示性的,并不旨在限制本实施方案的范围。图8a是示出使用可调电阻器的另一合适的加权方案的图。如图8a所示,每个像素的像素输出线可耦接至相应的可调电阻器(例如,第一像素400-1可耦接至第一电阻器组rweight1,第二像素400-2可耦接至第二电阻器组rweight2,第三像素400-3可耦接至第三电阻器组rweight3等)。这些电阻器组的值可根据期望的核权重进行静态或动态调节。

[0063]

sf_d节点可耦接至产生输出vneuron的和/差电流/电荷积分器块802。图8b示出了积分器模块802的一种合适的实施方式。块802可包括电流镜像部分819和积分器部分820。电流镜电路819可包括用于将电流发送到像素阵列中的相应sf_d节点上的上拉晶体管810、具有经由对应的选择开关选择性地耦接至积分器820的给定大小的第一组电流镜像晶体管812。晶体管810和812的大小可相同或可不同。可使用开关电容器方案来实施积分器块820。积分器820可包括比较器822,该比较器具有被配置为接收共模输入电压vcm的第一(+)输入和耦接至不同电流镜像路径的第二(-)端子。共享积分电容器cint可使用开关p1或p2选择

性地交叉耦接在放大器822的输入/输出两端,或者可使用自动调零开关重置。

[0064]

根据另一种合适的布置方式,电阻器组可另选地实施为可变脉冲开关以控制总电荷吸收、权重的电阻性非易失性存储器阵列或者实施为仅在连接到sf_d节点的电流镜中施加权重的虚拟地端子(例如,参见图8c,使用块802',同时有选择地将本地串行输出总线分流到虚拟地以提供必要的电流路径)。如图8c所示,块802可包括电流镜部分819'和积分器部分820'。电流镜电路819'可包括用于将电流发送到像素阵列中的相应sf_d节点上的上拉晶体管810、具有经由开关sel_wta(2)选择性地耦接至积分器820的给定大小的第一组电流镜像晶体管812、具有经由开关sel_wta(1)选择性地耦接至积分器820的2倍给定大小的第二组电流镜像晶体管814、具有经由开关sel_wta(0)选择性地耦接至积分器820的4倍给定大小的第三组电流镜像晶体管816。可通过选择多个电流镜输出中的一个或多个电流镜输出(例如,通过配置各种加权开关)来设置每个像素列的权重。可以使用类似于已结合图8b描述的开关电容器方案来实施积分器块820',并且不需要详细重述。

[0065]

图9a是示出充电模式特征提取电路的又一合适实施方式的图。如图9a所示,rst_d和sf_d节点可耦接至其上提供vaa的电源端子902,并且像素输出线经由相应的加权电阻器耦接至积分器块920。不同于图8a、图8b和图8c的实施方案,图9a的实施方案具有代替耦接至sf_d端子而耦接至像素输出线的积分器块920。积分器块920可具有与已结合图8b描述的基本相同的结构。在图9a的示例中,像素400-1的列输出线经由开关select_wt1和第一可调电阻器组rweight1选择性地耦接至积分器920的输入;像素400-2的列输出线经由开关select_wt2和第二可调电阻器组rweight2选择性地耦接至积分器920的输入;像素400-3的列输出线经由开关select_wt3和第三可调电阻器组rweight3选择性地耦接至积分器920的输入;等等。参考电压vref(或一些其他偏移电压)可通过接通开关select_ref经由参考可调电阻器组rweight_ref选择性地施加到积分器块920的负输入。

[0066]

图9b示出了用于操作图9a的电路的例示性步骤。在步骤950处,在激活p1开关的同时,接通放大器上的自动调零开关。在此时间期间,p2开关关断,所有权重选择开关select_wtx被停用,这使电容器cint上的电荷调零,以确保将比较器的输入均设置为vcm。在步骤952处,自动调零开关关断。

[0067]

在步骤954处,行选择晶体管导通,所有正select_wt开关接通。在步骤956处,将访问与正权重相关联的fd节点上的像素充电信号持续一段时间,该段时间将允许积分电容器cint充电到与fd电压和rweight值成比例的电平。此后,正select_wt开关关断。

[0068]

在步骤958处,p1开关关断,而将p2开关接通以翻转积分电容器cint的极性,同时临时停止cint的充电。在步骤960处,行选择晶体管导通,所有负select_wt开关接通。在步骤962处,将访问与负权重相关联的fd节点上的像素充电信号持续一段时间,该段时间将允许积分电容器cint充电到与fd电压和rweight值成比例的电平。此后,负select_wt开关关断。

[0069]

在步骤964处,select_ref开关可启用持续一段时间,该段时间允许将偏移电压施加到cint持续一定时间或允许cint放电与所有像素fd节点的平均暗电平成比例的减法参考电平持续一定时间,如果fd节点处于暗电平,该减法参考电平由rweight值进行调制,该rweight值由预期的总输出电流确定。在步骤966处,p1开关再次接通,而p2开关关断。在步骤968处,可读出并随后捕获最终输出电压vneuron。

[0070]

图10是示出电荷模式特征提取电路的又一合适实施方式的图,该电荷模式特征提取电路使用差分放大器电路1002来比较不同像素组之间的值。如图10所示,核窗口中的每个像素的像素列输出线可耦接至(有时被认为是差分放大器的一部分的)共享电流吸收器1040,并行连接的第一组像素1020-1可具有经由第一开关矩阵1030耦接至差分放大器1002中的第一节点1050的sf_d节点,并且并行连接的第二组像素1020-2可具有经由第二开关矩阵1030耦接至差分放大器1002中的第二节点1052的sf_d节点。

[0071]

差分放大器1002还可包括连接到节点1050的第一二极管连接的上拉晶体管、连接到节点1052的第二二极管连接的上拉晶体管1010、交叉耦接在节点1050和1052之间的第三上拉晶体管1006、交叉耦接在节点1052和1050之间的第四上拉晶体管1008、被配置为从节点1052接收电压vneuron的比较器1012。比较器1012可被配置为提供用于高速adc路径的数字输出。以这种方式配置,差分放大器1002可用于输出二进制数字值而没有任何种类的加权。因此,如果比较器1012输出“1”,则第一组像素1020-1将具有比第二组像素1020-2大的像素输出值。相反,如果比较器输出“0”,则第一组像素1020-1将具有比第二组像素1020-2小的像素输出值。如果需要,可动态地调整每个单独像素中的行选择信号的栅极电压,以控制模拟核输入的加权。

[0072]

根据一个实施方案,提供了一种成像电路,该成像电路包括第一像素,该第一像素被配置为输出第一像素值;第二像素,该第二像素被配置为输出第二像素值;第一可调电路,该第一可调电路被配置为向第一像素值施加第一加权因子以产生第一加权像素值;第二可调电路,该第二可调电路被配置为向第二像素值施加第二加权因子以产生第二加权像素值;以及输出电路,该输出电路被配置为将第一加权像素值和第二加权像素值组合以产生模拟输出电压。

[0073]

根据另一实施方案,成像电路任选地还包括被配置为在模拟域中存储模拟输出电压的模拟电路。

[0074]

根据另一实施方案,第一像素和第二像素任选地形成在第一管芯上,并且第一可调电路和第二可调电路以及输出电路任选地形成在堆叠在第一管芯下方的第二管芯上。

[0075]

根据另一实施方案,第二管芯任选地包括被配置为将第一像素值和第二像素值路由至第二管芯上的外围电路的本地输出总线。

[0076]

根据另一实施方案,第二管芯任选地包括可配置总线,该可配置总线将第一像素和第二像素中的源极跟随器漏极端子路由至外围电路以产生并求和第一加权值和第二加权值。

[0077]

根据另一实施方案,第二管芯任选地还包括被配置为支持第一加权值和第二加权值的并行产生和求和的附加本地输出总线。

[0078]

根据另一实施方案,第一像素和第二像素任选地是第一管芯上的图像传感器像素阵列的一部分,并且第一像素值任选地经由被配置为从阵列中的其他像素接收像素值的全局输出总线耦接至第二管芯。

[0079]

根据另一实施方案,第一像素和第二像素任选地是图像传感器像素阵列的一部分,并且第一像素值任选地经由被配置为仅从阵列的子集中的其他像素接收像素值的全局输出总线耦接至第二管芯。

[0080]

根据另一实施方案,通过使用单独的光学黑色参考像素,第一像素值任选地在不

同的权重电平下被感测多次。

[0081]

根据另一实施方案,第一像素值不用于通过模数转换器的后续读出,而是仅用于与附加加权像素值组合。

[0082]

根据另一实施方案,第一可调电路和第二可调电路是任选地可调电容器电路。

[0083]

根据另一实施方案,输出电路任选地包括至少一个输出电容器。

[0084]

根据另一实施方案,输出电路任选地包括被配置为存储与正加权因子相关联的电荷的正输出电容器和被配置为存储与负加权因子相关联的电荷的第二输出电容器。

[0085]

根据另一实施方案,第一可调电路和第二可调电路任选地包括可调电阻器电路。

[0086]

根据另一实施方案,第一可调电路和第二可调电路任选地包括可调电流镜电路。

[0087]

根据另一实施方案,第一可调电路和第二可调电路任选地包括电阻性非易失性存储器。

[0088]

根据一个实施方案,提供了一种成像电路,该成像电路包括第一像素,该第一像素具有第一源极跟随器漏极端子(其中第一像素被配置为输出第一像素值);第二像素,该第二像素具有第二源极跟随器漏极端子(其中第二像素被配置为输出第二像素值);以及电流镜电路,该电流镜电路具有用于向第一像素值施加第一权重的第一组可调开关和用于向第二像素值施加第二权重的第二组可调开关。

[0089]

根据另一实施方案,第一组可调开关是任选的不同大小的开关。

[0090]

根据另一实施方案,成像电路任选地还包括被配置为从电流镜电路接收信号的基于开关电容器的集成电路。

[0091]

根据一个实施方案,提供了一种成像电路,该成像电路包括第一组有源像素,该第一组有源像素被配置为产生有源像素值;加权电路,该加权电路被配置为从第一组有源像素中接收有源像素值并产生对应的加权像素值;输出电路,该输出电路被配置为接收并组合加权像素值以产生对应的输出电压;以及第二组空闲像素,该第二组空闲像素被配置为临时存储输出电压以避免必须在数字域中存储输出电压。

[0092]

前述内容仅仅是对本发明原理的例示性说明,本领域技术人员可以在不脱离本发明的范围和实质的前提下进行多种修改。上述实施方案可单个实施或以任意组合方式实施。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1