一种有效解决报文多命中流量过滤分流平台及实现方法与流程

[0001]

本发明涉及一种计算机通信领域的流量过滤分流平台,尤其是涉及一种有效解决报文多命中流量过滤分流平台及实现方法。

背景技术:

[0002]

近年来大量高速网络技术不断出现,由于网络的迅速发展,网络中数据分析技术如内容过滤、网络流分析、协议分析变得原来越复杂,研究如何在高速的网络环境下进行数据的过滤分流显得十分重要。现有的流量过滤分流平台通常在线路板卡中内置过滤分流模块,此设计硬件成本高。同时目前关于流量过滤分流平台针对同一报文可能命中多条规则的问题主要是根据规则的优先级或规则的下发顺序执行最高优先级规则的分流过滤动作或最早下发规则的分流过滤动作,因此不能保证针对此报文的所有的过滤分流动作完全执行,从而造成过滤分流动作部分遗漏缺失。

技术实现要素:

[0003]

为了解决现有的过滤分流平台中同一报文同时命中多条过滤规则不能执行全部规则的动作的问题,本发明提供了一种有效解决报文多命中流量过滤分流平台及实现方法。该过滤分流平台不仅可以针对报文输入端口,l2层的源mac/目的mac/vlan,mpls标签,mpls域内源mac/目的mac/vlan,l3层ip五元组等各字段及掩码或各字段及掩码的组合规则进行过滤分流,而且能通过对配置规则进行拆分、重组、排序等计算有效的解决多命中问题,保证所有规则的动作全部正确的执行。

[0004]

本发明采取的技术方案是:一种有效解决报文多命中流量过滤分流平台,包括安装在机箱中且与背板相连接的主控板卡、线路板卡和交换板卡,其特征在于,所述的交换板卡上设置有zynq处理器、fpga处理器、tcam芯片、时钟模块和供电模块,zynq处理器与 ddr3内存连接,同时分别通过spi接口与emmc存储器、qspi存储器连接,zynq处理器通过rgmii网口与背板上的连接器连接,zynq处理器分别通过selectmap接口和chip2chip接口与fpga处理器连接,zynq处理器分别通过i2c接口与时钟模块、供电模块连接,zynq处理器通过gpio接口连接运行状态指示灯,zynq处理器通过rgmii接口连接rj45以太网调试接口,zynq处理器通过uart接口连接串口调试口;fpga处理器分别通过tx/rx接口连接两个40g qsfp28光模块接口、12个10g sfp+光模块接口,fpga处理器通过interlake接口连接tcam芯片。

[0005]

一种有效解决报文多命中流量过滤分流平台的实现方法,其特征在于,所述方法有如下步骤:一、主控板卡通过rj45以太网接口接收和发送网管的通信命令,主控板卡接收到网管管理命令后,进行网管命令解析和处理,根据业务流程通过背板与线路板卡、交换板卡进行管理数据通信。

[0006]

二、线路板卡具备28个1g sfp+光模块接口、4个10g sfp+光模块接口,负责l2层以太网光信号流量的接收和发送;线路板卡将接收到的l2层报文数据通过qsfp28光模块接口

汇聚到交换板卡进行处理。

[0007]

三、交换板卡通过一个qsfp28光模块接口接收来自线路板卡汇聚的数据流量,并将过滤后的数据通过此qsfp28光模块接口发送回线路板卡;交换板卡通过另一个qsfp28光模块接口负责l3层以太网光信号流的接收和l3层过滤后光信号流量的发送。

[0008]

四、交换板卡上的zynq处理器通过背板接收来自主控板卡的用户规则添加、删除配置命令后,解析配置命令,对用户规则拆分重组,转换用户规则为内部规则格式,交换板卡上的zynq处理完成规则排序计算,将重新排序后的规则通过chip2chip接口下发到fpga处理器。

[0009]

五、fpga处理器接收到网络数据流量后,根据交换板卡zynq处理器下发的规则配置,通过管理tcam模块对报文进行解析及分流过滤处理。

[0010]

六、交换板卡上的zynq处理器在完成规则排序计算后,将更新后的规则存储到规则管理库中。

[0011]

七、当交换板卡上的zynq处理器接收到来自主控板卡的查询规则的命令后,查询规则管理库的规则及这些规则的关联关系,zynq处理器根据规则的关联关系重新将设备内部的规则转换为用户规则,并通过背板网口将查询结果上报给主控板卡,主控板卡通过网管将查询结果上报给用户。

[0012]

本发明在步骤四中,所述规则排序计算有如下操作步骤:遍历规则管理库,比较当前新增规则和原始规则中每条规则关系:(a)、比较当前新增规则包含原始规则中时,更新过滤输出端口,更新规则关系表,新增规则与规则管理库后面的规则继续比较。

[0013]

(b)、比较当前新增规则与原始规则相等时,更新过滤输出端口,更新规则关系表,此规则添加完成。

[0014]

(c)、比较当前新增规则被包含在原始规则时,更新过滤输出端口,更新规则关系表,将新增规则插入规则管理库原始规则前。

[0015]

(d)、比较当前新增规则与原始规则为交集时,求出两条规则相交部分,生成新的规则,将生成的新规则与原始规则的每一条进行比较,判定是否有相同规则,若存在相同规则直接更新相同规则的过滤输出端口号,若不存在相同规则,则将新规则交集新生成规则直接放入规则管理库当前原始规则前,新增加规则与规则管理库后续原始规则继续比较计算。

[0016]

(e)、比较当前新增规则与原始规则无关时,将当前新增规则插到规则管理库尾部。

[0017]

本发明在步骤五中,所述报文解析及分流过滤处理流程有如下操作步骤:(1)、fpga处理器进行包字段提取发送到tcam芯片,tcam芯片对接收的报文数据包逐一搜索包头信息,执行二层规则过滤。

[0018]

(2)、tcam芯片对二层规则过滤后的报文数据包进行包头信息匹配搜索,fpga处理器将tcam搜索结果缓存;fpga根据tcam搜索结果决定报文继续转发或丢弃。

[0019]

(3)、fpga接下来判断是否执行三层规则过滤,如果执行三层规则过滤,则添加l2id标签,发送到tcam芯片执行三层规则过滤。

[0020]

(4)、tcam芯片将进行三层规则包头信息匹配搜索,并将搜索结果返回给fpga处理

器缓存,fpga根据tcam搜索结果决定报文继续转发或丢弃。

[0021]

(5)、若报文需要继续转发,fpga处理器根据过滤规则将数据报文发送至目的输出端口,报文解析及分流过滤处理流程结束。

[0022]

本发明的有益效果是:本发明的线路板卡负责接收和发送需要过滤的l2层光网络信号流量,且将线路板卡光网络信号的数据流量通过40g qsfp28模块汇聚到交换板卡统一过滤处理,在线路板卡不再内置过滤分流模块,此设计不仅节省了平台硬件成本,而且也充分考虑到平台后续针对l2过滤分流流量带宽的扩容。

[0023]

本设计可以在满足针对不同流量报文基于输入端口,l2层的源mac/目的mac/vlan,mpls标签,mpls域内源mac/目的mac/vlan,l3层ip五元组各字段及掩码,或各字段及掩码的组合规则,那些没有耦合关系的规则进行所有规则分流过滤的同时生效的应用场景的需求,还可以通过规则拆分重组计算有效地解决有耦合关联关系的规则不能同时生效的问题,从而满足针对单个报文同时匹配多个复杂的规则时可以执行全部规则的分流过滤动作,所用分流过滤规则同时生效的需求。从而解决了流量分流过滤的多命中问题。

附图说明

[0024]

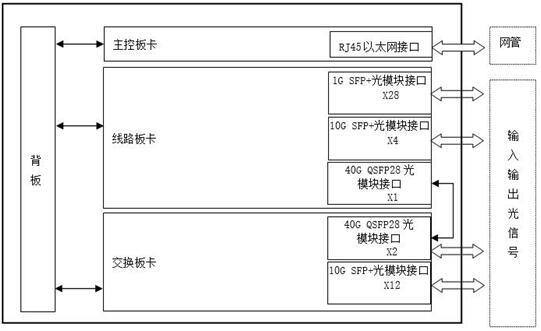

图1是本发明有效解决报文多命中流量过滤平台机箱框架图;图2是本发明有效解决报文多命中流量过滤平台交换板卡原理框图;图3是本发明的总体工作流程图;图4是本发明的规则排序计算流程图;图5是本发明的报文解析及分流过滤处理流程图。

具体实施方式

[0025]

下面结合附图和实施例对本发明进一步说明。

[0026]

如图1所示,本发明平台的硬件形态为atca机箱架构,本机箱由背板、主控板卡、线路板卡、交换板卡组成。主控板卡、线路板卡和交换板卡与背板连接器连接可实现板卡之间的以太网络通信。其中主控板卡负责对atca机箱中所有板卡的指令控制,承担了规则管理的部分功能,并且主控板卡可以通过rj45以太网接口连接外部网管软件,负责接收网管软件的监控管理命令与网管软件通信。

[0027]

线路板卡具备多个1g/10g输入输出光口,负责流量的接收和过滤后l2层流量输出转发等;交换板卡具备多个10g/40g输入输出光口,负责来自线路板卡l2层汇聚的流量和交换板卡的输入端口的l3流量的接收,并负责过滤后输出流量转发,另外交换板卡中部署了fpga模块和tcam芯片负责报文解析及分流过滤;其中背板走线将机箱中所有槽位的板卡进行互联,实现网口互通。

[0028]

主控板卡、线路板卡和交换板卡之间的网络通信协议主要基于tcp、udp的私有通信协议完成。

[0029]

线路板卡具备28个1g sfp+、4个10g sfp+光模块接口,负责l2层以太网光信号流的接收和发送。另外线路卡还具备1个40g的qsfp光模块接口,这个光模块接口与交换板卡的其中一个40g qsfp光模块接口通过一对40g qsfp光模块和光纤连接。当线路板卡接收到来自sfp+光模块接口的以太网信号后,负责将这些流量通过40g qsfp汇聚转发到交换板卡

进行流量过滤处理,交换板卡在完成来自线路板卡的流量过滤后将过滤后的流量又从这个40g qsfp模块接口发送回线路板卡,线路板卡根据过滤规则指定目的转发端口完成过滤后报文的转发。

[0030]

由于本平台面向的实际应用场景中线路板卡中28个1g sfp+光模块接口和4个10g sfp+光模块接口不同时工作,所以线路板卡和交换板卡的40g带宽可以满足实际应用场景的需要。

[0031]

交换板卡具备12个10g sfp+光模块接口和2个40g qsfp28光模块接口。这两个40g qsfp28光模块接口其中一个光模块接口和线路板卡通过一对40g qsfp光模块和光纤连接,负责接收来自线路板卡的需要过滤的以太网流量和发送过滤后的以太网流量到线路板卡。交换板卡的其他光模块接口负责接收来自以太网的光网络数据流量,并在流量过滤完成后将过滤后的流量根据过滤规则从指定的目的端口转发发送出去。另外,在交换板卡中部署了fpga芯片和tcam芯片,这两个模块负责报文解析及分流过滤处理。

[0032]

如图2所示,交换板卡上主要芯片为zynq+fpga+tcam,另外交换板卡上部署了qsfp28/sfp+输入输出模块、时钟模块、供电模块、内存等模块。

[0033]

本设计使用的zynq-7000系列处理器,zynq-7000是赛灵思公司发布的一款可扩展处理平台的处理器。zynq处理器作为交换板卡的控制系统,通过chip2chip通信方式和fpga交互实现过滤规则配置、命中统计查询等功能,通过selectmap通信接口控制fpga程序升级,zynq还可以通过i2c接口完成时钟模块和电源模块的配置和监控,zynq处理器通过gpio接口外接了运行状态指示灯用于交换板卡的运行状态指示,zynq外接了rj45以太网接口及串口调试口用于设备调试,交换板卡zynq处理器支持emmc启动或qspi启动两种启动模式。另外zynq通过背板连接器连接到背板可以和主控板卡进行以太网络通信。

[0034]

本设计使用的fpga(现场可编程逻辑门阵列)处理器,型号为xcvu095-2ffva2104i,型号可替换。fpga为交换板卡的业务处理模块,负责过滤规则的接收,来自sfp+/qsfp28等光信号的接收发送,包字段提取,并按interlaken协议要求的burst结构进行组帧,并将组帧结果传输到nla12000 tcam芯片,并根据nla12000 tcam芯片对该包的匹配搜索结果决定数据流量的每个以太包是否舍弃,从而完成流量过滤功能。

[0035]

nla12000 tcam芯片是博通公司生产的一款高性能tcam芯片。nla12000 tcam芯片负责接收来自fpga的数据流量和控制指令,并对接收的以太包头信息进行搜索匹配,以确定是否有符合条件的包头信息出现,并将匹配搜索结果返回。

[0036]

供电模块的主要功能是为设备提供电源方案。

[0037]

时钟模块为fpga模块提供多路独立的时钟。

[0038]

qsfp28/sfp+输入输出模块主要负责以太网光输入输出光信号的接收和转发。

[0039]

如图3所示,有效解决报文多命中流量过滤分流平台实现方法有如下步骤:一、主控板卡通过rj45以太网接口接收和发送网管的通信命令,主控板卡接收到网管管理命令后,进行网管命令解析和处理,根据业务流程通过背板与线路板卡、交换卡进行管理数据通信。

[0040]

二、线路板卡具备28个1g sfp+光模块接口、4个10g sfp+光模块接口,负责l2层以太网光信号流量的接收和发送;线路板卡将接收到的l2层报文数据通过qsfp28光模块接口汇聚到交换板卡进行处理。

[0041]

三、交换板卡通过一个qsfp28光模块接口接收来自线路板卡汇聚的数据流量,并将过滤后的数据通过此qsfp28光模块接口发送回线路板卡;交换板卡通过另一个qsfp28光模块接口负责以太网光信号流的接收和l3层过滤后光信号流量的发送。

[0042]

四、交换板卡上的zynq处理器通过背板接收来自主控板卡的用户规则添加、删除配置命令后,解析配置命令,对用户规则拆分重组,转换用户规则为内部规则格式,交换板卡上的zynq处理完成规则排序计算,将重新排序后的规则通过chip2chip接口下发到fpga处理器。

[0043]

五、fpga处理器接收到网络数据流量后,根据交换板卡zynq处理器下发的规则配置,通过管理tcam芯片对报文进行解析及分流过滤处理。

[0044]

六、交换板卡上的zynq处理器在完成规则排序计算后,将更新后的规则存储到规则管理库中。

[0045]

七、当交换板卡上的zynq处理器接收到来自主控板卡的查询规则的命令后,查询规则管理库的规则及这些规则的关联关系,zynq处理器根据规则的关联关系重新将设备内部的规则转换为用户规则,并通过背板网口将查询结果上报给主控板卡,主控板卡通过网管将查询结果上报给用户。

[0046]

本平台负责接收用户的添加规则、删除规则、查询规则等配置命令。当接收到用户的添加或删除规则的命令时,解析用户命令,对用户规则拆分重组转换用户规则为内部规则格式,并完成规则排序计算,将重新排序后的规则下发到fpga处理器。zynq处理器在完成规则排序计算后,更新后的规则也被存储规则管理库中。当接收到查询规则的命令后,zynq处理器查询规则管理库的规则及这些规则的关联关系,并根据规则的关联关系重新将设备内部的规则转换为用户规则并上报给用户。当输入单元从不同的sfp+、qsfp28端口接收来自网络的流量数据,这些流量数据经过报文解析及分流过滤后,并按照规则的配置从sfp+、qsfp28等端口输出。

[0047]

本实施例中,当接收到新建或删除规则的命令后,首先将用户规则转换为内部规则。用户规则为符合国际惯例或常见用法的规则格式,如ip地址用某个值和掩码表示,而为了简化规则管理算法,在此将内部这些规则的所有字段都被表示为最大值和最小值的统一格式,添加或删除的整条规则被表示为这条规则涉及的具有统一表示格式的所有字段的集合。

[0048]

用户规则转换为内部规则后,将根据此规则的类型,查找规则管理库中和此规则有关联的所有规则。在本平台中过滤规则涉及较多字段,而实际应用中的过滤规则不一定用到所有字段。从节约硬件的资源和简化规则管理算法的角度考虑,将规则类型分为二层规则和三层规则两种类型。二层规则包含了端口号和osi模型数据链路层相关字段。三层规则的字段为ip五元组相关字段及l2id,l2id是为此三层规则所涉及的二层规则分配的id标签。另外,关于管理规则的计算由于规则用所有字段的最大值和最小值表示,因此关联规则计算可以简化为通过相同字段的最大值和最小值的大小关系的比较计算。

[0049]

在完成关联规则查找后,将对关联规则进行拆分重组。在执行删除规则时,相关规则从规则管理库中全部删除,而其中那些本不应该删除相关规则需要重组为原始规则格式后重新添加计算,后续针对这些规则的添加流程和正常规则添加流程相同。在执行具有相交关系的规则添加时,完成交集的计算并将交集作为新的规则加入到规则管理库。另外规

则管理库中还保存了规则的全部关联关系,这些关联关系可分为包含、被包含、相等、相交、和无关几类。另外规则拆分还存在一种情况,由于l3规则中l2id被作为一个匹配的字段处理,而实际l2id代表的一条二层规则,这条规则可能会有一些关联的规则,这些关联规则的交集部分和新添加的三层规则的其他字段也应该组成新的三层规则。

[0050]

在完成规则的拆分重组计算后,这些新添加的规则被按照规则优先生效的顺序重新插入到规则管理库中,更新后的规则同时也由zynq处理器发送给fpga处理器用于流量过滤处理。

[0051]

如图4所示,本发明在步骤四中,规则排序计算有如下操作步骤:遍历规则管理库,比较当前新增规则和原始规则中每条规则关系:(a)、比较当前新增规则包含原始规则中时,更新过滤输出端口,更新规则关系表,新增规则与规则管理库后面的规则继续比较。

[0052]

(b)、比较当前新增规则与原始规则相等时,更新过滤输出端口,更新规则关系表,此规则添加完成。

[0053]

(c)、比较当前新增规则被包含在原始规则时,更新过滤输出端口,更新规则关系表,将新增规则插入规则管理库原始规则前。

[0054]

(d)、比较当前新增规则与原始规则为交集时,求出两条规则相交部分,生成新的规则,将生成的新规则与原始规则的每一条进行比较,判定是否有相同规则,若存在相关规则直接更新相同规则的过滤输出端口号,若不存在相同规则,则将新规则交集新生成规则直接放入规则管理库当前原始规则前,新增加规则与规则管理库后续原始规则继续比较计算。

[0055]

(e)、比较当前新增规则与原始规则无关时,将当前新增规则插到规则管理库尾部。

[0056]

本实施例中详细描述了新添加规则如何按照相关规则从小到大的顺序的原则重新插入到规则库的处理流程。新添加的过滤规则和规则库中各规则的关系包括以下几种:包含、被包含、相等、无关、交集等,在不同关系过滤规则按照如图4不同分支分别插入规则并更新过滤规则和规则间的关系。将相关规则从小到大顺序添加到规则管理库,原则也是依据规则优先生效原则添加,本平台先下发规则优先生效,当某报文命中先下发规则后执行这条规则的对应动作,关于本报文过滤处理流程结束,此报文不再继续后面规则的命中匹配动作。

[0057]

如图5所示,本发明在步骤五中,报文解析及分流过滤处理流程有如下操作步骤:(1)、fpga处理器进行包字段提取发送到tcam芯片,tcam芯片对接收的报文数据包逐一搜索包头信息,执行二层规则过滤。

[0058]

(2)、tcam芯片对二层规则过滤后的报文数据包进行包头信息匹配搜索,fpga处理器将tcam搜索结果缓存;fpga根据tcam搜索结果决定报文继续转发或丢弃。

[0059]

(3)、fpga接下来判断是否执行三层规则过滤,如果执行三层规则过滤,则添加l2id标签,发送到tcam芯片执行三层规则过滤。

[0060]

(4)、tcam芯片将进行三层规则包头信息匹配搜索,并将搜索结果返回给fpga处理器缓存,fpga根据tcam搜索结果决定报文继续转发或丢弃。

[0061]

(5)、若报文需要继续转发,fpga处理器根据过滤规则将数据报文发送至目的输出

端口,报文解析及分流过滤处理流程结束。

[0062]

当交换板卡上的fpga处理器接收到网络数据流量后,提取包字段,并按interlaken协议要求的burst结构进行组帧,并将组帧结果传输到tcam模块。当交换板卡上的tcam模块接收来自fpga处理器接的数据流量和控制指令后,对接收的以太包头信息进行搜索匹配,以确定是否有符合条件的包头信息出现,并将匹配搜索结果返回。交换板卡上的fpga处理器根据tcam对以太包的匹配搜索结果决定数据流量中的每个以太包是否舍弃,并将过滤后的流量按照配置规则通过sfp+/qsfp28光模块接口输出。

[0063]

依据本实施例处理流程表示范围较小规则,其动作为其全部父规则的动作的集合,较小规则优先生效即是保证了其父规则的全部动作都生效,从而保证单个报文同时匹配多个复杂的规则时可以执行全部规则的分流过滤动作,所用规则分流过滤同时生效的需求。另外本方案针对过滤规则的比较是基于规则管理库表项的比较完成的,此实现方法大大减少代码的复杂度,提高了程序的稳定性。

[0064]

报文解析及分流过滤的基本原理是,对接收的以太网包逐一审查包头信息,并根据匹配和规则决定包的前行或被舍弃,以达到拒绝发送可疑包的目的。在图5所示实施例中,tcam模块负责对接收的以太包头信息进行搜索匹配,以确定是否有符合条件的包头信息出现,并将匹配搜索结果返回。例如,将以太包的源mac地址“00 80 16 00 00 00”作为规则事先写入到tcam中,在此后的以太包头信息流入过程中,tcam便会对以太包头信息进行源mac匹配搜索,如果匹配成功则返回命中结果,此时便可得知该以太包是前行或舍弃。在本实例中分二层规则和三层规则两个阶段处理,不仅仅简化了规则管理算法的复杂度,另外也节省单条规则的占用匹配字段的位宽,节省tcam资源,提高了本平台最大支持的规则数的容量。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1