一种加密算法模块加速器及数据高速加密方法与流程

1.本发明创造属于嵌入式芯片技术领域,尤其是涉及一种加密算法模块加速器及数据高速加密方法。

背景技术:

2.密码芯片中会采用多种密码算法模块来对数据进行加密,密码算法需要多种配置,特别是公钥算法涉及逻辑操作、判断操作,如果单纯采用硬件来实现,硬件代价太大,无法实现;如果采用cpu+密码算法单元来实现,由于cpu的参与大量占用系统资源和时间,极大拖累系统的性能。另一方面,高性能的密码算法应用中涉及多任务的应用,任务之间是无关的、并行的,如何提高多任务级并行数据流的处理速度来达到实际应用中对数据流加解密的要求,这一问题是本发明研究的内容。

技术实现要素:

3.有鉴于此,本发明创造旨在提出一种加密算法模块加速器及数据高速加密方法,以解决密码芯片中多种密码算法模块对数据进行加密时,需要多种配置采用硬件代价太大无法实现,以及采用cpu与密码算法单元实现,会占用大量的系统资源以及时间问题。

4.为达到上述目的,本发明创造的技术方案是这样实现的:

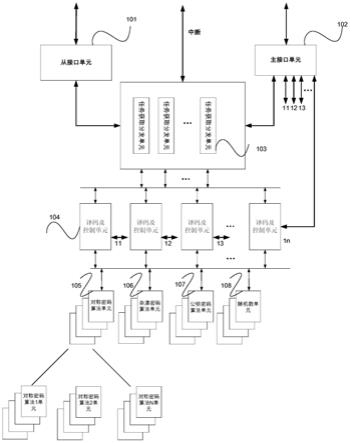

5.一种加密算法模块加速器,包括从总线接口单元、主总线接口单元、任务获取分发单元,以及用于接收任务获取分发单元的译码及控制单元;

6.所述从总线接口单元用于此加密算法模块进行配置;

7.所述主总线接口单元用于此加密算法模块读写数据;

8.所述任务获取分发单元包括多路任务获取分发子单元;

9.所述主总线接口单元的接收端与任务池连接,所述主总线接口单元通过从总线接口单元的配置信息调取任务,所述任务获取分发单元通过主总线接口单元实现两级检索需要执行的任务,任务获取分发单元并将检索的任务发送至译码及控制单元执行。

10.进一步的,所述主总线接口内部含有多路dma引擎。

11.进一步的,所述任务获取分发单元,用于取任务,并将任务分发给译码及控制单元,任务完成后,回写任务状态及任务地址到外部存储空间,取需要执行的任务和回写完成的任务可以同时执行。

12.进一步的,所述任务获取分发单元所取的任务是以指令序列的格式存在,指令序列中除了定义何种类型密码算法之外,还可以定义:读明文操作及地址、写密文操作及地址、读key操作及地址、读iv操作及地址、写报文操作及地址、读写大数操作及地址、逻辑运算、算数运算、跳转运算。

13.进一步的,所述译码及控制单元包括多组,每组译码及控制单元分别包括对称密码算法子单元、杂凑密码算法子单元、公钥密码算法子单元、随机数子单元;

14.所述对称密码算法子单元,用于完成对称密码算法;

15.杂凑密码算法子单元,用于完成杂凑密码算法;

16.公钥密码算法子单元,用于完成公钥密码算法;

17.随机数子单元,用于生成随机数。

18.一种加密算法模块加速器的数据高速加密方法,包括以下步骤:

19.s1、通过任务获取分发单元在任务池中取任务,并将取得的任务信息发送给空闲的译码及控制单元,然后继续取任务,等待空闲的译码及控制单元发送;

20.s2、译码及控制单元接收到任务信息后调用空闲的算法子单元,通过算法子单元进行加密后将加密任务结果信息返回译码及控制单元,;

21.s3、译码及控制单元将加密的任务信息返回至任务获取分发单元;

22.s4、任务获取分发单元将每个任务信息通过主总线接口单元写到外部存储空间,以及记录每个任务的完成情况及状态,重复步骤s1

‑

s4,直至任务结束。

23.进一步的,所述步骤s1中任务信息包括:任务、任务地址、任务获取分发单元标记。

24.相对于现有技术,本发明创造所述的一种加密算法模块加速器及数据高速加密方法具有以下优势:

25.本发明所述的一种加密算法模块加速器及数据高速加密方法,主要针对多任务多进程应用,提出一种并行架构,架构中多个获取分发单元之间是并行的,可以同时执行,多个译码及控制单元之间是并行,可以同时执行,多个算法单元之间是并行的,可以同时执行;同时加解密过程中完全不需要cpu参与,逻辑操作,判断操作,读明文,写密文,密码算法操作等都通过指令序列实现,这样来提高并行加解密任务的速度。

附图说明

26.构成本发明创造的一部分的附图用来提供对本发明创造的进一步理解,本发明创造的示意性实施例及其说明用于解释本发明创造,并不构成对本发明创造的不当限定。在附图中:

27.图1为本发明创造实施例所述的加密算法模块加速器的系统原理框图;

28.图2为本发明创造实施例所述的加密方法任务存放流程意图;

29.图3为本发明创造实施例所述的任务获取分发单元内部状态图;

30.图4为本发明创造实施例所述的译码及控制单元处理任务流程图。

31.附图标记说明:

32.101、从总线接口单元;102、主总线接口单元;103、任务获取分发单元;104、译码及控制单元;105、对称密码算法子单元;106、杂凑密码算法子单元;107、公钥密码算法子单元;108、随机数子单元。

具体实施方式

33.需要说明的是,在不冲突的情况下,本发明创造中的实施例及实施例中的特征可以相互组合。

34.在本发明创造的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明创造和简化描述,而不是指示

或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明创造的限制。此外,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明创造的描述中,除非另有说明,“多个”的含义是两个或两个以上。

35.在本发明创造的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以通过具体情况理解上述术语在本发明创造中的具体含义。

36.下面将参考附图并结合实施例来详细说明本发明创造。

37.如图1至图4所示,一种加密算法模块加速器,包括从总线接口单元101、主总线接口单元102、任务获取分发单元,以及用于接收任务获取分发单元的译码及控制单元104;

38.所述从总线接口单元101用于此加密算法模块进行配置;

39.所述主总线接口单元102用于此加密算法模块读写数据;

40.所述任务获取分发单元103包括多路任务获取分发子单元;

41.所述主总线接口单元102的接收端与任务池连接,所述主总线接口单元102通过从总线接口单元101的配置信息调取任务,所述任务获取分发单元103通过主总线接口单元102实现两级检索需要执行的任务,任务获取分发单元103并将检索的任务发送至译码及控制单元104执行。

42.所述主总线接口内部含有多路dma引擎。

43.所述任务获取分发单元103,用于取任务,并将任务分发给译码及控制单元104,任务完成后,回写任务状态及任务地址到外部存储空间,取需要执行的任务和回写完成的任务可以同时执行。

44.所述任务获取分发单元103所取的任务是以指令序列的格式存在,指令序列中除了定义何种类型密码算法之外,还可以定义:读明文操作及地址、写密文操作及地址、读key操作及地址、读iv操作及地址、写报文操作及地址、读写大数操作及地址、逻辑运算、算数运算、跳转运算。

45.所述译码及控制单元104包括多组,每组译码及控制单元104分别包括对称密码算法子单元105、杂凑密码算法子单元106、公钥密码算法子单元107、随机数子单元108;

46.所述对称密码算法子单元105,用于完成对称密码算法;

47.杂凑密码算法子单元106,用于完成杂凑密码算法;

48.公钥密码算法子单元107,用于完成公钥密码算法;

49.随机数子单元108,用于生成随机数。

50.一种加密算法模块加速器的数据高速加密方法,包括以下步骤:

51.s1、通过任务获取分发单元103在任务池中取任务,并将取得的任务信息发送给空闲的译码及控制单元104,然后继续取任务,等待空闲的译码及控制单元104发送;

52.s2、译码及控制单元104接收到任务信息后调用空闲的算法子单元,通过算法子单元进行加密后将加密任务结果信息返回译码及控制单元104;

53.s3、译码及控制单元104将加密的任务信息返回至任务获取分发单元;

54.s4、任务获取分发单元将每个任务信息通过主总线接口单元写到外部存储空间,以及记录每个任务的完成情况及状态,重复步骤s1

‑

s4,直至任务结束。

55.所述步骤s1中任务信息包括:任务、任务地址、任务获取分发单元标记。

56.具体如下:

57.如图1所示,密码算法模块加速器包含的硬件模块:从总线接口单元101,主总线接口单元(102),任务获取分发单元(103),译码及控制单元104,算法单元,包括:对称密码算法单元105,杂凑密码算法单元106,公钥密码算法子单元107,随机数子单元108。

58.任务获取分发单元包括多个任务获取分发单元(103),加速器中还多个译码及控制单元104,多个算法单元。

59.如图2、图3所示,每一个任务由一组指令序列定义,每个任务的首地址存放在任务池中,任务池的首地址在任务获取分发单元(103)中的寄存器来定义;

60.这样任务获取分发单元(103)可以通过两级索引找到需要执行的任务,

61.任务的指令序列缓存到任务获取分发单元(103)的内部,如果此时找到空闲的译码及控制单元104,则把任务、任务地址和任务获取分发单元标记发送给空闲的译码及控制单元104,然后继续取任务;

62.如果没有发现空闲的译码及控制单元104,则等待空闲的译码及控制单元104,等到某一个空闲,再将任务发给它,然后任务获取分发单元103继续取下一个任务,直到所有待取任务都取完;

63.因为任务获取分发单元103可以一直取任务,把任务发给空闲的译码及控制单元104,这样就可以实现任务级的并行;可以有多个任务获取分发单元103,这样就可以实现应用级或进程级的并行。

64.译码及控制单元104接收到任务后,译码并执行指令序列中的指令,指令涉及的操作包括:读明文操作及地址,写密文操作及地址,读key操作及地址,读iv操作及地址,写报文操作及地址,读写大数操作及地址,逻辑运算,算数运算,跳转运算,算法指令。

65.当执行到算法指令,译码及控制单元104产生请求,与空闲的特定算法单元进行仲裁,一但仲裁到某一个算法单元,此译码及控制单元104和此算法单元绑定并执行译码及控制单元104发送给密码算法操作;

66.绑定期间此算法单元无法参与与其它译码及控制单元104的仲裁,任务结束后,译码及控制单元104释放此算法单元(算法单元空闲,可参与其它译码及控制单元的仲裁),将加密后的数据通过主总线接口单元写到外部memory,并将此任务的地址及状态回写给任务获取分发单元103,仲裁逻辑基于“任务获取分发单元标记”。任务获取分发单元103将任务的地址及状态回通过主总线接口单元写到外部memory。

67.任务获取分发单元103和译码及控制单元104内部都有dma引擎,通过主总线接口单元102,从外部读取数据或向外部写数据。

68.任务获取分发单元103取任务和回写任务的地址及状态可以同时执行,这样就可以实现任务的下发和任务完成的提交同时执行。

69.译码及控制单元105之间是独立的,可以实现多任务级并行。

70.密码算法单元之间是并行的,而且每一种密码算法单元之间也是并行的,例如,公

钥密码算法单元107,杂凑密码算法子单元106,对称密码算法子单元105之间是并行的,可以同时被不同的译码及控制单元104调用,同时执行;对称算法aes,des/3des,sm1,sm4这些对称算法单元之间是并行的,可以同时被不同的译码及控制单元104调用,同时执行;对称算法aes算法单元1,对称算法aes算法单元2......对称算法aes算法单元n,这些算法单元之间也是并行的,可以同时被不同的译码及控制单元104调用,同时执行。

71.对于对称密码运算,译码及控制单元104从外部存储空间读入数据,对称密码算法单元105读入数据,对称运算,对称密码算法单元105写结果到译码及控制单元104,译码及控制单元104写结果到外部存储空间组成5级流水,并行执行;对于杂凑密码算法106,译码及控制单元104从外部存储空间读入数据,杂凑密码算法子单元106读入数据,杂凑密码算法子单元106组成三级流水,并行执行,直到所有数据计算完杂凑密码算法后,最后结果写到数据到译码及控制单元104,译码及控制单元104再将结果写到外部存储空间;

72.对于公钥密码算法子单元107,主要执行大数操作。每一种公钥密码算法是通过若干个大数运算算子加上逻辑运算组成,这些操作由指令序列定义。

73.译码及控制单元104从外部存储空间读入数据到公钥密码算法子单元107内部的存储空间,公钥密码算法子单元107进行大数运算,运算结果还是放到公钥密码算法子单元107内部的存储空间,待所有大数算子执行完成后,最后结果写到数据到译码及控制单元104,译码及控制单元104再将结果写到外部存储空间;

74.对于随机数子单元108,译码及控制单元104控制随机数子单元108生成随机数,随机数生成,生成随机数写到译码及控制单元104,译码及控制单元104再将数据写到外部存储空间组成三级流水,并行执行。

75.以上所述仅为本发明创造的较佳实施例而已,并不用以限制本发明创造,凡在本发明创造的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明创造的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1