用于无线通信系统的基于欠采样的接收器架构的制作方法

用于无线通信系统的基于欠采样的接收器架构

1.相关申请案交叉申请

2.本技术要求于2019年3月1日提交的第16/290,035号、发明名称为“用于无线通信系统的基于欠采样的接收器架构(under

‑

sampling based receiver architecture for wireless communications systems)”的美国专利申请的优先权,所述专利申请的内容通过引用的方式并入本文中。

技术领域

3.本发明大体上涉及无线通信系统领域,具体地,涉及一种无线通信接收器,该无线通信接收器采用欠采样技术来降低时钟速率和功耗,以高效使用硬件和软件处理资源。

背景技术:

4.一些无线通信系统用于接收多个之前已经编码和调制的模拟数据信号。然后,可以在接收器处使用具有比模拟数据信号调制频率更高的频率的码来组合这些多个模拟数据信号。多个模拟数据信号的这种组合产生了跨宽带宽扩频的输出信号。使用高码率来扩频数据信号使得能够通过在模数转换器(analog

‑

to

‑

digital converter,adc)采样之前将多个输入信号组合为单个信号而实现接收器硬件资源的共享,同时还提供更大的抗干扰能力和更高的可靠性(例如,较低的误差向量幅度(error vector magnitude,evm)值)。

5.但是,应理解,这些高码率信号的解码操作对无线接收器系统提出了一些挑战。也就是说,接收器系统需要采用能够以更高的速度运行的硬件、软件和固件元件来正确处理高码率信号。

6.对现有无线通信系统以及下一代无线通信设计的一些改进可能会面临更大的挑战。这些改进和设计包括部署高采样率adc来对高码率信号进行采样。这些改进和设计可能造成接收器硬件和软件处理资源紧张。

技术实现要素:

7.本发明的目的是提供一种用于处理模拟信号的无线接收器。本文提出的公开内容采用了一种可用于接收多个模拟信号的结构。信号编码模块用于根据码率为f

c

的编码方案将接收到的多个模拟信号编码为单个编码模拟复合信号。多个模数转换器用于对所述单个编码模拟复合信号进行采样,并生成代表所述单个编码模拟信号的多个数字复合信号,其中,所述多个模数转换器以低于所述码率f

c

的采样率运行。信号解码模块用于根据所述编码方案对所述多个数字复合信号中的每一个进行解码,以输出包含所述接收到的多个模拟信号的期望信息内容的多个数字信号。

8.根据本发明的其它方面,接收器还包括扩频码生成模块,用于生成编码方案并将所述编码方案提供给所述信号编码模块和所述信号解码模块,其中,所述编码方案是正交码集合。

9.根据本发明的其它方面,在所述接收器中,所述多个模数转换器基于德尔塔

‑

西格

玛delta

‑

sigma调制器并且还包括用于消除量化噪声的噪声传递函数生成器。所述多个模数转换器以采样率对所述单个编码模拟复合信号进行采样,其中,f

c

是所述码率,n是所述编码方案中的码数量。

10.根据本发明的其它方面,所述接收器还包括多相时钟生成器,用于生成多个移相时钟,并将所述移相时钟提供给所述欠采样模数转换模块。

11.根据本发明的其它方面,在所述接收器架构中,多个模数转换器以时钟频率运行,f

c

是所述码率,n是所述编码方案中的码数量,k的范围为0到n

–

1。

12.根据本发明的其它方面,在所述接收器架构中,所述信号解码模块以交织方式对所述多个数字复合信号进行解码。

13.根据本发明的其它方面,提供了一种处理接收到的无线信号的方法。本文提出的公开内容用于接收包含期望信息内容的多个模拟信号,并根据码率为f

c

的编码方案将所述接收到的多个模拟信号编码为单个编码模拟复合信号。对所述单个编码模拟复合信号进行采样,以生成代表所述单个编码模拟信号的多个数字复合信号,其中,所述采样率低于所述码率f

c

。根据所述编码方案对所述数字复合信号进行解码,以输出包含所述接收到的多个模拟信号的期望信息内容的多个数字信号。

14.根据本发明的其它方面,所述处理信号的方法还包括生成编码方案,其中,所述编码方案是正交码集合。

15.根据本发明的其它方面,所述处理信号的方法还包括用于消除量化噪声的噪声传递函数。

16.根据本发明的其它方面,在所述处理信号的方法中,对单个编码模拟复合信号进行采样以采样率执行,其中,f

c

是码率,n是编码方案中的码数量。

17.根据本发明的其它方面,所述处理信号的方法还包括生成多个移相时钟的方法,其中,所述模数转换以时钟频率执行,其中,f

c

是所述码率,n是所述编码方案中的码数量,k的范围为0到n

–

1。

18.根据本发明的其它方面,在所述处理信号的方法中,对所述多个数字复合信号进行解码以生成所述多个数字信号是以交织方式执行的。

附图说明

19.本发明的特征和优点将从以下结合附图的详细描述中变得显而易见。

20.图1示出了无线通信接收器架构的高级功能框图;

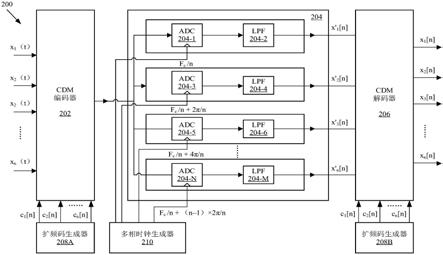

21.图2示出了根据本发明的各种实施例的欠采样接收器架构的高级功能框图;

22.图3示出了根据本发明的各种实施例的代表性cdm编码器模块的高级功能框图;

23.图4示出了根据本发明的各种实施例的代表性adc模块的高级功能框图;

24.图5示出了根据本发明的各种实施例的代表性cdm解码器模块的高级功能框图;

25.图6示出了根据本发明的各种实施例的代表性cdm解码器的示例性高级功能框图;

26.图7a示出了根据本发明的各种实施例的欠采样接收器架构的示例性高级功能框图;

27.图7b示出了根据本发明的各种实施例的欠采样接收器架构的示例性时序图;

28.图7c至图7f示出了根据本发明的各种实施例的欠采样接收器架构的解码操作的功能框图;

29.图8示出了根据本发明的各种实施例的欠采样接收器架构处理的功能流程图。

30.应理解,在整个附图和对应的描述中,相似的特征通过相似的附图标记标识。此外,还应理解,附图和随后的描述仅用于说明目的,并且此类公开并不旨在限制权利要求的范围。

具体实施方式

31.如本文所使用的,术语“大约”或“大致”是指相对于标称值的+/

–

10%的变化。应理解,无论是否具体提及,本文提供的给定值总是包括这种变化。

32.除非另有定义,否则本文所使用的所有技术和科学术语的含义与所描述实施例所属领域的普通技术人员通常理解的相同。

33.图1(现有技术)示出了用于处理接收到的模拟信号的无线接收器100的架构的功能框图。无线接收器100包括码分复用(code division multiplexing,cdm)编码器模块120、模数转换器(analog

‑

to

‑

digital converter,adc)122、cdm解码器模块124和扩频码生成器126a、126b。可能存在其它元素,但未示出。

34.如图1所示,无线接收器100接收模拟输入信号x1(t)、x2(t)

……

x

n

(t),这些信号可以通过一个或多个天线结构(未示出)接收,例如,通过mimo/m

‑

mimo天线接收。此外,每个接收到的信号可以具有不同的调制/编码特性。

35.如图所示,模拟输入信号x1(t)、x2(t)

……

x

n

(t)被转发到cdm编码器120。cdm编码器120用于根据所提供的编码方案,将n个模拟输入信号x1(t)、x2(t)

……

x

n

(t)编码并转换为单个复合编码模拟信号x(t)。也就是说,扩频码生成器126a向cdm编码器模块120提供扩频编码方案c

i

[n]:c1[n]、c2[n]

……

c

n

[n]。

[0036]

具体地,cdm编码器模块120的编码操作是通过扩频编码方案c1[n]、c2[n]

……

c

n

[n]将模拟输入信号x1(t)、x2(t)

……

x

n

(t)进行混频来完成的。混频操作的输出随后可以被滤波和组合,以产生单个模拟复合信号x(t)。

[0037]

应理解,所提供的编码方案c1[n]、c2[n]

……

c

n

[n]可以基于任何正交码或pn序列,例如沃尔什walsh码、哈达玛德hadamard码、古德gold码、拜克barker码等。这些码具有理想的编码特性,并且可以以比模拟输入信号x1(t)、x2(t)

……

x

n

(t)大得多的频率实现。在此过程中,cdm编码器模块120输出在宽频率带宽上有效地扩频的单个复合高速率模拟信号x(t)。

[0038]

编码模拟复合信号x(t)可以提供给具有高带宽的adc模块122,并用于将模拟复合信号x(t)转换为数字复合信号x[n]。

[0039]

数字复合信号x[n]随后被发送用于进一步处理,例如,由cdm解码器模块124解码。cdm解码器模块124处理数字复合信号x[n]以对数字复合信号x[n]进行解码和分离,从而获得数字输入信号x1[n]、x2[n]

……

x

n

[n]。

[0040]

也就是说,cdm解码器模块124通过扩频码生成器126b提供的扩频编码方案c

i

[n]对数字复合信号x

i

[n]进行混频,来接收和处理数字复合信号x[n]。然后,可以求所得混频

样本的积分,以生成数字输入信号x1[n]、x2[n]

……

x

n

[n]。

[0041]

如上所述,无线接收器100需要硬件和软件处理,例如需要adc 122以高处理速度运行,以适于处理高速率高宽带的编码信号。

[0042]

图2示出了根据本发明的各种实施例的欠采样接收器200的架构的功能框图。如图所示,欠采样接收器200采用cdm编码器模块202、欠采样adc模块204、cdm解码器模块206、扩频码生成器模块208a和208b以及多相时钟生成器模块210。可以存在其它元素,但为了简单起见未示出。

[0043]

根据随后的描述,并且根据本发明的各种实施例,可以理解,欠采样adc模块204的实现方式用于有效降低高采样率要求,同时保持数据恢复完整性。在这样做的过程中,欠采样接收器200实质上放松了硬件/软件处理速度和功耗,以适于处理高速率高宽带的编码信号。

[0044]

此外,与本发明的各种实施例一致,将理解,欠采样接收器200的一些或所有所指出的元件,例如cdm编码器模块202、欠采样adc模块204、cdm解码器模块206、扩频码生成器模块208a和208b以及多相时钟生成器模块210中的任何一个或多个,可以通过软件结构实现,以促进与现有接收器架构的集成。

[0045]

如图2所示,cdm编码器模块202接收模拟输入信号x1(t)、x2(t)

……

x

n

(t),并用于根据由扩频码生成器208a提供的编码方案c

i

[n]:c1[n]、c2[n]

……

c

n

[n]将n个模拟输入信号x1(t)、x2(t)

……

x

n

(t)编码并转换为单个复合编码模拟信号x(t)。扩频码生成器208a以码率f

c

生成码。

[0046]

图3提供了根据本发明的各种实施例的cdm编码器模块202的更详细的功能图。如图所示,cdm编码器模块202接收模拟输入信号x1(t)、x2(t)

……

x

n

(t)。这些输入信号被转发到混频器302

‑

1、302

‑2……

302

‑

n,这些混频器通过将输入信号与本地振荡器304

‑

1、304

‑2……

304

‑

n生成的信号混频,将每个输入信号移位到中频(intermediate frequency,if)。反过来,混频器306

‑

1、306

‑2……

306

‑

n用于通过编码方案c

i

[n]:c1[n]、c2[n]

……

c

n

[n]将if移位输入信号进行混频,以对移位输入信号进行扩频。每个输入信号的扩频扩展了其带宽。然后,移位和扩频输入信号被转发到组合器308。组合器308组合移位和扩频输入信号x1(t)、x2(t)

……

x

n

(t),以产生单个宽带模拟复合信号x(t)。

[0047]

应理解,单个宽带模拟复合信号x(t)造成接收器的接收器硬件和软件处理资源紧张。这是由于adc模块122的带宽处理能力有限。在传统接收器中,adc应以输入信号带宽的至少两倍的采样率或时钟速率运行,以实现令人满意的模数转换,而不会丢失任何信息。

[0048]

如上文关于无线接收器100所讨论的,adc模块122采用具有高带宽的单个adc将单个宽带模拟复合信号x(t)转换为数字复合信号x[n]。但是,如图2所示,欠采样接收器200包括欠采样adc模块204,该模块采用欠采样adc组204

‑

1、204

‑

3、204

‑5……

204

‑

n。每个欠采样adc都以较低的带宽和量化分辨率运行。在信号链中,欠采样adc组204

‑

1、204

‑

3、204

‑5……

204

‑

n分别跟随低通滤波器组204

‑

2、204

‑

4、204

‑6……

204

‑

m,其中,欠采样adc的数量和低通滤波器的数量可以等于或大于输入信号的数量。欠采样adc模块204中采用的adc可以是任何适当的模数转换器,例如,基于delta

‑

sigma调制等。鉴于以下讨论,将理解,使用以欠采样方式运行的多个adc可以使操作可靠和准确,而不会产生与使用单个高速adc相关的问题,如上文关于图1所讨论的。

[0049]

如图2所示,模拟复合信号x(t)被转发到欠采样adc模块204,然后被并行馈送到欠采样adc组204

‑

1、204

‑

3、204

‑5……

204

‑

n。每个欠采样adc的采样率为其中,f

c

是码率,n是编码方案c

i

[n]:c1[n]、c2[n]

……

c

n

[n]中的码数量。每个欠采样adc以采样频率对模拟复合信号x(t)进行采样。在这样做的过程中,每个欠采样adc会使频谱对称折叠,从而使采样模拟复合信号x(t)的图像混叠并相互重叠,从而降低总带宽要求。

[0050]

欠采样模拟复合信号x(t)的信息随后以交织方式恢复。换句话说,欠采样adc 204

‑

1、204

‑

3、204

‑5……

204

‑

n中的每一个都设有由多相时钟生成器模块210生成的移相时钟。每个时钟相移其中,k的范围为0到n

–

1,n是码的总数量。例如,欠采样adc 204

‑

1以时钟频率运行,而欠采样adc 204

‑

2以时钟频率运行,依此类推。此外,每个欠采样adc 204

‑

1、204

‑

3、204

‑5……

204

‑

n的输出被转发到低通滤波器204

‑

2、204

‑

4、204

‑6……

204

‑

m。低通滤波器204

‑

2、204

‑

4、204

‑6……

204

‑

m用于协助欠采样adc模块204通过对量化误差引入的噪声分布进行整形来提高欠采样模拟复合信号x(t)的质量。低通滤波器204

‑

2、204

‑

4、204

‑6……

204

‑

m的输出产生欠采样数字复合信号x1'[n]、x2'[n]

……

x

n

'[n],其中,每个信号包含根据移相时钟的样本。

[0051]

图4示出了根据本发明的各种实施例的欠采样adc 204

‑

1的高级功能框图。如图所示,欠采样adc 204

‑

1采用采样和保持电路402

‑

1、减法器402

‑

2、量化器402

‑

3和噪声传递函数(noise transfer function,ntf)生成器402

‑

4。

[0052]

模拟复合信号x(t)被提供给采样和保持电路402

‑

1,其中,采样和保持电路402

‑

1对连续变化的模拟复合信号x(t)进行采样,并在将其值保持在恒定电平持续指定的最小时间间隔。然后,由量化器402

‑

3量化该采样和保持值。量化样本被反馈到ntf生成器402

‑

4,ntf生成器402

‑

4根据量化器402

‑

3的输出连续生成信号,以消除量化器402

‑

3生成的量化噪声。也就是说,从模拟复合信号x(t)的采样值中减去ntf生成器402

‑

4生成的信号,以补偿量化器402

‑

3引入的噪声。因此,ntf生成器402

‑

4使adc 402能够以低量化电平有效地运行。

[0053]

然后,量化器402

‑

3的输出被馈送到低通滤波器204

‑

2。低通滤波器204

‑

2用于滤除量化器402

‑

3提供的信号中的量化噪声。因此,ntf生成器402

‑

4、低通滤波器204

‑

2协助欠采样adc 204

‑

1在低量化电平上运行。应理解,其它欠采样adc 204

‑

3、204

‑5……

204

‑

n也使用与欠采样adc 204

‑

1类似的架构。

[0054]

回到图2,数字复合信号x1'[n]、x2'[n]

……

x

n

'[n]随后被发送到cdm解码器模块206用于进一步处理。cdm解码器模块206以交织方式处理数字复合信号x1'[n]、x2'[n]

……

x

n

'[n],以对数字复合信号x1'[n]、x2'[n]

……

x

n

'[n]进行解码和分离,以根据由扩频码生成器208b提供的编码方案c

i

[n]:c1[n]、c2[n]

……

c

n

[n]获得数字输入信号x1[n]、x2[n]

……

x

n

[n]。扩频码生成器208b以码率f

c

生成码。

[0055]

此外,图5示出了根据本发明的各种实施例的cdm解码器模块206。cdm解码器模块206采用一组cdm解码器502

‑

1、502

‑2……

502

‑

n,其中,cdm解码器的数量等于编码方案c

i

[n]:c1[n]、c2[n]

……

c

n

[n]中的码数量,还等于模拟输入信号的数量。

[0056]

如图5所示,cdm解码器模块206接收数字复合信号x1'[n]、x2'[n]

……

x

n

'[n]。每个接收到的数字复合信号被转发到cdm解码器502

‑

1、502

‑2……

502

‑

n中的每一个。在所示实

施例中,这是以并行的方式完成的。cdm解码器502

‑

1、502

‑2……

502

‑

n中的每一个还从编码方案c

i

[n]:c1[n]、c2[n]

……

c

n

[n]接收适当的扩频码,以对数字复合信号x1'[n]、x2'[n]

……

x

n

'[n]进行解码和分离,从而以交织方式获得数字输入信号x1[n]、x2[n]

……

x

n

[n]。cdm解码器502

‑

1、502

‑2……

502

‑

n中的每一个的输出将是模拟输入信号x1(t)、x2(t)

……

x

n

(t)的数字版本。例如,cdm解码器502

‑

1的输出将是对应于模拟输入信号x1(t)的数字输入信号x1[n],而cdm解码器502

‑

2的输出将是对应于模拟输入信号x2(t)的数字输入信号x2[n],依此类推。

[0057]

图6示出了根据本发明的各种实施例的cdm解码器502

‑

1的高级功能框图。如图所示,cdm解码器502

‑

1采用一组混频器602

‑

1、602

‑2……

602

‑

n,其中,混频器的数量等于数字输入的数量。cdm解码器502

‑

1还采用加法器604和平均模块606。

[0058]

如图所示,混频器602

‑

1、602

‑2……

602

‑

n中的每一个分别接收对应的数字复合信号x1'[n]、x2'[n]

……

x

n

'[n]。接着,混频器602

‑

1、602

‑2……

602

‑

n将数字复合信号x1'[n]、x2'[n]

……

x

n

'[n]与适当的扩频码位混频。例如,混频器602

‑

1将数字复合信号x1'[n]与码c1[n]中的第一个位(即c1[1])混频,而混频器602

‑

2将数字复合信号x2'[n]与码c1[n]中的第二个位(即c1[2])混频,依此类推。混频器602

‑

1、602

‑2……

602

‑

n的输出由加法器604以交织方式相加,然后平均模块606对加法器604的输出求平均值,以得到数字输入信号x1[n]。应理解,其它cdm解码器502

‑2……

502

‑

n也使用与cdm解码器502

‑

1类似的架构。

[0059]

图7a示出了根据本发明的各种实施例的欠采样接收器架构700的示例性功能框图。欠采样接收器架构700接收四个模拟输入信号x1(t)、x2(t)、x3(t)和x4(t),并以如上所述的类似方式对其进行处理。此外,欠采样接收器架构700采用:用于将混频模拟输入信号x1(t)、x2(t)、x3(t)和x4(t)与适当的扩频码混频的混频器组702

‑

1、702

‑

2、702

‑

3和702

‑

4;组合器703;欠采样adc组704

‑

1、704

‑

2、704

‑

3和704

‑

4;低通滤波器组705

‑

1、705

‑

2、705

‑

3和705

‑

4;用于将数字复合信号x1'[n]、x2'[n]、x3'[n]和x4'[n]与适当的扩频码混频的混频器组706

‑

1、706

‑

2、706

‑

3和706

‑

4;加法器组707

‑

1、707

‑

2、707

‑

3和707

‑

4;平均模块组708

‑

1、708

‑

2、708

‑

3和708

‑

4。

[0060]

如图7a所示,欠采样接收器700接收模拟输入信号x1(t)、x2(t)、x3(t)和x4(t),这些信号可以通过一个或多个天线结构(未示出)接收,例如,通过mimo/m

‑

mimo天线接收。此外,每个接收到的信号可以具有不同的调制/编码特性。

[0061]

如图所示,模拟输入信号x1(t)、x2(t)、x3(t)和x4(t)然后被转发到混频器组702

‑

1、702

‑

2、702

‑

3和702

‑

4。接着,混频器702

‑

1、702

‑

2、702

‑

3和702

‑

4用于通过将模拟输入信号x1(t)、x2(t)、x3(t)和x4(t)分别与适当的扩频码c1[n]、c2[n]、c3[n]、c4[n]混频,编码模拟输入信号x1(t)、x2(t)、x3(t)和x4(t)。混频操作的输出随后可以被滤波并由组合器703组合,以将模拟输入信号x1(t)、x2(t)、x3(t)和x4(t)转换为单个复合编码模拟信号x(t)。

[0062]

将理解,所提供的编码方案c1[n]、c2[n]、c3[n]、c4[n]可以基于包括正交码或pn序列的多个不同码中的任一个,例如walsh码、hadamard码、gold码和barker码。这些码具有理想的编码特性,并且可以以比模拟输入信号x1(t)、x2(t)、x3(t)和x4(t)大得多的频率实现。在这样做的过程中,组合器703输出在宽频率带宽上有效地扩频的单个复合高速率模拟信号x(t)。

[0063]

具体地,例如,欠采样接收器700使用的扩频码是每个码的长度等于4的hadamard

正交码,hadamard码如下所示:

[0064][0065]

如图7a所示:混频器702

‑

1将模拟输入信号x1(t)与c1[n](即[+1+1+1+1])混频;混频器702

‑

2将模拟输入信号x2(t)与c2[n](即[+1

–

1+1

–

1])混频;混频器702

‑

3将模拟输入信号x3(t)与c3[n](即[+1+1

–1–

1])混频;混频器702

‑

4将模拟输入信号x4(t)与c4[n](即[+1

–1–

1+1])混频。在这样做时,组合器703然后将模拟输入信号x1(t)、x2(t)、x3(t)和x4(t)转换为单个复合编码模拟信号x(t)。

[0066]

然后,复合模拟信号x(t)被并行转发到欠采样adc 704

‑

1、704

‑

2、704

‑

3和704

‑

4。然后,欠采样adc 704

‑

1、704

‑

2、704

‑

3和704

‑

4中的每一个以采样频率f

c

/4对模拟复合信号x(t)进行采样。在这样做的过程中,欠采样adc 704

‑

1、704

‑

2、704

‑

3和704

‑

4中的每一个会使频谱对称折叠,从而使采样模拟复合信号x(t)的图像混叠并相互重叠,从而降低总带宽要求。

[0067]

随后,欠采样模拟复合信号x(t)的信息以交织方式恢复。换句话说,欠采样adc 704

‑

1、704

‑

2、704

‑

3和704

‑

4中的每一个有移相时钟。每个时钟相移其中,k的范围为0到3。例如,欠采样adc 704

‑

1以时钟频率运行,欠采样adc 704

‑

2以时钟频率运行,欠采样adc 704

‑

3以时钟频率运行,欠采样adc 704

‑

4以时钟频率运行。此外,欠采样adc 704

‑

1、704

‑

2、704

‑

3和704

‑

4中的每一个的输出分别转发到低通滤波器705

‑

1、705

‑

2、705

‑

3和705

‑

4。低通滤波器705

‑

1、705

‑

2、705

‑

3和705

‑

4用于协助欠采样adc 704

‑

1、704

‑

2、704

‑

3和704

‑

4通过对量化误差引入的噪声分布进行整形来提高欠采样模拟复合信号x(t)的质量。低通滤波器705

‑

1、705

‑

2、705

‑

3和705

‑

4的输出产生欠采样数字复合信号x1'[n]、x2'[n]、x3'[n]和x4'[n],其中,每个信号包含根据移相时钟的样本。

[0068]

如图所示,数字复合信号x1'[n]、x2'[n]、x3'[n]和x4'[n]被转发到混频器706

‑

1、706

‑

2、706

‑

3和706

‑

4。例如,混频器706

‑

1接收数字复合信号x1'[n],混频器706

‑

2接收数字复合信号x2'[n],混频器706

‑

3接收数字复合信号x3'[n],混频器706

‑

4接收数字复合信号x4'[n]。接着,混频器706

‑

1、706

‑

2、706

‑

3和706

‑

4将数字复合信号x1'[n]、x2'[n]、x3'[n]和x4'[n]与适当的扩频码混频。混频器706

‑

1、706

‑

2、706

‑

3和706

‑

4的输出通过加法器707

‑

1、707

‑

2、707

‑

3和707

‑

4交织,每个交织信号的平均值通过平均模块708

‑

1、708

‑

2、708

‑

3和708

‑

4获得,从而获得最终数字输入信号x1[n]、x2[n]、x3[n]和x4[n]。

[0069]

图7b示出了欠采样接收器架构700的示例性时序图。如图所示,时钟脉冲clk1、clk2、clk3和clk4中的每一个都具有π/2的相移。例如,clk2相对于clk1具有π/2的相移,而clk3相对于clk2具有π/2的相移,clk4相对于clk3具有π/2的相移。时钟脉冲clk1、clk2、clk3和clk4中的每一个的频率为f

c

/4,其中,f

c

是码率。

[0070]

欠采样adc 704

‑

1、704

‑

2、704

‑

3和704

‑

4分别以clk1、clk2、clk3和clk4的正沿运行,并根据图7b所示的移相时钟对模拟复合信号x(t)进行采样,以分别输出数字复合信号x1'[n]、x2'[n]、x3'[n]和x4'[n]。应理解,欠采样adc 704

‑

1、704

‑

2、704

‑

3和704

‑

4可以分别

以clk1、clk2、clk3和clk4的负沿运行。

[0071]

图7c至图7f示出了欠采样接收器架构700的解码操作的功能框图。如图7c所示,混频器706

‑

1还包括子混频器706

‑

1a、706

‑

1b、706

‑

1c和706

‑

1d。子混频器706

‑

1a、706

‑

1b、706

‑

1c和706

‑

1d中的每一个分别接收如图7b所示的一个数字复合信号x1'[n]、x2'[n]、x3'[n]和x4'[n]。例如,混频器706

‑

1a接收数字复合信号x1'[n](即[a5+b5+c5+d5][a1+b1+c1+d1]),混频器706

‑

1b接收数字复合信号x2'[n](即[a6

–

b6+c6

–

d6][a2

–

b2+c2

–

d2]),混频器706

‑

1c接收数字复合信号x3'[n](即[a7+b7

–

c7

–

d7][a3+b3

–

c3

–

d3]),混频器706

‑

1d接收数字复合信号x4'[n](即[a8

–

b8

–

c8+d8][a4

–

b4

–

c4+d4])。接着,子混频器706

‑

1a、706

‑

1b、706

‑

1c和706

‑

1d将数字复合信号x1'[n]、x2'[n]、x3'[n]和x4'[n]与适当的扩频码位混频。例如,混频器706

‑

1a将数字复合信号x1'[n]与码c1[n](即[1])的第一个位混频,混频器706

‑

1b将数字复合信号x2'[n]与码c1[n](即[1])的第二个位混频,混频器706

‑

1c将数字复合信号x3'[n]与码c1[n](即[1])的第三个位混频,混频器706

‑

1d将数字复合信号x4'[n]与码c1[n](即[1])的第四个位混频。子混频器706

‑

1a、706

‑

1b、706

‑

1c和706

‑

1d的输出由加法器707

‑

1交织,平均模块708

‑

1对加法器707

‑

1的输出求平均值,以得到数字输入信号x1[n]。

[0072]

如图7d所示,混频器706

‑

2还包括子混频器706

‑

2a、706

‑

2b、706

‑

2c、706

‑

2d、加法器707

‑

2、平均模块708

‑

2,它们以如上所述的类似方式运行,以使用扩频码c2[n](即[+1

–

1+1

–

1])得到数字输入信号x2[n]。此外,图7e示出了混频器706

‑

3还包括子混频器706

‑

3a、706

‑

3b、706

‑

3c和706

‑

3d、加法器707

‑

3、平均模块708

‑

3,它们以与如上所述的类似方式运行,以使用扩频码c3[n](即[+1+1

–1–

1])得到数字输入信号x3[n]。图7e示出了混频器706

‑

4还包括子混频器706

‑

4a、706

‑

4b、706

‑

4c和706

‑

4d、加法器707

‑

4、平均模块708

‑

4,它们以如上所述的类似方式运行,以使用扩频码c3[n](即[+1

–1–

1+1])得到数字输入信号x4[n]。

[0073]

图8示出了根据本发明的各种实施例的涉及欠采样接收器处理的过程800的功能流程图。

[0074]

如图所示,过程800开始于步骤802,其中,欠采样接收器架构200接收包含期望信息内容的多个模拟信号。如上所述,架构200可以包括一个或多个用于接收模拟信号的天线结构。

[0075]

执行过程800的步骤804,其中,架构200基于编码方案将接收到的多个信号编码为单个模拟复合信号。如上所述,扩频码生成器模块208a用于生成提供给cdm编码器模块202的编码方案。接着,cdm编码器模块202用于通过编码方案对接收到的多个信号进行混频和组合,以输出单个复合模拟信号。

[0076]

在步骤806,架构200用于以低于所需的速率对模拟复合信号进行采样,从而根据移相时钟对模拟复合信号进行欠采样以生成数字复合信号。也就是说,如以上所描述,欠采样adc模块204执行欠采样操作以生成数字复合信号,然后对数字复合信号进行滤波以去除量化噪声。

[0077]

最后,在步骤808,架构200对数字复合信号进行解码,以输出对应于包含期望内容的接收到的模拟信号的数字信号。如以上所描述,cdm解码器模块206通过编码方案将数字复合信号进行混频,以交织方式添加混频信号,然后求平均值以生成对应于包含期望内容的接收到的模拟信号的数字信号,来对编码信号信息进行解码和恢复。

[0078]

因此,通过欠采样接收器架构200所采用的欠采样技术,降低了硬件/软件处理速

度,可以实现较低带宽资源,并且降低了功耗。

[0079]

应理解,所描述的欠采样接收器架构、组成组件和相关过程的操作和功能可以通过基于硬件、基于软件、基于固件的元件或其组合来实现。这种操作替代方案并不以任何方式限制本发明的范围。

[0080]

还将理解,尽管本文中提出的原理已经参考特定的特征、结构和实施例进行了描述,但很明显,可以在不脱离此类公开内容的情况下进行各种修改和组合。因此,说明书和附图被简单地视为由所附权利要求所定义的原理的说明,并被设想涵盖属于本发明范围的任何和所有修改、变化、组合或等同物。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1