用于迭代代码设计的通信设备和方法与流程

1.本发明涉及用于迭代代码设计的第一通信设备和第二通信设备。此外,本发明还涉及对应的方法和计算机程序。

背景技术:

2.当前的3gpp第五代(fifth generation,5g)标准,也称为新空口(new radio,nr),尽管满足各种要求,但在很大程度上依赖于从前几代标准继承的先前传统设计,其中物理层模块是单独设计和优化的,用于提供高频谱效率(spectral efficiency,se)和高数据速率的服务。

3.随着5g标准化的推进,实现与新定义的服务对应的新指标的困难出现了。例如,用于未来一代的典型超可靠低延迟通信/工业物联网(ultra-reliable low-latency communication/industrial internet of things,urllc/iiot)应用将需要有限块长度分组的显著更高的可靠性和/或更短的传输延迟。理论结果表明,为更短的分组传输获得更高可靠性的方法是高效地利用到发送器的信道输出反馈。

4.主要设计用于提供高数据速率的传统无线通信系统使用线性码,如涡轮码(turbo code)和低密度奇偶校验(low density parity check,ldpc)码。至于反馈机制,众所周知的混合自动重传请求(hybrid automatic repeat request,harq)反馈被用作在解码失败时使初始生成的码字的相同部分或另一部分能够重传的方法。在接收器中,接收到的编码比特的软合并提高了可靠性。harq类型反馈限制了理论上可以通过充分利用信道输出反馈获得的增益。

技术实现要素:

5.本发明的示例的目的是提供一种方案,其减轻或解决传统方案的缺点和问题。

6.上述和其它目的是通过独立权利要求的主题来解决的。本发明的其它有利示例可以在从属权利要求中找到。

7.根据本发明的第一方面,通过用于无线通信系统的第一通信设备实现上述和其它目的,所述第一通信设备被配置为:

8.基于在第一信道中向第二通信设备发送的系统符号集合和在第二信道中从所述第二通信设备接收的对应系统符号集合,获得第一噪声值集合,其中,所述系统符号集合与对应于信息比特集合并从k=1,2,...,k索引的信息符号集合相关联,其中,k是整数;

9.对于k=1:

10.使用第一发生器设备并基于所述系统符号集合中的第一系统符号和所述第一噪声值集合中的第一噪声值,生成第一奇偶校验符号集合p1,

11.在所述第一信道中向所述第二通信设备发送所述第一奇偶校验符号集合p1,

12.在所述第二信道中从所述第二通信设备接收第一对应奇偶校验符号集合

13.对于k=2,...,k:

14.i)基于发送的第k-1奇偶校验符号集合p

k-1

和接收的第k-1奇偶校验符号集合,获得第k-1噪声值集合,

15.ii)使用所述第一发生器设备并基于第k系统符号、所述第一噪声值集合中的第k到第k-δ

tx

噪声值以及第k-1到第噪声值集合,生成第k奇偶校验符号集合pk,其中,δ

tx

和是整数,对应于第l奇偶校验符号,其中,l=1,2,...,p,p是所述信息比特集合中的每个信息比特的奇偶校验符号的数量,

16.iii)在所述第一信道中向所述第二通信设备发送所述第k奇偶校验符号集合pk,以及

17.iv)在所述第二信道中从所述第二通信设备接收第k对应奇偶校验符号集合

18.系统符号集合与对应于信息比特集合的信息符号集合相关联,这可以理解为,信息比特集合是使用例如传统调制方案的调制方案调制的。信息符号没有被进一步编码,因此被表示为系统符号。

19.接收第k对应奇偶校验符号集合可以理解为第二通信设备回送从第一通信设备接收的第k奇偶校验符号集合pk。因此,对应奇偶校验符号集合可以被视为发送的有噪声的奇偶校验符号pk。更准确地说,是发送的奇偶校验符号pk,包括第一(也称为前向)信道上的噪声和第二(也称为反馈)信道上的噪声。

20.因此,提供了迭代代码设计,包括在第一通信设备与第二通信设备之间的发送和接收。根据第一方面的第一通信设备的优点是,可以在无线通信系统中获得差错率(例如bler)的一个数量级的增益。

21.在根据第一方面的第一通信设备的一种实现方式中,δ

tx

等于1。

22.这种实现方式的优点是,对于δ

tx

的相同值和任何传统的调制阶数,获得差错率的一个数量级的增益。

23.在根据第一方面的第一通信设备的一种实现方式中,当p等于2时,等于1,等于0。

24.这种实现方式的优点是,对于相同的值和任何调制阶数,获得差错率的一个数量级的增益。

25.在根据第一方面的第一通信设备的一种实现方式中,所述第一发生器设备被配置为:

26.还基于所述第一发生器设备的前一时刻生成所述第k奇偶校验符号集合pk。

27.第一发生器设备可以是在任何给定时刻基于其输入和内部状态产生输出的设备。此外,在移动到下一时刻之前,内部状态可以被更新。第一发生器设备可以由状态列表、其初始状态和触发转换到另一状态的输入来定义。

28.这种实现方式的优点是在不同时刻生成的奇偶校验符号之间存在记忆。这允许具有较大的依赖关系集合,并允许使用这些依赖关系模拟信息的有效编码。依赖关系可以在本文表示由于第一发生器设备的状态在不同时刻生成的奇偶校验符号之间的相关性。因此,可以设计强大的代码。

29.在根据第一方面的第一通信设备的一种实现方式中,其中,所述第一发生器设备是包括单层门控循环单元、线性变换器和线性激活函数的循环神经网络。

30.这种具有线性激活函数而不是非线性激活函数的实现方式的优点是降低实现复杂度。此外,具有线性激活函数允许具有较大值的奇偶校验符号,在使用高阶调制时避免饱和。使用单层门控循环单元而不是两层门控循环单元允许较少复杂的实现。线性变换器允许从门控循环单元的输出生成不同数量的奇偶校验符号,因此能够获得不同的速率。

31.在根据第一方面的第一通信设备的一种实现方式,所述第一通信设备被配置为:

32.向所述第二通信设备发送控制消息,其中,所述控制消息指示k和p。

33.这种实现方式的优点是,对于考虑的频谱效率或编码速率,发送器(即第一通信设备)和接收器(即第二通信设备)具有相同的编码器和解码器结构信息。

34.在根据第一方面的第一通信设备的一种实现方式中,所述控制消息还指示表示接收的系统符号的时间窗口的第一参数δ

rx

和表示接收的奇偶校验符号的时间窗口的第二参数。

35.这种实现方式的优点是获得关于解码器结构的信息,以在第二通信设备上获得一定的性能。

36.根据本发明的第二方面,通过用于无线通信系统的第二通信设备实现上述和其它目的,所述第二通信设备被配置为:

37.在第一信道中从第一通信设备接收系统符号集合,其中,所述系统符号集合对应于与信息比特集合对应并从k=1,2,...,k索引的信息符号集合,其中,k是整数,

38.在第二信道中向所述第一通信设备发送接收的所述系统符号集合;

39.对于k=1,2,...,k:

40.i)在所述第一信道中从所述第一通信设备接收第k奇偶校验符号集合pk,

41.ii)在所述第二信道中向所述第一通信设备发送第k对应奇偶校验符号集合

42.iii)使用第二发生器设备并基于接收的第k到第k-δ

rx

系统符号和接收的第k到第奇偶校验符号,确定第k信息符号,其中,δrx和是整数,对应于第l奇偶校验符号,其中,l=1,2,...,p,p是所述信息比特集合中的每个信息比特的奇偶校验符号的数量。

43.根据第二方面的第二通信设备的优点是,这种实现允许实现差错率(例如bler)的一个数量级的增益,并且实现表现出较低复杂度。

44.在根据第二方面的第二通信设备的一种实现方式中,δ

rx

等于1或2。

45.这种实现方式的优点是,对于任何调制阶数,可以考虑相同的值,因此可以定义通用结构。

46.在根据第二方面的第二通信设备的一种实现方式中,当p等于2时,等于,等于0或1。

47.这种实现方式的优点是,对于任何调制阶数,可以考虑相同的值,因此可以定义通用结构。

48.在根据第二方面的第二通信设备的一种实现方式中,所述第二发生器设备被配置为:

49.还基于所述第二发生器设备的前一时刻和后一时刻确定所述第k信息符号。

50.第二发生器设备可以是在任何给定时刻基于其输入和内部状态产生输出的设备。此外,在移动到下一时刻之前,内部状态可以被更新。第二发生器设备可以由状态列表、其

初始状态和触发转换到另一状态的输入来定义。

51.这种实现方式的优点是,在不同的时刻之间存在记忆,能够解码编码序列。考虑前一状态和后一状态获取信息符号,以实现更可靠的解码。

52.在根据第二方面的第二通信设备的一种实现方式中,所述第二发生器设备是包括双向单层门控循环单元、线性变换器和线性激活函数的循环神经网络。

53.这种实现方式的优点是,与非线性激活函数相比,线性激活函数的计算复杂度较低。此外,线性激活函数允许具有更大的值,并避免高阶调制的饱和。与两层双向门控循环单元相比,单层双向门控循环单元的计算复杂度要低得多。线性变换器可以保证考虑编码器和解码器不同的码率。

54.在根据第二方面的第二通信设备的一种实现方式中,所述第二通信设备被配置为:

55.从所述第一通信设备接收控制消息,其中,所述控制消息指示k和p。

56.这种实现方式的优点是,发送器(即第一通信设备)和接收器(即第二通信设备)具有相同的解码器编码器结构理解。

57.在根据第二方面的第二通信设备的一种实现方式中,控制消息还指示表示接收的系统符号的时间窗口的第一参数δ

rx

和表示接收的奇偶校验符号的时间窗口的第二参数。

58.这种实现方式的优点是从解码器结构获得信息,以在第二通信设备上获得一定的性能。

59.根据本发明的第三方面,通过用于第一通信设备的方法实现上述和其它目的,所述方法包括:

60.基于在第一信道中向第二通信设备发送的系统符号集合和在第二信道中从所述第二通信设备接收的对应系统符号集合,获得第一噪声值集合,其中,所述系统符号集合与对应于信息比特集合并从k=1,2,...,k索引的信息符号集合相关联,其中,k是整数;

61.对于k=1:

62.使用第一发生器设备并基于所述系统符号集合中的第一系统符号和所述第一噪声值集合中的第一噪声值,生成第一奇偶校验符号集合p1,

63.在所述第一信道中向所述第二通信设备发送所述第一奇偶校验符号集合p1,

64.在所述第二信道中从所述第二通信设备接收第一对应奇偶校验符号集合;

65.对于k=2,...,k:

66.基于发送的第k-1奇偶校验符号集合p

k-1

和接收的第k-1奇偶校验符号集合,获得第k-1噪声值集合,

67.使用所述第一发生器设备并基于第k系统符号、所述第一噪声值集合中的第k到第k-δ

tx

噪声值以及第k-1到第噪声值集合,生成第k奇偶校验符号集合pk,其中,δ

tx

和是整数,对应于第l奇偶校验符号,其中,l=1,2,...,p,p是所述信息比特集合中的每个信息比特的奇偶校验符号的数量,

68.在所述第一信道中向所述第二通信设备发送所述第k奇偶校验符号集合pk,以及

69.在所述第二信道中从所述第二通信设备接收第k对应奇偶校验符号集合

70.根据第三方面的方法可以扩展为对应于根据第一方面的第一通信设备的实现方式的实现方式。因此,该方法的实现方式包括第一通信设备的对应实现方式的特征。

71.根据第三方面的方法的优点与根据第一方面的第一通信设备的对应实现方式的优点相同。

72.根据本发明的第四方面,通过用于第二通信设备的方法实现上述和其它目的,所述方法包括:

73.在第一信道中从第一通信设备接收系统符号集合,其中,所述系统符号集合对应于与信息比特集合对应并从k=1,2,...,k索引的信息符号集合,其中,k是整数,

74.在第二信道中向所述第一通信设备发送接收的所述系统符号集合;

75.对于k=1,2,...,k:

76.在所述第一信道中从所述第一通信设备接收第k奇偶校验符号集合pk,

77.在所述第二信道中向所述第一通信设备发送第k对应奇偶校验符号集合

78.使用第二发生器设备并基于接收的第k到第k-δ

rx

系统符号和接收的第k到第奇偶校验符号,确定第k信息符号,其中,δ

rx

和是整数,对应于第l奇偶校验符号,其中,l=1,2,...,p,p是所述信息比特集合中的每个信息比特的奇偶校验符号的数量。

79.根据第四方面的方法可以扩展为对应于根据第二方面的第二通信设备的实现方式的实现方式。因此,该方法的实现方式包括第二通信设备的对应实现方式的特征。

80.根据第四方面的方法的优点与根据第二方面的第二通信设备的对应实现方式的优点相同。

81.本发明还涉及计算机程序,其特征在于,程序代码在由至少一个处理器运行时,使所述至少一个处理器执行根据本发明的示例的任何方法。此外,本发明还涉及计算机程序产品,包括计算机可读介质和所述计算机程序,其中,所述计算机程序包括在所述计算机可读介质中,并且包括以下群组中的一个或多个:只读存储器(read-only memory,rom)、可编程rom(programmable rom,prom)、可擦除prom(erasable prom,eprom)、闪存、电eprom(electrically eprom,eeprom)和硬盘驱动器。

82.本发明的示例的其它应用和优点从以下详细描述中显而易见。

附图说明

83.附图旨在阐明和解释本发明的不同示例,在附图中:

[0084]-图1示出了根据本发明的示例的第一通信设备;

[0085]-图2示出了根据本发明的示例的用于第二通信设备的方法;

[0086]-图3示出了根据本发明的示例的第二通信设备;

[0087]-图4示出了根据本发明的示例的用于第二通信设备的方法;

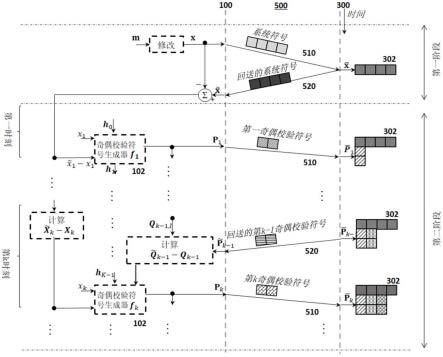

[0088]-图5示出了根据本发明的示例的无线通信系统;

[0089]-图6示出了根据本发明的示例的无线通信系统中的第一通信设备与第二通信设备之间的交互;

[0090]-图7示出了解码器自动化;

[0091]-图8示出了根据本发明的示例的第一发生器设备;

[0092]-图9示出了根据本发明的示例的第二发生器设备;

[0093]-图10示出了训练过程的功能框图;并且

[0094]-图11至图14示出了本发明的示例的性能结果。

具体实施方式

[0095]

具有反馈的信道的传统代码是非线性代码,非线性代码将当前信息比特和接收到的反馈映射到要在当前时间间隔内传输的信号。直观地,使用传统的代码设计方法很难获得这样的非线性代码。在这种情况下,使用深度神经网络的机器学习方法被认为是有前景的代码设计方法,这些方法本质上允许通过在非线性编码器上产生任何线性来优化性能。此外,使用神经网络设计的反馈码可以潜在地与使用传统harq反馈的线性码级联,以进一步提高可靠性,从而满足未来一代无线网络的严格可靠性要求。

[0096]

参考上一节,代码设计的可能方法是在编码器和解码器中使用所谓的循环神经网络(recurrent neural network,rnn)。事实上,这种结构具有记忆或隐藏状态,可以跟踪先前的输入。因此,通过使用rnn记忆联合映射信息比特和先前接收到的反馈,以迭代的方式执行编码,可以创建新的输出。这种策略已经得到利用,并且已知仅靠这一策略不足以实现传统方法的良好性能。相反,已经表明,在具有反馈的擦除信道上的多步重传实现容量。

[0097]

按照这种方法,发送的比特要么被完美接收,要么被擦除,并且擦除位置被反馈回发送器。在这种信道中,可以首先发送未编码符号块,然后在以下步骤中发送在前一个块中被擦除的任意符号。这激发了两阶段方案,其中,在第一阶段发送未编码比特或符号或者系统比特或符号,然后基于第一阶段的反馈,在第二阶段发送编码比特或符号或者奇偶校验比特或符号。因此,代码只需要为第二阶段设计。

[0098]

基于传统方案的神经网络设计的传统编码器和解码器架构不允许实现未来无线通信系统所需的非常高的可靠性或低的误块率(block error rate,bler)。此外,所提出的传统方案的解码器具有相当大的计算复杂度,因为在这种解码器中需要大量的训练变量。这最终将导致大量的训练时间,从而导致高延迟。此外,传统的编码器和解码器架构不考虑为二进制相移键控(binary shift keying,bpsk)调制开发的传统方案如何或是否可以适应于更高阶调制和/或更高的频谱效率,并因此被用于无线系统的传统调制。

[0099]

因此,在本公开中提出并评估了用于神经网络的新编码器和解码器架构。该方案可以被认为是基于顺序迭代码(sequential iterative code,sic),但不限于此。一般来说,本文中的代码设计原则可以被认为至少部分依赖于通过向编码器输入发送最近和过去的奇偶校验和系统符号来利用循环神经网络的记忆。解码器输入中使用相同的一般原则,这表示向解码器发送最近和过去接收到的有噪声的系统和奇偶校验符号。提出的方案也可应用于高阶调制方案。因此,可以设计适合传统和未来无线系统(例如lte和nr)的不同调制阶数的统一编码器和解码器架构。

[0100]

图1示出了根据本发明的示例的第一通信设备100。在图1所示的示例中,第一通信设备100包括第一发生器设备102、收发器104和存储器106。第一发生器设备102可以通过本领域已知的通信模块108耦合到收发器104和存储器106。第一通信设备100还可以包括耦合到收发器104的天线或天线阵列110,这表示第一通信设备100可以被配置为用于无线通信系统中的无线通信。第一通信设备100可以被配置用于执行某些动作在本公开中可以理解为表示第一通信设备100包括被配置用于执行所述动作的合适模块,例如第一发生器设备

102和收发器104。

[0101]

第一通信设备100的第一发生器设备102可以被称为一个或多个通用中央处理单元(central processing unit,cpu)、一个或多个数字信号处理器(digital signal processor,dsp)、一个或多个专用集成电路(application-specific integrated circuit,asic)、一个或多个现场可编程门阵列(field programmable gate array,fpga)、一个或多个可编程逻辑器件、一个或多个分立门、一个或多个晶体管逻辑器件、一个或多个分立硬件组件、一个或多个芯片组。第一通信设备100的存储器106可以是只读存储器、随机存取存储器或非易失性随机存取存储器(non-volatile random access memory,nvram)。第一通信设备100的收发器104可以是收发器电路、功率控制器、天线或与其它模块或设备通信的接口。在示例中,第一通信设备100的收发器104可以是单独的芯片组,也可以与第一发生器设备102集成在一个芯片组中。而在一些示例中,第一通信设备100的第一发生器设备102、收发器104和存储器106集成在一个芯片组中。

[0102]

根据本发明的示例,第一通信设备100被配置为基于在第一信道510中向第二通信设备300发送的系统符号集合和在第二信道520中从第二通信设备300接收的对应系统符号集合来获得第一噪声值集合,参见图5和图6。系统符号集合与对应于信息比特集合并从k=1,2,...,k索引的信息符号集合相关联,其中,k是整数。

[0103]

第一通信设备100还被配置为:对于k=1:

[0104]

使用第一发生器设备102并基于系统符号集合中的第一系统符号和第一噪声值集合中的第一噪声值,生成第一奇偶校验符号集合p1,

[0105]

在第一信道510中向第二通信设备300发送第一奇偶校验符号集合p1,

[0106]

在第二信道520中从第二通信设备300接收第一对应奇偶校验符号集合

[0107]

对于k=2,...,k:

[0108]

i)基于发送的第k-1奇偶校验符号集合p

k-1

和接收的第k-1奇偶校验符号集合,获得第k-1噪声值集合,

[0109]

ii)使用第一发生器设备102并基于第k系统符号、第一噪声值集合中的第k到第k-δ

tx

噪声值以及第k-1到第噪声值集合,生成第k奇偶校验符号集合pk,其中,δ

tx

和是整数,对应于第l奇偶校验符号,其中,l=1,2,...,p,p是信息比特集合中的每个信息比特的奇偶校验符号的数量,

[0110]

iii)在第一信道510中向第二通信设备300发送第k奇偶校验符号集合pk,

[0111]

iv)在第二信道520中从第二通信设备300接收第k对应奇偶校验符号集合

[0112]

第一通信设备100被配置为重复步骤i)至iv),直到k=k。

[0113]

图2示出了可以在如图1所示的第一通信设备100中执行的对应方法200的流程图。方法200包括基于在第一信道510中向第二通信设备300发送的系统符号集合和在第二信道520中从第二通信设备300接收的对应系统符号集合来获得(202)第一噪声值集合。系统符号集合与对应于信息比特集合并从k=1,2,...,k索引的信息符号集合相关联,其中,k是整数。

[0114]

方法200还包括:对于k=1:

[0115]

使用第一发生器设备102并基于系统符号集合中的第一系统符号和第一噪声值集

合中的第一噪声值,生成(204)第一奇偶校验符号集合p1,

[0116]

在第一信道510中向第二通信设备300发送(206)第一奇偶校验符号集合p1,

[0117]

在第二信道520中从第二通信设备300接收(208)第一对应奇偶校验符号集合

[0118]

所述方法200还包括:对于k=2,...,k:

[0119]

基于发送的第k-1奇偶校验符号集合p

k-1

和接收的第k-1奇偶校验符号集合,获得(210)第k-1噪声值集合,

[0120]

使用第一发生器设备102并基于第k系统符号、第一噪声值集合中的第k到第k-δ

tx

噪声值以及第k-1到第噪声值集合,生成(212)第k奇偶校验符号集合pk,其中,δ

tx

和是整数,对应于第l奇偶校验符号,其中,l=1,2,...,p,p是信息比特集合中的每个信息比特的奇偶校验符号的数量,

[0121]

在第一信道510中向第二通信设备300发送(214)第k奇偶校验符号集合pk,

[0122]

在第二信道520中从第二通信设备300接收(216)第k对应奇偶校验符号集合

[0123]

因此,在方法200中重复步骤210至216,直到k=k。

[0124]

图3示出了根据本发明的示例的第二通信设备300。在图3所示的示例中,第二通信设备300包括第二发生器设备302、收发器304和存储器306。第二发生器设备302通过本领域已知的通信模块308耦合到收发器304和存储器306。第二通信设备300可以被配置用于无线通信系统中的无线通信。无线通信能力由耦合到收发器304的天线或天线阵列310提供。第二通信设备300被配置为执行某些动作在本公开中可以理解为表示第二通信设备300包括被配置为执行所述动作的合适模块,例如第二发生器设备302和收发器304。

[0125]

第二通信设备300的第二发生器设备302可以是指一个或多个通用cpu、一个或多个dsp、一个或多个asic、一个或多个fpga、一个或多个可编程逻辑器件、一个或多个分立门、一个或多个晶体管逻辑器件、一个或多个分立硬件组件以及一个或多个芯片组。第二通信设备300的存储器306可以是只读存储器、随机存取存储器或nvram。第二通信设备300的收发器304可以是收发器电路、功率控制器、天线或与其它模块或设备通信的接口。在示例中,第二通信设备300的收发器304可以是单独的芯片组,也可以与第二发生器设备302集成在一个芯片组中。而在一些示例中,第二通信设备300的第二发生器设备302、收发器304和存储器306集成在一个芯片组中。

[0126]

根据本发明的示例,第二通信设备300被配置为在第一信道510中从第一通信设备100接收系统符号集合。系统符号集合对应于与信息比特集合对应并从k=1,2,...,k索引的信息符号集合,其中,k是整数。第二通信设备300还被配置为在第二信道520中向第一通信设备100发送接收的系统符号集合。

[0127]

第二通信设备300还被配置为:对于k=1,2,...,k:

[0128]

i)在第一信道510中从第一通信设备100接收第k奇偶校验符号集合pk,

[0129]

ii)在第二信道520中向第一通信设备100发送第k对应奇偶校验符号集合

[0130]

iii)使用第二发生器设备302并基于接收的第k到第k-δ

rx

系统符号和接收的第k到第奇偶校验符号,确定第k信息符号,其中,δ

rx

和是整数,对应于第l奇偶校验符号,其中,l=1,2,...,p,p是信息比特集合中的每个信息比特的奇偶校验符号的数量。

[0131]

在示例中,第二通信设备300被配置为缓冲/存储从第一通信设备100接收的系统

符号集合和每个奇偶校验符号集合pk,其中,k=1,2,...,k。此后,缓冲的系统符号集合和奇偶校验符号集合被联合解码。系统符号集合和每个奇偶校验符号集合pk可以例如被缓冲/存储在存储器306中。

[0132]

图4示出了可以在如图3所示的第二通信设备300中执行的对应方法400的流程图。方法400包括在第一信道510中从第一通信设备100接收(402)系统符号集合。系统符号集合对应于与信息比特集合对应并从k=1,2,...,k索引的信息符号集合,其中,k是整数。方法400还包括在第二信道520中向第一通信设备100发送(404)接收的系统符号集合。

[0133]

方法400还包括:对于k=1,2,...,k:

[0134]

在第一信道510中从第一通信设备100接收(406)第k奇偶校验符号集合pk,

[0135]

在第二信道520中向第一通信设备100发送(408)第k对应奇偶校验符号集合

[0136]

使用第二发生器设备302并基于接收的第k到第k-δ

rx

系统符号和接收的第k到第奇偶校验符号,确定(410)第k信息符号,其中,δ

rx

和是整数,对应于第l奇偶校验符号,其中,l=1,2,...,p,p是信息比特集合中的每个信息比特的奇偶校验符号的数量。

[0137]

在示例中,方法400包括缓冲从第一通信设备100接收的系统符号集合和每个奇偶校验符号集合pk,其中,k=1,2,...,k。此后,缓冲的系统符号集合和奇偶校验符号集合被联合解码。

[0138]

图5示出了根据本发明的示例的无线通信系统500。无线通信系统500包括被配置为在无线通信系统500中操作的第一通信设备100和第二通信设备300。为了简单起见,图5所示出的无线通信系统500仅包括一个第一通信设备100和一个第二通信设备300。但是,无线通信系统500可以包括任何数量的第一通信设备100和任何数量的第二通信设备300,而不偏离本发明的范围。本公开中的无线通信系统包括但不限于lte、5g或未来的无线通信系统。

[0139]

在图5中,第一通信设备100被示为客户端设备,第二通信设备300被示为网络接入节点。但是,相反的情况是可能的。因此,第一通信设备100可以是客户端设备或网络接入节点或任何其它合适的通信设备;第二通信设备300可以是客户端设备或网络接入节点或任何其它合适的通信设备。

[0140]

本公开中的客户端设备包括但不限于:ue,例如智能手机、蜂窝电话、无绳电话、会话发起协议(session initiation protocol,sip)电话、无线本地环路(wireless local loop,wll)站、个人数字助理(personal digital assistant,pda)、具有无线通信功能的手持设备、连接到无线调制解调器的计算设备或其它处理设备、车载设备、可穿戴设备、接入回传一体化(integrated access and backhaul,iab)节点(例如移动汽车或安装在汽车中的设备)、无人机、设备到设备(device-to-device,d2d)设备、无线摄像机、移动站、接入终端、用户单元、无线通信设备、无线局域网(wireless local access network,wlan)站、支持无线功能的平板电脑、笔记本电脑嵌入式设备、通用串行总线(universal serial bus,usb)软件狗、无线用户驻地设备(customer-premises equipment,cpe)和/或芯片组。在物联网(internet of things,iot)场景中,客户端设备可以表示与另一无线设备和/或网络设备执行通信的机器或另一设备或芯片组。

[0141]

ue还可以被称为移动电话、蜂窝电话、具有无线能力的计算机平板电脑或笔记本电脑。在此上下文中,ue可以是例如便携式、口袋存储式、手持式、计算机组成式或车载式移

动设备,能够通过无线接入网与另一实体(例如另一个接收器或服务器)进行语音和/或数据通信。ue可以是站(station,sta),它是包含到无线媒体(wireless medium,wm)的、符合ieee 802.11的媒体接入控制(media access control,mac)和物理层(physical layer,phy)接口的任何设备。ue还可以被配置用于在3gpp相关的lte和lte-高级(lte-advanced)中、在wimax及其演进中以及在第五代无线技术(例如nr)中进行通信。

[0142]

本公开的网络接入节点包括但不限于:宽带码分多址(wideband code division multiple access,wcdma)系统中的nodeb、lte系统中的演进节点b(evolutional node b,enb)或演进nodeb(evolved nodeb,enodeb)、中继节点或接入点、车载设备、可穿戴设备或第五代(fifth generation,5g)网络中的gnb。此外,本文中的网络接入节点可以表示为无线网络接入节点、接入网络接入节点、接入点或基站,例如无线基站(radio base station,rbs),在一些网络中,根据使用的技术和术语,基站可以称为发送器、“gnb”、“gnodeb”、“enb”、“enodeb”、“nodeb”或“b节点”。基于传输功率,因此也基于小区大小,无线网络接入节点可以具有不同类别,例如,宏enodeb、家庭enodeb或微微基站。无线网络接入节点可以是站(station,sta),它是一个包括到无线媒体的、符合ieee 802.11的mac和phy接口的任何设备。无线网络接入节点也可以是对应于5g无线系统的基站。

[0143]

图6更详细地示出了根据本发明的示例的无线通信系统500中的第一通信设备100与第二通信设备300之间的交互。在图6中,方案可以被认为是两阶段过程,现在将详细描述。

[0144]

第一阶段

[0145]

第一阶段包括通过前向信道(本文中也表示为第一信道510)发送系统符号集合,以及通过反馈信道(本文中也表示为第二信道520)接收回送的对应系统符号。

[0146]

在第一通信设备100中,系统符号集合是从信息比特集合中获得的,而不添加任何冗余,例如没有编码过程。换句话说,调制信息比特集合以获得系统符号集合。在这方面,调制长度为l比特的信息块矢量m=(m1,...,m

l

),以获得要在第一信道510上发送的系统符号集合x=(x1,...,xk)。发送的矢量x被方差为σ2的独立高斯噪声n0破坏,因此第二通信设备300接收:

[0147][0148]

第二通信设备300缓冲/存储接收的矢量,并通过第二信道520将该接收的矢量回送或反馈给第一通信设备100。在第二信道520中发送并由第一通信设备100接收的回送的系统矢量可以写成:

[0149][0150]

其中,w0是第二信道520上的独立高斯噪声,方差为

[0151]

第二阶段

[0152]

在第一阶段之后,执行第二阶段。第二阶段包括迭代过程,其中,在迭代时刻k(其中,k={1,2,...,k})由奇偶校验符号发生器自动机fk(本文中也表示包括在第一通信设备100中的第一发生器设备102)生成奇偶校验符号集合pk。

[0153]

在迭代时刻k的奇偶校验符号集合pk表示为:

[0154][0155]

其中,p

k,l

(其中,1≤l≤p)表示迭代k的第l奇偶校验符号,p是针对每个信息比特生成的奇偶校验符号的数量。

[0156]

通过第一信道510发送的奇偶校验符号集合被独立高斯噪声nk~n(0,σ2)破坏,在第二通信设备300处创建接收的矢量

[0157]

然后,接收的奇偶校验符号集合在单位时间延迟后通过表示为第二信道520的另一加性白高斯噪声信道被发送回或回送到第一通信设备100,其中,噪声在统计上是独立的并且是高斯分布的

[0158][0159]

第一通信设备100可以使用来自第二通信设备300的该反馈来顺序地和自适应地决定/确定在下一个传输步骤中发送哪个奇偶校验符号集合。此外,接收的符号被缓冲在第二通信设备300中,以便稍后解码,这将在下面的公开中更详细地解释。

[0160]

在示例中,第一发生器设备102包括rnn,例如包括单层门控循环单元122、线性变换器124和线性激活函数126的rnn,参见图8。

[0161]

在第一发生器设备102中,第k时刻的输出状态或记忆用hk表示。时刻hk是在时刻k-1(表示为h

k-1

)第一发生器设备102的输入状态的非线性函数。这表示,在当前时刻,存在关于前一时刻发生的事情的记忆。这种特殊性使得能够通过连续状态学习大量的依赖关系。hk的长度为k,且h0=0。

[0162]

在时刻k第一发生器设备102的附加输入是在时刻k的信息符号,表示为xk,在时刻k系统符号上的噪声,表示为,以及在先前发送的奇偶校验符号集合和通过第二信道520从第二通信设备300接收的对应奇偶校验符号集合上的噪声。

[0163]

第一发生器设备102可以写成非线性映射函数fk,其中:

[0164]fk

:(ik,h

k-1

)

→

pkꢀꢀꢀ

(5)

[0165]

其中,ik表示在时刻k编码器自动机的实际输入,将在下一节中详细描述。

[0166]

在第二阶段,迭代时刻k对应于时刻k。在等式(4)中,第一通信设备100从第二通信设备300接收回送的奇偶校验符号集合,这些奇偶校验符号是先前生成的,并在时刻k-1从第一通信设备100发送到第二通信设备520。当执行了对应于时刻k=k的最后迭代时刻时,第二阶段的迭代停止。

[0167]

第一发生器设备102(也称为第一自动机)可以被认为是在任何给定时刻基于其输入和内部状态产生输出的设备。此外,在移动到下一时刻之前,内部状态被更新。第一发生器设备102可以由状态列表、其初始状态和触发转换到另一状态的输入定义。

[0168]

解码

[0169]

在阶段1和阶段2期间接收的系统符号集合和奇偶校验符号集合被第二通信设备300缓冲/存储。一旦接收完成,即在时刻k之后,第二通信设备300通过有效地使用神经网络结构解码接收的系统和奇偶校验符号集合的矢量。

[0170]

数学上,第二发生器设备302(也称为解码器自动机)可以被视为非线性映射函数g,该函数根据下式将接收的序列映射为估计的信息符号:

[0171][0172]

这可以如图7所示,其中,接收的符号集合可以写成在阶段1和阶段2期间缓冲的接收的系统和奇偶校验符号集合:

[0173][0174]

更准确地说,(其中,1≤k’≤k)在完成阶段1和阶段2给出的两步编码过程后包括缓冲的接收的系统和奇偶校验符号集合。

[0175]

在示例中,第二发生器设备302是rnn,例如双向gru,该rnn在接收的整个缓冲上进行处理,以获得对应于每个接收的(其中,1≤k’≤k)的估计符号如下所示:

[0176][0177]

第二发生器设备302可以使用双向gru来解码接收的码字。事实上,双向gru有利于在两个方向上跟踪信息,因为在这种结构中,有两个rnn一个堆叠在另一个之上,从而提供更高的可靠性。双向gru可以是单层或两层gru。

[0178]

第二发生器设备302可以由状态列表、其初始状态和触发转换到另一状态的输入定义。自动机的初始状态可以设置为零。

[0179]

在下文中,将更详细地解释第一通信设备100的编码器架构和第二通信设备300的解码器架构。

[0180]

图8示出了根据本发明的示例的提出的第一通信设备100的编码器架构。第一发生器设备102包括循环神经网络,该神经网络包括单层(或两层)门控循环单元122、线性变换器124和线性激活函数126。与传统方案相反,激活函数126是线性激活函数,与非线性激活函数相比,它在实践中允许具有较大值的奇偶校验符号而不饱和,并且还降低了复杂度。奇偶校验符号被进一步归一化,以获得要发送的零均值和单位方差序列。在归一化之后,可选的功率分配单元在发送的系统符号和奇偶校验符号之间分配功率,这在图8中未示出。

[0181]

数学上,在时刻k编码器的新输入(表示为ik)可以写成如下所示:

[0182][0183]

其中,xk是时刻k的信息符号,是大小为δ

tx

+1的系统符号上的噪声的矢量,其中,δ

tx

是正数,即δ

tx

≥0。

[0184]

在本文中将大小为δ

tx

+1的矢量xk表示为包含时刻k到时刻k-δ

tx

的系统符号的系统符号的矢量,使用以下表示法:

[0185][0186]

其中,t表示转置操作。

[0187]

用表示大小为δ

tx

+1的矢量,该矢量包含在时刻k到时刻k-δ

tx

在反馈信道上接收的系统符号的接收的系统符号集合。

[0188]

根据上述表示法,得到:

[0189][0190]

因此,在时刻k到时刻k-δ

tx

接收到的系统符号上的噪声的系统符号集合上的噪声可以表示为获得的矢量可以具有大小δ

tx

+1。

[0191]

可以看到,参数δ

tx

对应于在系统符号上定义的时间窗口。实际上,可以看出,矢量的第一元素是在时刻k系统符号集合上的噪声,后面的元素表示先前接收的δ

tx

系统符号,或在本文中使用的时刻k-1,k-2,...,k-δ

tx

系统符号上的噪声。

[0192]

将在时刻k-1到(其中,)接收的奇偶校验符号中的第l(其中,1≤l≤p)奇偶校验符号的矢量表示为q

k-1,l

。遵循上面介绍的表示法,得到:

[0193][0194]

在上面的等式中,第一个元素表示时刻k-1的第l奇偶校验符号,后面的元素表示直到时刻k-1-γ

l

的第l奇偶校验符号。

[0195]

还将表示为时刻k-1到(其中,)接收的有噪声的奇偶校验符号的接收的有噪声的矢量的第l奇偶校验符号。可以写成:

[0196][0197]

因此,通过堆叠所有获得的列矢量来创建矢量(其中,l=1,2,...,p),其中,p是针对每个信息比特生成的奇偶校验符号的数量。因此,得到:

[0198][0199]

可以为q

k-1,l

(其中,l=1,2,...,p)写出类似的方程,以获得q

k-1

[0200][0201]

因此,矢量表示在时刻k-1到奇偶校验符号上的噪声,先前时刻为该矢量的大小为可以看到,对应于在第一通信设备100中在第l奇偶校验符号上定义的时间窗口。

[0202]

图9更详细地示出了所提出的第二通信设备300的解码器架构。第二发生器设备302可以是如前所述的rnn,包括双向单层门控循环单元322、线性变换器324和线性激活函数326。在示例中,第二发生器设备302包含仅单层双向gru单元,与使用两层双向gru的传统方案相比,单层双向gru单元减少了要训练和处理的变量数量,因此具有显著降低计算复杂度的优点。至于激活函数326,它可以被第一通信设备100的对应编码器的线性函数取代,从而允许更高的输出动态性并且降低实现的复杂度。

[0203]

包括缓冲的接收的奇偶校验符号和系统符号的在时刻k’(其中,1≤k’≤k)第二发生器设备302的输入可以表示为其中:

[0204][0205]

其中,

[0206][0207]

可以看出,的第一元素是在时刻k’的接收的系统符号,后面的元素表示在时刻k’之前的接收的δ

rx

系统符号。是一个大小为(δ

rx

+1)

×

1矢量,假设已经考虑了δ

rx

是整数值,其中,δ

rx

≥0。可以看到,参数δ

rx

对应于在接收的系统符号上定义的时间窗口。

[0208]

使用表示时刻k’的接收的第l奇偶校验符号和先前接收的(其中,)奇偶校验符号的矢量。更精确地,表示从时刻k

′

到时刻的接收的第l有噪声的奇偶校验符号的矢量。可以写成:

[0209][0210]

矢量可以通过堆叠所有列矢量,l=1,2,...,p,其中,p是分别针对每个信息比特生成的奇偶校验符号的数量。因此,矢量为:

[0211][0212]

等式(19)中的矢量具有大小可以看到,对应于在接收器中第l奇偶校验符号上定义的时间窗口。

[0213]

复杂度评估

[0214]

在上述示例中用于第一通信设备100和第二通信设备300的基本神经网络是(单层或两层)门控循环单元,门控循环单元使用门控机制来跟踪和管理由choi在2014年首次提出的神经网络中的单元之间的信息流。gru的结构允许从大数据序列中捕获依赖关系,而不会使用门控原则丢弃来自序列的早期部分中的信息。

[0215]

在gru单元内执行的操作可以写成:

[0216]rk

=σ(w

ir

ik+b

ir

+w

hrhk-1

+b

hr

)

ꢀꢀꢀ

(20)

[0217]

zk=σ(w

iz

ik+b

iz

+w

hzhk-1

+b

hz

)

ꢀꢀꢀ

(21)

[0218]

nk=tanh(w

in

ik+b

in

+rk*(w

hhhk-1

+b

hn

))

ꢀꢀꢀ

(22)

[0219]hk

=(1-zk)*nk+zk*h

k-1

ꢀꢀꢀ

(23)

[0220]

其中,大小为k

×

1的hk是在时刻k的隐藏状态,ik是在时刻k的输入,h

k-1

是在时刻k-1的层的隐藏状态或在时刻0的初始隐藏状态,由h0表示,rk、zk、nk分别是重置门、更新门和新门。σ是sigmoid函数;*是hadamard乘积;w

xy

和b

xy

表示训练的参数。

[0221]

更新门和重置门通过使用当前输入数据和先前隐藏状态计算输出。更新门和重置门还控制需要为未来步骤保留多少过去信息。

[0222]

在多层gru中,第l层(l≥2)的输入是前一层的隐藏状态

[0223]

至于对大小为k

×

1的输出状态数据hk应用线性变换的线性变换,可以像图8和图9

中捕获的那样写成:

[0224]

pk=a

khk

+bkꢀꢀꢀ

(24)

[0225]

其中,ak和bk表示训练的参数。

[0226]

gru和线性变换的计算复杂度是通过计算要训练的变量的大小和总数来计算的。可以看出,编码器和解码器的复杂度主要由隐藏状态hk的大小和相同大小的训练的参数决定。训练的变量数量为k3的数量级,如表1所示。即使对于中等值的信息符号/比特k,该值也会变得相当大。

[0227]

表1:用于编码器和解码器的训练的变量数量

[0228] 训练的变量数量两层gru编码器和线性变换≈6k3单层gru编码器和线性变换≈3k3解码器(两层双向gru)≈12k3[0229]

与使用两层gru时为≈18k3相比,用于单层gru编码器和两层双向gru解码器的编码和解码的训练的变量总数为≈15k3。

[0230]

所提出的方案要求编码器和解码器中循环神经网络的输入变量具有更高的维度。但是,计算复杂度仍然由作为参数δ

tx

,δ

rx

,γ

tx

,γ

rx

<<k的隐藏状态的大小决定。所提出的方案允许使用单层双向gru解码器,与传统方案的两层双向gru解码器相比,单层双向gru解码器具有相当低的计算复杂度。

[0231]

可以参考表1,对于上面提出的使用单层gru编码器和单层双向gru解码器的情况,总计算复杂度为3k3+6k3=9k3。与计算复杂度分别为15k3和18k3的传统方案相比,该方案的计算复杂度降低了约40%至50%。

[0232]

扩展到高阶调制

[0233]

图10示出了具有较高se的代码的功能框图,示出了训练过程。需要说明的是,第一通信设备100的编码器和第二通信设备300的解码器是联合训练的。

[0234]

训练过程设备700包括成本函数计算器702、神经网络(neural network,nn)权重计算器704和开关706,该开关706被配置为根据来自nn权重计算器704的输入在第一成本函数计算器712与第二成本函数计算器712

′

之间切换nn权重计算器块704。

[0235]

当bpsk调制用于系统符号时,使用二进制交叉熵作为成本函数(即第一成本函数计算器612)执行训练。在这种情况下,损失函数的输入是实际和估计的信息比特,在图10中分别用m

train-bit

和表示,其中,所示的开关606位于位置1,该位置指示用于bpsk调制的成本函数计算。

[0236]

但是,对于高阶调制,例如,当qpsk、16qam或32qam用于系统符号时,使用最小平方误差作为输入和估计的非二进制符号(在图10中分别用x

train-sym

和表示)而不是二进制比特的成本函数来完成训练。这对应于所示的开关606在位置2,指示在输入符号而不是比特上,即在第二成本函数计算器612

′

中,执行成本函数计算。

[0237]

例如,当使用传统的16qam将信息比特调制为系统符号时,信息比特被映射到等效的4个pam实部和虚部符号,并组合成一个复符号。

[0238]

在一般情况下,矩形qam信号星座具有明显的优点,即易于生成为相位正交载波中

的pam信号。对于矩形信号m-qam星座,其中,m=2

l

(l为偶数),qam信号星座相当于正交载波上的两个pam信号,每个pam信号具有个信号点。

[0239]

因此,对于高阶调制,编码器基于发送的pam系统符号和通过第二信道520接收的pam系统符号生成实奇偶校验符号。两个连续的实奇偶校验符号组合成一个复符号。在这种情况下,rnn记忆被减少到k=l/l,其中,l是等效pam调制的大小,因为l是信息比特的数量。

[0240]

解码器也被修改,以避免在执行解码时非二进制符号的缩放。对于编码和传输,奇偶校验和系统符号在示例中被进一步归一化,以获得要传输的零均值和单位方差序列。

[0241]

成本函数计算单元是通用单元,可以在任何神经网络系统中找到,该神经网络系统将最小平方误差或二进制交叉熵测量应用于如上所述通过所示开关的位置选择的输入。nn权重计算块包含在训练过程结束时获得的最终权重。

[0242]

等式(24)中所示的线性变换将线性变换应用于大小为k

×

1的输出状态hk,以产生大小为p的奇偶校验符号序列。因此,可以通过修改输出的大小(可训练参数ak的大小)使用相同的输出hk状态,生成不同大小的奇偶校验符号序列,并因此训练系统。因此,可以为相同的输出状态hk设想打孔或重复模式。

[0243]

更准确地,ak的大小是p

×

k,其中,p是可以调整的。例如,p=2时,将针对每个信息比特生成两个奇偶校验符号,从而考虑系统比特产生速率为的代码。对于p=1,将针对每个信息比特生成一个奇偶校验符号,从而产生速率为的代码,从而实现打孔。

[0244]

信令方面

[0245]

如前所述,编码器和解码器是联合训练的。当所提出的代码正在发送/接收数据时,甚至在训练期间,第一通信设备100和第二通信设备100都应对设计参数(本文中也称为信令参数)具有相同了解。当mcs、速率或频谱效率(spectral efficiency,se)等系统要求发生变化时,设计参数也发生变化。

[0246]

上述对深度学习编码器和解码器的系统要求可以通过选择具有可变速率的深度学习代码来定义,以具有与传统代码相同se的方式,并且se可以定义如下:

[0247][0248]

其中,n

re

表示用于发送获得的码字的资源元素(或复符号)的数量,l是信息比特的数量。

[0249]

可以考虑新的要求,例如sic码的速率,表示为r

sic

,定义如下:

[0250][0251]

在示例中,这些参数可以通过图5中所示的控制器600用信号发送到第一通信设备100和第二通信设备300。控制器600可以放置在或在物理上位于与第一通信设备100相同的设备中,或第二通信设备300中。

[0252]

在示例中,参数可以在控制消息610中从第一通信设备100用信号发送到第二通信设备300。在一个示例中,控制消息610指示参数k和p。换句话说,第一通信设备100被配置为向第二通信设备300发送控制消息610,其中,控制消息610指示k和p。相应地,第二通信设备300被配置为从第一通信设备100接收控制消息610,其中,控制消息610指示参数k和p。

[0253]

在其它示例中,控制消息610还指示表示接收的系统符号的时间窗口的第一参数δ

rx

和表示接收的奇偶校验符号的时间窗口的第二参数。

[0254]

在另外示例中,参数可以由lte和nr的标准预先配置,并且为第一通信设备100和第二通信设备300所知。

[0255]

表2中给出了先前和其它设计参数的非详尽列表。这些参数可以基于系统要求(例如目标调制阶数、sic码的速率和频谱效率)快速变化在一个或多个控制消息、每个传输时间间隔中动态地用信号发送,或者在系统要求缓慢变化时半静态或静态地配置或预配置。

[0256]

表2:根据系统要求用信号发送的参数

[0257][0258]

上述码字级或比特级权重代表在系统符号/比特或奇偶校验符号上应用的潜在标量可训练权重,同时保持恒定的平均发送功率约束。这些可训练的权重可以被通知为为对于所有奇偶校验比特都是相等的,或者可以被认为是不同的。

[0259]

图11示出了对应于从上述过程获得的nr的mcs 13的高阶调制的性能。评估假设如表3中所示。可以看出,对于高于2db的snr,所获得的代码的性能均优于nr-ldpc码。例如,对于bler=10

–4,该增益约为2db。

[0260]

表3:模拟假设

[0261][0262]

提出的架构的模拟结果

[0263]

还针对p=2速率为1/3和调制系统符号考虑的不同调制阶数来评估提出的迭代代码设计。训练过程和其它模拟参数如上所述考虑。

[0264]

对于这些评估,考虑了对于第一通信设备100,表4示出了用于第一通信设备100的详细选择参数。

[0265]

表4:速率为1/3的发送器(bpsk、qpsk和16qam)

[0266][0267]

第二通信设备300的接收器参数如表5中所示,其中,对于第二通信设备300,

[0268]

表5:速率为1/3的接收器(bpsk、qpsk和16qam)一单层双向gru

[0269][0270]

图12示出了bpsk速率为1/3时的bler与snr-训练snr=0db。图13示出了qpsk速率为1/3时的bler与snr-训练snr=4db。图14示出了16qam速率为1/3时的bler与snr-训练snr=10db。

[0271]

在图12至图14中,星号标记的曲线表示使用根据传统方案的架构的参考案例。在这种情况下,第一通信设备100中使用单层gru,第二通信设备300中使用两层双向gru。三角形标记的曲线示出了使用传统架构的相同参考,其中,在第一通信设备100侧具有更高的计算复杂度的两层gru,如上所述。方形标记的曲线示出了新提出的架构。第一通信设备100中的两个新架构都使用单层gru,具有如在表4中捕获的延迟版本的输入。事实上,用于第一通信设备100的新架构是统一设计的,因此是通用架构。

[0272]

测试两个不同的第二通信设备,用于如在表5中捕获的第一通信设备100中使用的新代码设计和架构。第二通信设备使用接收的系统比特/符号的一个延迟版本和两个奇偶校验符号。另一个第二通信设备仅使用一个时间延迟和两个时间延迟的系统位/符号的移位版本。两个第二通信设备都使用单层双向gru架构,与两层架构相比,该架构的复杂度要低得多。

[0273]

性能评估表明,与传统方案相比,根据该方案的第一通信设备100的编码器架构和第二通信设备300的解码器架构分别可以实现一个数量级的bler增益,计算复杂度为传统方案的一半。

[0274]

另外,根据本发明的示例的任一方法可以在具有代码装置的计算机程序中实现,该计算机程序当由处理装置运行时,使处理装置执行方法步骤。计算机程序包括在计算机程序产品的计算机可读介质中。计算机可读介质基本上可以包括任何存储器,例如只读存储器(read-only memory,rom)、可编程只读存储器(programmable read-only memory,prom)、可擦除prom(erasable prom,eprom)、闪存、电eprom(electrically erasable prom,eeprom)或硬盘驱动器。

[0275]

此外,技术人员意识到,第一通信设备100和第二通信设备300的示例包括用于执行方案的功能、装置、单元、元件等形式的必要通信能力。其它此类装置、单元、元件和功能的示例为:处理器、存储器、缓冲器、控制逻辑、编码器、解码器、速率匹配器、去速率匹配器、映射单元、乘法器、决策单元、选择单元、开关、交织器、解交织器、调制器、解调器、输入、输出、天线、放大器、接收单元、发送单元、dsp、msd、tcm编码器、tcm解码器、电源单元、电源馈线、通信接口、通信协议等,它们适当地布置在一起以执行方案。

[0276]

特别地,第一通信设备100和第二通信设备300的处理器可以包括中央处理单元(central processing unit,cpu)、处理单元、处理电路、处理器、专用集成电路(application specific integrated circuit,asic)、微处理器,或其它可以解释和执行指令的处理逻辑的一个或多个实例。表述“处理器”因此可表示包括多个处理电路的处理电路,多个处理电路例如上面提到的任何、一些或全部。处理电路还可以执行用于输入、输出以及处理数据的数据处理功能,数据处理包括数据缓冲和设备控制功能,设备控制功能例如呼叫处理控制、用户界面控制等。

[0277]

最后,应理解,本发明并不限于上述示例,而是还涉及且结合了所附独立权利要求范围内的所有示例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1