一种基于ZYNQ的数据采集传输方法、装置、设备及存储介质

一种基于zynq的数据采集传输方法、装置、设备及存储介质

技术领域

1.本发明涉及通信传输领域,特别涉及一种基于zynq的数据采集传输方法、装置、设备及存储介质。

背景技术:

2.数据采集系统已经普遍地应用到人们的日常生活工作当中;现在的数据采集系统通常通过单片机进行数据采集,但是单片机的采集系统存在采集速率慢,并且由于时钟频率较低而导致速率不能够满足实时数据传输处理的要求,进而限制了数据的采集传输效率。

技术实现要素:

3.本发明旨在至少解决现有技术中存在的技术问题之一。

4.为此,本发明提出一种基于zynq的数据采集传输方法,能够很好地提高数据的采集传输速率。

5.本发明还提出一种应用上述基于zynq的数据采集传输方法的基于zynq的数据采集传输装置。

6.本发明还提出一种应用上述基于zynq的数据采集传输方法的基于zynq的数据采集传输设备。

7.本发明还提出一种应用上述基于zynq的数据采集传输方法的计算机可读存储介质。

8.根据本发明第一方面实施例的基于zynq的数据采集传输方法,包括:

9.接收由上位机发送过来的配置参数并且进行解析,得到操作指令;

10.基于所述操作指令,通过pl端的状态机控制adc模块进行数据采集并且将采集到的数据写入存储器;

11.从所述存储器中读取数据并且将数据传输到上位机。

12.根据本发明实施例的基于zynq的数据采集传输方法,至少具有如下有益效果:zynq芯片首先接收到上位机发送过来的配置参数,然后对配置参数进行解析处理,得出相应的操作指令;然后根据得到的操作指令,通过pl端的状态机控制adc模块进行数据采集处理,并且将采集到的数据写入存储器中;然后从存储器中读取数据并且将数据传输到上位机;pl端为fpga,它是由可编程逻辑单元组成,fpga采用并行处理,可以大幅度地提高数据的采集传输效率,使得数据传输更加稳定、实时性更好,数据不易丢失。

13.根据本发明的一些实施例,所述接收由上位机发送过来的配置参数并且进行解析,得到操作指令,包括:

14.通过ps端的cpu接收由上位机发送过来的配置参数;

15.通过ps端的cpu对所述配置参数进行解析,得到操作指令。

16.根据本发明的一些实施例,所述基于所述操作指令,通过pl端的状态机控制adc模

块进行数据采集并且将采集到的数据写入存储器,包括:

17.通过ps端的cpu将所述操作指令发送到pl端的软处理器;

18.通过pl端的软处理器启动pl端的状态机;

19.通过pl端的状态机控制adc模块进行数据采集;

20.将采集到的数据写入存储器。

21.根据本发明的一些实施例,所述从所述存储器中读取数据并且将数据传输到上位机,包括:

22.当数据写满存储器的情况下,通过pl端的状态机向ps端的cpu发送触发信号;

23.触发ps端的cpu从所述存储器中读取数据;

24.通过ps端的cpu将读取的数据通过网口发送到上位机。

25.根据本发明的一些实施例,所述存储器为ram存储器。

26.根据本发明的一些实施例,所述adc模块包括两个4路通道的ad9228芯片。

27.根据本发明第二方面实施例的基于zynq的数据采集传输装置,包括:

28.处理单元,用于接收由上位机发送过来的配置参数并且进行解析,得到操作指令;

29.采集存储单元,用于基于所述操作指令,通过pl端的状态机控制adc模块进行数据采集并且将采集到的数据写入存储器;

30.读取发送单元,用于从所述存储器中读取数据并且将数据传输到上位机。

31.根据本发明的一些实施例,所述处理单元包括:

32.接收单元,用于通过ps端的cpu接收由上位机发送过来的配置参数;

33.解析单元,用于通过ps端的cpu对所述配置参数进行解析,得到操作指令。

34.根据本发明实施例的基于zynq的数据采集传输装置,至少具有如下有益效果:zynq芯片首先接收到上位机发送过来的配置参数,然后对配置参数进行解析处理,得出相应的操作指令;然后根据得到的操作指令,通过pl端的状态机控制adc模块进行数据采集处理,并且将采集到的数据写入存储器中;然后从存储器中读取数据并且将数据传输到上位机;pl端为fpga,它是由可编程逻辑单元组成,fpga采用并行处理,可以大幅度地提高数据的采集传输效率,使得数据传输更加稳定、实时性更好,数据不易丢失。

35.根据本发明第三方面实施例的基于zynq的数据采集传输设备,能够应用根据本发明上述第一方面实施例的基于zynq的数据采集传输方法。

36.根据本发明实施例的基于zynq的数据采集传输设备,至少具有如下有益效果:zynq芯片首先接收到上位机发送过来的配置参数,然后对配置参数进行解析处理,得出相应的操作指令;然后根据得到的操作指令,通过pl端的状态机控制adc模块进行数据采集处理,并且将采集到的数据写入存储器中;然后从存储器中读取数据并且将数据传输到上位机;pl端为fpga,它是由可编程逻辑单元组成,fpga采用并行处理,可以大幅度地提高数据的采集传输效率,使得数据传输更加稳定、实时性更好,数据不易丢失。

37.根据本发明第四方面实施例的计算机可读存储介质,能够应用根据本发明上述第一方面实施例的基于zynq的数据采集传输方法。

38.根据本发明实施例的计算机可读存储介质,至少具有如下有益效果:zynq芯片首先接收到上位机发送过来的配置参数,然后对配置参数进行解析处理,得出相应的操作指令;然后根据得到的操作指令,通过pl端的状态机控制adc模块进行数据采集处理,并且将

采集到的数据写入存储器中;然后从存储器中读取数据并且将数据传输到上位机;pl端为fpga,它是由可编程逻辑单元组成,fpga采用并行处理,可以大幅度地提高数据的采集传输效率,使得数据传输更加稳定、实时性更好,数据不易丢失。

39.本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

40.本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:

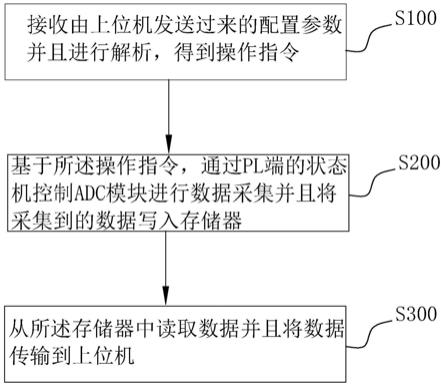

41.图1为本发明实施例一的基于zynq的数据采集传输方法的工作流程图;

42.图2为本发明实施例一的基于zynq的数据采集传输方法中的接收参数并且对参数进行解析的工作流程图;

43.图3为本发明实施例一的基于zynq的数据采集传输方法中的采集数据并且对数据进行存储的工作流程图;

44.图4为本发明实施例一的基于zynq的数据采集传输方法中的读取数据并且对数据进行发送的工作流程图;

45.图5为本发明实施例一的基于zynq的数据采集传输方法中的pl端的状态机运行的工作流程图;

46.图6为本发明实施例一的基于zynq的数据采集传输方法中的adc模块和fpga的结构示意图;

47.图7为本发明实施例二的基于zynq的数据采集传输装置的结构示意图;

48.图8为本发明实施例三的基于zynq的数据采集传输设备的结构示意图。

具体实施方式

49.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

50.本发明的描述中,除非另有明确的限定,设置、连接等词语应做广义理解,所属技术领域技术人员可以结合技术方案的具体内容合理确定上述词语在本发明中的具体含义。

51.说明:zynq芯片包括了ps端和pl端;ps端包括了硬核处理器的cpu,pl端包括了软处理器的fpga;应用zynq芯片,既可以利用了cpu的通用处理功能,也采用了fpga的可编程逻辑部分。针对高速数据采集和传输需要一种高速接口,所以fpga的并行处理功能可以很好的完成。其次针对采集系统中不同时钟域,利用bram资源将异步数据做了同步处理。

52.实施例一

53.参照图1,本发明实施例一提供了一种基于zynq的数据采集传输方法,其中的一种实施例包括但不限于以下步骤:

54.步骤s100,接收由上位机发送过来的配置参数并且进行解析,得到操作指令。

55.在本实施例中,本步骤接收由上位机发送过来的配置参数;配置参数中可以包括需要配置的各种工作模式,比如需要通过spi接口配置射频端发射多少赫兹线性调频信号

以及重复周期等相关信号,而对采集要求的配置则包括:本次采集需要采集多少帧数据,一帧数据需要adc采样多少个点;然后对采集的配置参数进行解析,从而得到相应的操作指令;用户可以通过上位机灵活地对各种参数进行修改配置,使得数据采集传输系统能够被灵活控制。

56.步骤s200,基于所述操作指令,通过pl端的状态机控制adc模块进行数据采集并且将采集到的数据写入存储器。

57.在本实施例中,本步骤基于上述获得的操作指令,通过pl端的状态机控制adc模块进行数据采集并且将采集到的数据写入存储器中;pl端的状态机由verilog语言编写而成,利用状态机来控制adc模块进行数据采集,很好地提升了数据采集传输的效率。

58.步骤s300,从所述存储器中读取数据并且将数据传输到上位机。

59.在本实施例中,本步骤通过自相关矩阵计算结果波形,并且在计算结果波形的过程中结合了恒模约束和稀疏频率约束,最后得到结果波形,能够很好地减少波形之间相互干扰的情况,提升检测效果。

60.参照图2,在步骤s100中,可以包括但不限于以下步骤:

61.步骤s110,通过ps端的cpu接收由上位机发送过来的配置参数。

62.在本实施例中,本步骤zynq采集板中的ps端的cpu接收由上位机发送过来的配置参数;并且上位机通过串口的方式将配置参数发送到zynq采集板。

63.步骤s120,通过ps端的cpu对配置参数进行解析,得到操作指令。

64.在本实施例中,本步骤ps端的cpu能够对配置参数进行解析处理,从而将上位机发送过来的配置参数转换为相应的操作指令。

65.参照图3,在步骤s200中,可以包括但不限于以下步骤:

66.步骤s210,通过ps端的cpu将操作指令发送到pl端的软处理器。

67.在本实施例中,本步骤ps端的cpu将解析得到的操作指令发送到pl端的软核处理器,从而控制软核处理器完成相应的操作。

68.步骤s220,通过pl端的软处理器启动pl端的状态机。

69.在本实施例中,本步骤pl端的软处理器启动预先编写的状态机,为了状态机的运行做好前提准备。

70.步骤s230,通过pl端的状态机控制adc模块进行数据采集。

71.在本实施例中,本步骤状态机控制adc模块进行数据采集,很好地提高了数据采集传输的效率。

72.步骤s240,将采集到的数据写入存储器。

73.在本实施例中,本步骤将采集到的数据写入存储器中,为了后续的数据传输做好准备。

74.参照图4,在步骤s300中,可以包括但不限于以下步骤:

75.步骤s310,当数据写满存储器的情况下,通过pl端的状态机向ps端的cpu发送触发信号。

76.在本实施例中,本步骤当数据写满存储器的时候,状态机就会向ps端的cpu发送触发信号,通知cpu进行采集数据的读取传输。

77.步骤s320,触发ps端的cpu从所述存储器中读取数据。

78.在本实施例中,本步骤cpu接收到状态机发送过来的触发信号之后,触发ps端的中断,进而cpu从存储器中读取数据。

79.步骤s330,通过ps端的cpu将读取的数据通过网口发送到上位机。

80.在本实施例中,本步骤cpu从存储器中读取数据并且触发网口,通过udp协议将数据发送到上位机,从而能够在上位机中进行后续的信号处理与分析。

81.在本发明的一些具体实施例中,存储器为ram存储器。ram存储器为常用的一种存储器,对数据的存储速率较快。

82.在本发明的一些具体实施例中,adc模块包括两个4路通道的ad9228芯片。adc模块由两个4路通道的ad9228芯片组合而成,使得能够实现8通道的数据采集传输处理,很好地提高了数据的采集传输效率。

83.参照图5,在本发明的一些具体实施例中,状态机的运行过程如下:首先一开始状态机处于空闲状态sz,一直等待上位机发送的开始指令,如果上位机的指令过来了,则由空闲状态跳转到sza状态。在此状态会判断需要此次所需的帧数,如果帧数少于此次采集帧数的条件,则跳转到下一个状态s0,否则就会跳转到空闲状态sz,进入s0状态之后,此时状态机会等待射频前端发送回来的反馈脉冲,如果接收到该脉冲,则由s0在此再做判断,如果此时采集的chirps满足一帧需要保存的个数,则会跳转到下一个判断,此时如果满足跳过的chirps数就会转到sza状态否则会转到s0状态,继续判断一帧需要跳过的chirps。如果一开始不满足一帧保存的chirps数,则状态转到s0a,进而判断是否需要丢弃一段稳定采集的废chirps数,满足的话就会跳转到s1状态,而行帧头编码。数据写完之后就会进入下一个状态s2,此状态会将采集的数据写入ram里,当写满一次ram给一个触发信号,进而触发ps端的中断,cpu进而将状态机写入ram里面的数据调入到内存中,并触发网口,通过udp协议上传数据。

84.参照图6,在本发明的一些具体实施例中,adc芯片采用两个4路通道的ad9228组合而成,模拟信号的输入通过采用60针的samtec连接到射频前端。而adc工作的时钟是由fpg a内部的时钟通过可编程i/o输出提供,与此同时adc芯片会返回两路时钟,分别为数据输出时钟(dco)和数据帧输出时钟(fco)。fpga在接收adc输出的lvds串行信号时,需要考虑dco边沿与数据边沿所存在的相位差,只有设置合理的时序约束,以满足建立时间和保持时间,消除亚稳态。同时需要与数据确定相位关系,dco也要和fco确定相位关系,因为仅靠dco采集到的数据虽然是正确的,但只是一串比特流,而不能确定数据的最高位或者最低位,最有通过fco进行比特序列调整才可以恢复数据。数据与fco的相位基本同步,fco的上升沿与数据的最高位对齐。利用双口bram,作乒乓操作,加快数据读取,并对不同时钟域数据做了同步处理。

85.通过上述方案可知,zynq芯片首先接收到上位机发送过来的配置参数,然后对配置参数进行解析处理,得出相应的操作指令;然后根据得到的操作指令,通过pl端的状态机控制adc模块进行数据采集处理,并且将采集到的数据写入存储器中;然后从存储器中读取数据并且将数据传输到上位机;pl端为fpga,它是由可编程逻辑单元组成,fpga采用并行处理,可以大幅度地提高数据的采集传输效率,使得数据传输更加稳定、实时性更好,数据不易丢失。

86.实施例二

87.参照图7,本发明实施例二提供了一种基于zynq的数据采集传输装置1000,包括:处理单元1100,用于接收由上位机发送过来的配置参数并且进行解析,得到操作指令;采集存储单元1200,用于基于所述操作指令,通过pl端的状态机控制adc模块进行数据采集并且将采集到的数据写入存储器;

88.读取发送单元1300,用于从所述存储器中读取数据并且将数据传输到上位机。

89.在本发明的一些具体实施例中,处理单元1100包括:

90.接收单元1110,用于通过ps端的cpu接收由上位机发送过来的配置参数;

91.解析单元1120,用于通过ps端的cpu对所述配置参数进行解析,得到操作指令。

92.需要说明的是,由于本实施例中的基于zynq的数据采集传输装置与上述实施例一中的基于zynq的数据采集传输方法基于相同的发明构思,因此,方法实施例一中的相应内容同样适用于本系统实施例,此处不再详述。

93.通过上述方案可知,zynq芯片首先接收到上位机发送过来的配置参数,然后对配置参数进行解析处理,得出相应的操作指令;然后根据得到的操作指令,通过pl端的状态机控制adc模块进行数据采集处理,并且将采集到的数据写入存储器中;然后从存储器中读取数据并且将数据传输到上位机;pl端为fpga,它是由可编程逻辑单元组成,fpga采用并行处理,可以大幅度地提高数据的采集传输效率,使得数据传输更加稳定、实时性更好,数据不易丢失。

94.实施例三

95.参照图8,本发明实施例三提供了一种基于zynq的数据采集传输设备400,包括至少一个控制处理器401和用于与至少一个控制处理器401通信连接的存储器402;存储器402存储有可被至少一个控制处理器401执行的指令,指令被至少一个控制处理器401执行,以使至少一个控制处理器401能够执行上述实施例一的基于zynq的数据采集传输方法。

96.实施例四

97.本发明实施例四还提供了一种计算机可读存储介质,所述计算机可读存储介质存储有基于zynq的数据采集传输装置可执行指令,基于zynq的数据采集传输装置可执行指令用于使基于zynq的数据采集传输装置执行上述的基于zynq的数据采集传输方法,例如,执行以上描述的图1中的方法步骤s100至s300,实现图7中的单元1000

‑

1300的功能。

98.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示意性实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

99.尽管已经示出和描述了本发明的实施例,本领域的普通技术人员可以理解:在不脱离本发明的原理和宗旨的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1