一种同时接入数字和模拟室内机的双模智能对讲系统的制作方法

1.本发明涉及对讲系统领域,具体涉及一种同时接入数字和模拟室内机的双模智能对讲系统。

背景技术:

2.随着居民住宅的不断增加,小区的物业管理就显得日趋重要。楼宇对讲系统实现了生活的智能化也提高了生活环境的安全性。目前,楼宇对讲系统分为模拟对讲系统和数字对讲系统。传统的模拟对讲系统架构复杂,且音视频模拟信号长距离传输后受干扰比较严重,容易出现失真现象,另外模拟对讲系统的功能相对来说也比较单一,模拟对讲系统的这些不足之处,不仅严重影响了该系统的稳定性与可靠性,而且还无法满足不同品牌之间功能需求的差异性。

3.当前数字对讲系统正被广泛部署,数字可视对讲系统是一种创新的、全业务的ip数据业务网,相对于总线制传输的模拟对讲系统,数字对讲系统在布线和安装调试方面要方便得多,具有极强的稳定性和很强的扩展性,没有距离限制,其解决了许多上述模拟对讲系统不能解决的问题,但是对于已经安装了传统的模拟对讲系统的小区而言,全部升级成为数字对讲系统需要耗费的成本过高。

技术实现要素:

4.为了克服现有技术的不足,本发明的目的是提供一种同时接入数字和模拟室内机的双模智能对讲系统,兼顾模拟和数字对讲系统的优点,实现可以同时接入模拟和数字室内机01的双模智能对讲系统,以满足不同用户的需求。

5.为了达到上述目的,本发明所采用的技术方案是:提供一种同时接入数字和模拟室内机的双模智能对讲系统,包括mcu单元、数模单元、电源单元、网络接口单元、麦克风单元以及扬声器单元;所述mcu单元分别与所述数模单元、所述电源单元、所述网络接口单元、所述麦克风单元以及所述扬声器单元电性相连,所述电源单元还分别与所述数模单元、所述网络接口单元、所述麦克风单元以及所述扬声器单元电性相连,所述数模单元还分别接入数字室内机和模拟室内机;

6.所述电源单元用于为所述mcu单元、所述数模单元、所述网络接口单元、所述麦克风单元以及所述扬声器单元提供工作电源,所述网络接口单元用于所述mcu单元通过以太网与外部设备进行数据交换,所述存储单元用于存储所述mcu单元的处理数据;

7.所述数模单元用于将接入的所述数字室内机的数字信号和所述模拟室内机的模拟信号传送至所述mcu单元;所述mcu单元通过处理器内置的数模转换器和乘法器,将接收到的所述模拟室内机的模拟信号转换为数字信号,与接收到的所述数字室内机的数字信号进行通话模式切换,通过所述麦克风单元和所述扬声器单元实现所述数字室内机和所述模拟室内机对讲;

8.所述mcu单元包括处理器u5,电容c51、c52、c53,电阻r19、r20、r22、r23、r24、r25、

r26、r27、r31、r32;所述处理器u5的型号为a64youpiao;所述处理器u5的引脚2连接所述电阻r31的一端,所述电阻r31的另一端分别连接端子pa

‑

shdn和所述电阻r32的一端,所述端子pa

‑

shdn用于功放控制,所述电阻r32的另一端连接端子out_mcu_pa

‑

shdn,所述处理器u5的引脚16连接模拟地,所述处理器u5的引脚48、引脚44、引脚41、引脚38、引脚35以及引脚32相连后接地,所述处理器u5的引脚58、引脚59以及引脚60相连后接电源5v,所述处理器u5的引脚61和引脚62相连后接地,所述处理器u5的引脚63分别连接所述电容c53的一端和端子,所述电容c53的另一端接地,所述处理器u5的引脚76分别连接所述电容c51的一端和所述电容c52的一端,所述电容c51的另一端和所述电容c52的另一端相连后接地,所述处理器u5的引脚92和引脚93相连后接地,所述处理器u5的引脚94接电源1.8v,所述处理器u5的引脚95和引脚96相连后接端子,所述处理器u5的引脚97连接所述电阻r22的一端,所述电阻r22的另一端分别接io口gpio4和所述电阻r26的一端,所述电阻r26的另一端接端子out_mcu_gp4,所述处理器u5的引脚98连接所述电阻r23的一端,所述电阻r23的另一端分别接io口gpio5和所述电阻r27的一端,所述电阻r27的另一端接端子out_mcu_gp5,所述处理器u5的引脚100连接所述电阻r20的一端,所述电阻r20的另一端分别接io口gpio3和所述电阻r25的一端,所述电阻r25的另一端接端子out_mcu_gp3,所述处理器u5的引脚102连接所述电阻r19的一端,所述电阻r19的另一端分别接io口gpio2和所述电阻r24的一端,所述电阻r24的另一端接端子out_mcu_gp2;

9.所述处理器u5的引脚119连接端子uart3

‑

tx,用于串口数据发送;所述处理器u5的引脚118连接端子uart3

‑

rx,用于串口数据接收;所述处理器u5的引脚77连接端子bt

‑

uart

‑

rx,用于蓝牙串口数据接收;所述处理器u5的引脚67连接端子bt

‑

uart

‑

tx,用于蓝牙串口数据发送;所述处理器u5的引脚57连接端子mdio,为以太网管理接口;所述处理器u5的引脚56连接端子mdc,为以太网数据传输接口;所述处理器u5的引脚52连接端子rxd0,为数据接收信号线;所述处理器u5的引脚53连接端子rxd1,为数据接收信号线;所述处理器u5的引脚54连接端子refclko,为以太网时钟信号线;所述处理器u5的引脚50连接端子rxer,为接收数据错误提示信号线;所述处理器u5的引脚55连接端子txen,为数据传输使能信号线;所述处理器u5的引脚48连接端子txd0,为数据发送信号线;所述处理器u5的引脚49连接端子txd1,为数据发送信号线;所述处理器u5的引脚51连接端子crs

‑

dv,为以太网控制信号接口;所述处理器u5的引脚1连接端子lan_reset,用于连接以太网复位按钮;所述处理器u5的引脚96和引脚95相连后接端子dcdc1,用于传输dc信号;所述处理器u5的引脚24连接端子spkp,为音频正差分输出端;所述处理器u5的引脚25连接端子spkn,为音频负差分输出端;所述处理器u5的引脚19连接端子hpoutr,为右耳机接口;所述处理器u5的引脚20连接端子hpoutl,为左耳机接口;所述处理器u5的引脚7连接端子twi1

‑

sda,为twi接口的串行数据线;所述处理器u5的引脚8连接端子twi1

‑

sck,为twi接口的同步时钟线;所述处理器u5的引脚22连接端子linein_p,用于连接声卡插口;所述处理器u5的引脚23连接端子linein_n,用于连接声卡插口;所述处理器u5的引脚112、引脚111、引脚109以及引脚107分别连接端子sdc0

‑

d0、端子sdc0

‑

d1、端子sdc0

‑

d2以及端子sdc0

‑

d3,用于存储卡的数据读写;所述处理器u5的引脚113连接端子sdc0

‑

clk,用于存储卡的时钟控制;所述处理器u5的引脚110连接端子sdc0

‑

cmd,用于存储卡的读写控制;所述处理器u5的引脚108连接端子sdc0

‑

det,用于存储卡的检测;

10.所述数模单元包括单刀双掷模拟开关u15、u16、u17,数字信号接入器j1208,数字

信号传输器j11,电容c141、c143、c142、c144、c145、c146、c319、c149、c150、c151、c152、c318,电阻r159、r160、r161、r369、r370、r164、r367、r368、r165、r166、r168、r170、r337、r336、r167、r169、r171;所述数模单元包括单刀双掷模拟开关u15、u16、u17用于将所述模拟室内机的模拟信号传送至所述mcu单元,所述数字信号接入器j1208和所述数字信号传输器j11用于将所述数字室内机的数字信号传送至所述mcu单元;

11.所述单刀双掷模拟开关u15的引脚1接输出信号端line_out,所述单刀双掷模拟开关u15的引脚2接地,所述单刀双掷模拟开关u15的引脚3接输出信号端line_in_t,所述单刀双掷模拟开关u15的引脚4分别连接所述电容c141的一端和所述电阻r159的一端,所述电容c141的另一端和所述电阻r159的另一端相连后接地,所述单刀双掷模拟开关u15的引脚5分别连接所述电容c143的一端和电源3.3v,所述电容c143的另一端接地,所述单刀双掷模拟开关u15的引脚6连接所述io口gpio2;所述单刀双掷模拟开关u16的引脚1接输出信号端line_in_l,所述单刀双掷模拟开关u16的引脚2接地,所述单刀双掷模拟开关u16的引脚3接输出信号端mic_out,所述单刀双掷模拟开关u16的引脚4分别连接所述电容c144的一端和所述电阻r160的一端,所述电容c144的另一端和所述电阻r160的另一端相连后接地,所述单刀双掷模拟开关u16的引脚5分别连接所述电容c142的一端和电源3.3v,所述电容c142的另一端接地,所述单刀双掷模拟开关u16的引脚6连接所述io口gpio3;所述单刀双掷模拟开关u17的引脚1接输出信号端line_out,所述单刀双掷模拟开关u17的引脚2接地,所述单刀双掷模拟开关u17的引脚3接输出信号端mic_out_t,所述单刀双掷模拟开关u17的引脚4分别连接所述电容c146的一端和所述电阻r161的一端,所述电容c146的另一端和所述电阻r161的另一端相连后接地,所述单刀双掷模拟开关u17的引脚5分别连接所述电容c145的一端和电源3.3v,所述电容c145的另一端接地,所述单刀双掷模拟开关u17的引脚6连接所述io口gpio4;

12.所述数字信号接入器j1208的引脚1接端子mic_in,所述数字信号接入器j1208的引脚13和引脚2相连后接模拟地,所述数字信号接入器j1208的引脚5接地,所述数字信号接入器j1208的引脚6接电源5.2v,所述数字信号接入器j1208的引脚9连接所述电容c319的一端,所述电容c319的另一端接地,所述数字信号接入器j1208的引脚10连接所述电阻r370的一端,所述电阻r370的另一端连接所述数字信号传输器j11的引脚10,所述数字信号接入器j1208的引脚14连接所述电阻r369的一端,所述电阻r369的另一端连接所述数字信号传输器j11的引脚8,所述数字信号传输器j11的引脚1分别连接所述电容c150的一端和所述电阻r164的一端,所述电容c150的另一端接地,所述电容c150的一端还连接所述电容c149的一端,所述电容c149的另一端接地,所述电阻r164的另一端接电源12v,所述数字信号传输器j11的引脚2分别连接所述电阻r336的一端、所述电阻r165的一端以及所述电阻r166的一端,所述数字信号传输器j11的引脚3分别连接所述电阻r337的一端、所述电阻r168的一端以及所述电阻r170的一端,所述电阻r337的另一端与所述电阻r336的另一端相连后接地,所述电阻r165的另一端连接所述端子uart3

‑

tx,所述电阻r166的另一端连接所述端子bt

‑

uart

‑

rx,所述电阻r168的另一端连接所述端子bt

‑

uart

‑

tx,所述电阻r170的另一端连接所述端子uart3

‑

rx,所述数字信号传输器j11的引脚4分别连接所述电阻r169的一端、所述电阻r167的一端以及所述电容c151的一端,所述电阻r167的一端还连接所述电阻r171的一端,所述电阻r171的另一端与所述电容c151的另一端相连后接地,所述电阻r169的另一端

连接所述io口gpio5,所述电阻r167的另一端连接端子out_ad_rst,所述数字信号传输器j11的引脚6连接端子cvbsout,所述数字信号传输器j11的引脚5、引脚7、引脚9、引脚11以及引脚12相连后接地,所述数字信号传输器j11的引脚8还分别连接所述电容c318的一端和所述电阻r367的一端,所述电容c318的另一端接地,所述电阻r367的另一端接端子spk_out,所述数字信号传输器j11的引脚10还分别连接所述电容c152的一端和所述电阻r368的一端,所述电容c152的另一端接地,所述电阻r368的另一端连接所述端子mic_in。

13.进一步地,所述电源单元包括单片同步整流降压稳压器u1和u2,正向低压降稳压器u3,插座j1,整流器f1,共模电感l1,电感器l2和l3,mos管q1和q2,三极管q3和q4,极性电容c9、c11、c13、c33,发光二极管d5,二极管d1、d2、d3、d4、d6,电容c1、c2、c3、c4、c5、c6、c7、c10、c8、c12、c22、c23、c24、c14、c16、c15、c17、c18、c19、c20、c21、c39、c40、c41、c25、c27、c26、c28、c29、c30、c31、c32、c34、c35、c36、c37、c38,电阻r1、r7、r8、r4、r3、r5、r2、r6、r10、r12、r11、r13、r14、r17、r15、r18、r16;所述插座j1的引脚1和引脚4相连后接端子,所述插座j1的引脚2和引脚相连后分别接端子、输入电源12v、所述电容c2的一端,所述电容c2的一端还分别连接所述电容c3的一端和整流器f1的引脚1,所述插座的引脚4还分别连接所述电容c2的另一端和所述电容c3的另一端,所述整流器f1的引脚2分别连接所述电容c4的一端和所述电容c5的一端,所述电容c5的一端还连接所述共模电感l1的引脚1,所述电容c3的另一端还分别连接所述电容c4的另一端和所述电容c5的另一端,所述电容c5的另一端还连接所述共模电感的引脚2,所述共模电感的引脚3分别连接所述电容c6的一端和所述电容c7的一端,所述共模电感l1的引脚4连接所述电容c6的另一端,所述电容c7的另一端与所述电容c6的另一端相连后接地,所述电容c7的一端还连接所述二极管d1的正极,所述二极管d1的负极分别连接所述极性电容c9的正极和所述电容c10的一端,所述极性电容c9的负极接地,所述电容c10的另一端接地,所述电容c10的一端还分别连接所述极性电容c11的正极和所述电阻r1的一端,所述极性电容c11的负极接地,所述电阻r1的一端还分别连接所述mos管q1的漏极、所述mos管q2的漏极、所述电阻r3的一端、所述电容c8的一端以及所述电阻r4的一端,所述电阻r1的另一端连接所述二极管d3的负极,所述二极管d3的正极分别连接所述电阻r8的一端和所述电阻r7的一端,所述电阻r7的另一端接地,所述电阻r8的另一端连接所述三极管q4的基极,所述三极管q4的发射极接地,所述三极管q4的集电极分别连接所述电阻r4的另一端和所述三极管q3的基极,所述三极管q3的发射极接地,所述三极管q3的集电极连接所述电阻r5的一端,所述电容c8的另一端和所述电阻r3的另一端相连后接所述mos管q2的栅极,所述电容c8的另一端和所述电阻r3的另一端相连的连接点与所述电阻r5的另一端相连后接所述mos管q1的栅极,所述mos管q1的源极分别连接所述电容c1的一端、所述单片同步整流降压稳压器的引脚2以及所述电容c22的一端,所述电容c1的另一端和所述电容c22的另一端分别接地,所述mos管q2的源极分别连接电源12v和所述电容c12的一端,所述电容c12的另一端接地,所述电容c12的一端还分别连接所述极性电容c13的正极和所述电阻r2的一端,所述极性电容c13的负极接地,所述电阻r2的另一端分别连接所述二极管d2的正极和所述电阻r6的一端,所述电阻r6的另一端接地,所述二极管d2的负极分别连接所述正向低压降稳压器u3的引脚2和所述电容c37的一端,所述电容c37的一端还连接所述电容c38的一端,所述电容c37的另一端和所述电容c38的另一端相连后接地,所述正向低压降稳压器u3的引脚2还与引脚4相连后接所述电容c36的一端,所述电容c36的另一端接地,所

述正向低压降稳压器u3的引脚3分别连接所述电容c35的一端和所述电容c34的一端,所述电容c34的一端还连接所述电容c32的一端,所述电容c34的另一端和所述电容c35的另一端分别接地,所述单片同步整流降压稳压器u2的引脚1连接所述电容c25的一端,所述单片同步整流降压稳压器u2的引脚3分别连接所述电容c25的另一端和所述二极管d6的正极,所述二极管d6的负极接地,所述单片同步整流降压稳压器u2的引脚3分别连接所述电容c25的另一端相连后连接所述电感器l3的一端,所述电感器l3的另一端与所述电阻r15的一端、所述电容c26的一端、所述电容c28的一端、所述电容c29的一端、所述电容c30的一端、所述电容c31的一端、所述电容c32的一端、所述电阻r16的一端以及所述极性电容c33的正极相连,所述单片同步整流降压稳压器u2的引脚5与所述电阻r15的另一端和所述电容c26的另一端相连后接所述电阻r18的一端,所述电阻r18的另一端接地,所述电容r28的另一端和所述电容r29的另一端相连后接地,所述电容c30的另一端、所述电容c31的另一端、所述电容c32的另一端、所述发光二极管d5的负极、所述极性电容c33的负极分别接地,所述电阻r16的另一端连接所述发光二极管d5的正极,所述单片同步整流降压稳压器u2的引脚6连接所述电容c27的一端,所述电容c27的另一端连接所述电阻r17的一端,所述电阻r17的另一端接地,所述单片同步整流降压稳压器u2的引脚4和引脚9分别接地,所述单片同步整流降压稳压器u2的引脚8连接所述电容c41的一端,所述电容c41的另一端接地,所述单片同步整流降压稳压器u2的引脚7连接所述电阻r14的一端,所述电阻r14的另一端分别连接所述单片同步整流降压稳压器u2的引脚2和所述电容c40的一端,所述电容c40的另一端接地,所述电阻r14的另一端还分别连接电源12v和所述电容c39的一端,所述电容c39的另一端接地,所述单片同步整流降压稳压器u1的引脚2分别连接所述电阻r10的一端和所述电容c22的一端,所述单片同步整流降压稳压器u1的引脚7连接所述电阻r10的另一端,所述电阻r10的一端还连接所述电容c23的一端,所述电容c23的另一端接地,所述单片同步整流降压稳压器u1的引脚8连接所述电容c24的一端,所述电容c24的另一端接地,所述单片同步整流降压稳压器u1的引脚6连接所述电容c16的一端,所述电容c16的另一端连接所述电阻r12的一端,所述电阻r12的另一端接地,所述单片同步整流降压稳压器u1的引脚1连接所述电容c14的一端,所述电容c14的另一端与所述单片同步整流降压稳压器u1的引脚3相连后连接所述电感器l2的一端,所述单片同步整流降压稳压器u1的引脚3还连接所述二极管d4的负极,所述二极管d4的正极接地,所述电感器l2的另一端与所述电阻r11的一端、所述电容c15的一端、所述电容c17的一端、所述电容c18的一端、所述电容c19的一端、所述电容c20的一端以及所述电容c21的一端相连,所述单片同步整流降压稳压器u1的引脚5分别连接所述电阻r11的另一端、所述电容c15的另一端、所述电阻r13的一端,所述电阻r13的另一端接地,所述电容c17的另一端和所述电容c18的另一端相连后接地,所述电容c19的另一端、所述电容c20的另一端、所述电容c21的另一端分别接地,所述电容c21的一端还接电源5.1v。

14.进一步地,所述网络接口单元包括以太网phy层芯片u10,以太网变压器t1,晶振y2,电容c113、c114、c115、c120、c122、c121、c123、c124,发光二极管d7和d8,电阻r103、r104、r105、r107、r108、r109、r110、r111、r112、r113、r114、r115;所述以太网phy层芯片u10的引脚1和引脚19相连后分别连接所述以太网变压器t1的引脚2、引脚7以及所述电容c120的一端,所述电容c120的另一端接地,所述以太网phy层芯片u10的引脚6分别连接端子vddc

‑

eth和所述电容c114的一端,所述电容c114的一端还连接所述电容c115的一端,所述

电容c114的另一端和所述电容c115的另一端相连后接地,所述以太网phy层芯片u10的引脚9分别连接端子vcc

‑

eth和所述电容c113的一端,所述电容c113的另一端接地,所述电容c113的一端还连接所述电阻r103的一端,所述以太网phy层芯片u10的引脚12分别连接所述电阻r103的另一端和所述端子mdio,所述以太网phy层芯片u10的引脚13连接所述端子mdc,所述以太网phy层芯片u10的引脚8连接所述电阻r104的一端,所述电阻r104的另一端连接所述端子rxd0,所述以太网phy层芯片u10的引脚7连接所述电阻r105的一端,所述电阻r105的另一端连接所述端子rxd1,所述以太网phy层芯片u10的引脚14连接所述电阻r107的一端,所述电阻r107的另一端连接所述端子refclko,所述以太网phy层芯片u10的引脚10连接所述端子rxer,所述以太网phy层芯片u10的引脚16连接所述端子txen,所述以太网phy层芯片u10的引脚17连接所述电阻r108的一端,所述电阻r108的另一端连接所述端子txd0,所述以太网phy层芯片u10的引脚18连接所述电阻r109的一端,所述电阻r109的另一端连接所述端子txd1,所述以太网phy层芯片u10的引脚11连接所述端子crs

‑

dv,所述以太网phy层芯片u10的引脚15分别连接所述电阻r112的一端和所述电容c124的一端,所述电阻r112的另一端连接所述端子vcc

‑

eth,所述电容c124的另一端接地,所述电阻r112的一端与所述电容c124的一端的连接点连接所述电阻r113的一端,所述电阻r113的另一端连接所述端子lan_reset,所述以太网phy层芯片u10的引脚5分别连接所述晶振y2的引脚1,所述以太网phy层芯片u10的引脚4分别连接所述晶振y2的引脚3和所述电容c123的一端,所述电容c121的另一端与所述电容c123的另一端相连后接地,所述晶振y2的引脚2接地,所述以太网phy层芯片u10的引脚25接地,所述以太网phy层芯片u10的引脚24连接所述电阻r116的一端,所述以太网phy层芯片u10的引脚2分别连接所述电阻r117的一端和所述电阻r115的一端,所述电阻r116的另一端和所述电阻r117的另一端相连后接地,所述电阻r115的另一端连接所述发光二极管d8的正极,所述以太网phy层芯片u10的引脚3连接所述电阻r114的一端,所述电阻r114的另一端连接所述发光二极管d7的正极,所述发光二极管d7的负极和所述发光二极管d8的负极相连后接地,所述以太网phy层芯片u10的引脚21连接所述以太网变压器t1的引脚1,所述以太网phy层芯片u10的引脚20连接所述以太网变压器t1的引脚3,所述以太网phy层芯片u10的引脚23连接所述以太网变压器t1的引脚6,所述以太网phy层芯片u10的引脚22连接所述以太网变压器t1的引脚8,所述以太网变压器t1的引脚16连接数据发送线phy

‑

txp,所述以太网变压器t1的引脚14连接数据发送线phy

‑

txn,所述以太网变压器t1的引脚11连接数据接收线phy

‑

rxp,所述以太网变压器t1的引脚9连接数据接收线phy

‑

rxn,所述以太网变压器t1的引脚15连接所述电阻r111的一端,所述以太网变压器t1的引脚10连接所述电阻r110的一端,所述电阻r110的另一端和所述电阻r111的另一端相连后连接所述电容c122的一端,所述电容c122的另一端接地。

15.进一步地,所述麦克风单元包括语音处理模块u7,读写芯片u8,晶振y1,电容c78、c79、c81、c82、c83、c84、c80、c89、c85、c86、c88、c94、c95、c96、c97、c98、c99、c101、c102、c103、c104、c109、c90、c91、c92、c87、c93、c100,电感器fb4、fb2、fb3、fb5、fb6、fb7、fb8,电阻r51、r53、r54、r56、r58、r62、r63、r57、r59、r60、r61、r67、r72、r73、r76、r78、r89、r66、r69、r74、r79、r90、r91、r92、r93、r94、r95、r52、r55、r64、r65、r70、r71、r75、r77、r82、r83、r84、r85、r86、r87、r80、r364、r81;所述语音处理模块u7的引脚39连接所述电阻r57的一端,所述电阻r57的另一端连接所述电容c89的一端,所述电容c89的另一端分别连接r54的一端

和所述电阻r56的一端,所述语音处理模块u7的引脚40连接所述电阻r59的一端,所述电阻r59的另一端连接所述电容c85的一端,所述电容c85的另一端分别连接所述电阻r63的一端和所述电阻r58的一端,所述语音处理模块u7的引脚41连接所述电阻r60的一端,所述电阻r60的另一端连接所述电容c86的一端,所述电容c86的另一端分别连接所述电阻r53的一端和所述电阻r56的另一端,所述语音处理模块u7的引脚42连接所述电阻r61的一端,所述电阻r61的另一端连接所述电容c88的一端,所述电容c88的另一端分别连接所述电阻r62的一端和所述电阻r58的另一端,所述电阻r62的另一端和所述电阻r63的另一端分别接模拟地,所述电阻r54的另一端与所述电阻r53的另一端相连后接所述电容c80的一端,所述电容c80的另一端接模拟地,所述电容c80的一端还连接所述电阻r51的一端,所述电阻r51的另一端分别连接所述电容c84的一端和所述电感器fb4的一端,所述电容c84的另一端接模拟地,所述电感器fb4的另一端分别连接所述电容c83的一端和所述电容c82的一端,所述电容c82的一端还分别连接所述电容c81的一端和所述语音处理模块u7的引脚19,所述电容c82的一端还连接所述端子dcdc1,所述电容c83的另一端、所述电容c82的另一端以及所述电容c81的另一端分别接模拟地,所述语音处理模块u7的引脚43连接所述电容c94的一端,所述电容c94的另一端连接所述电容c95的一端,所述电容c95的一端还分别连接所述电阻r66的一端和所述电阻r69的一端,所述电阻r66的另一端连接所述电容c96的一端,所述电容c96的另一端、所述电阻r69的另一端以及所述电容c95的另一端相连后接模拟地,所述电阻r66的另一端还分别连接所述电感器fb7的一端和所述电阻r68的一端,所述语音处理模块u7的引脚44连接所述电容c97的一端,所述电容c97的另一端连接所述电容c99的一端,所述电容c99的一端还分别连接所述电阻r74的一端和所述电阻r79的一端,所述电阻r74的另一端连接所述电容c98的一端,所述电容c98的另一端、所述电阻r79的另一端以及所述电容c99的另一端相连后接模拟地,所述电阻r74的另一端还分别连接所述电感器fb8的一端和所述电阻r68的另一端,所述电阻r68的另一端还连接所述电阻r95的一端,所述电感器fb7的另一端分别连接所述电阻r90的一端、所述电阻r91的一端以及所述电阻r92的一端,所述电感器fb8的另一端分别连接所述电阻r92的另一端、所述电阻r93的一端以及所述电阻r94的一端,所述电阻r90的另一端连接所述端子spkp,所述电阻r94的另一端连接所述端子spkn,所述电阻r91的另一端连接所述端子hpoutl,所述电阻r93的另一端和所述电阻r95的另一端相连后接所述端子hpoutr,所述语音处理模块u7的引脚30连接所述电阻r67的一端,所述电阻r67的另一端连接所述电容c81的一端,所述语音处理模块u7的引脚31分别连接所述电阻r89的一端和所述电容c103的一端,所述电阻r89的另一端连接所述电容c82的一端,所述电容c103的另一端接模拟地,所述语音处理模块u7的引脚22连接所述电阻r72的一端,所述语音处理模块u7的引脚21连接所述电阻r73的一端,所述语音处理模块u7的引脚25连接所述电阻r76的一端,所述语音处理模块u7的引脚26连接所述电阻r78的一端,所述电阻r72的另一端、所述电阻r73的另一端、所述电阻r76的另一端以及所述电阻r78的另一端相连后接模拟地,所述语音处理模块u7的引脚27分别连接所述晶振y1的引脚1和所述电容c104的一端,所述语音处理模块u7的引脚28分别连接所述晶振y1的引脚3和所述电容c109的一端,所述电容c104的另一端和所述电容c109的另一端相连后接模拟地,所述语音处理模块u7的引脚37连接所述电容c101的一端,所述语音处理模块u7的引脚45连接所述电容c101的另一端后接模拟地,所述语音处理模块u7的引脚46连接所述电容c102的一端,所述电容c102的另一

端接模拟地,所述语音处理模块u7的引脚7、引脚18以及引脚29相连后接模拟地,所述语音处理模块u7的引脚38接模拟地,所述语音处理模块u7的引脚24分别连接所述电阻r85的一端和所述电阻r87的一端,所述电阻r87的另一端连接所述端子twi1

‑

sda,所述语音处理模块u7的引脚23分别连接所述电阻r84的一端和所述电阻r86的一端,所述电阻r86的另一端连接所述端子twi1

‑

sck,所述语音处理模块u7的引脚12连接所述电阻r75的一端,所述语音处理模块u7的引脚13连接所述电阻r77的一端,所述语音处理模块u7的引脚17连接所述电阻r82的一端,所述语音处理模块u7的引脚20连接所述电阻r83的一端,所述电阻r75的另一端分别连接所述电阻r82的另一端和所述电阻r84的另一端,所述电阻r77的另一端与所述电阻r83的另一端以及所述电阻r85的另一端相连后接模拟地,所述语音处理模块u7的引脚16连接所述读写芯片u8的引脚5,所述语音处理模块u7的引脚15连接所述读写芯片u8的引脚6,所述读写芯片u8的引脚7连接所述电阻r80的一端,所述读写芯片u8的引脚6还连接所述电阻r364的一端,所述读写芯片u8的引脚5还连接所述电阻r81的一端,所述读写芯片u8的引脚8与所述电阻r80的另一端、所述电阻r364的另一端以及所述电阻r81的另一端相连后接所述电容c100的一端,所述电容c100的另一端接地,所述读写芯片u8的引脚1、引脚2、引脚3以及引脚4相连后接地,所述语音处理模块u7的引脚10连接所述电阻r65的一端,所述语音处理模块u7的引脚32连接所述电阻r70的一端,所述语音处理模块u7的引脚14连接所述电阻r71的一端,所述电阻r65的另一端与所述电阻r70的另一端以及所述电阻r71的另一端相连后接模拟地,所述语音处理模块u7的引脚47连接所述电容c90的一端,所述电容c90的另一端连接所述电阻r64的一端,所述电阻r64的另一端连接所述电容c91的一端,所述电容c91的一端分别连接所述输出信号端line_out、所述电感器fb3的一端、所述电感器fb5的一端、所述电感器fb6的一端以及所述电容c92的一端,所述电感器fb3的另一端分别连接所述端子linein_n和所述电阻r52的一端,所述电感器fb5的另一端分别连接所述电阻r52的另一端和所述电阻r55的一端,所述电阻r55的一端还连接所述端子linein_p,所述电感器fb6的另一端分别连接所述电容c87的一端和所述电阻r55的另一端,所述电阻r55的另一端连接端子line_out_p,所述电容c91的另一端与所述电容c92的另一端相连后接模拟地,所述电容c92的另一端还分别连接所述电容c87的一端和所述电容c93的一端,所述电容c93的另一端连接端子line_out_n,所述端子line_out_p和所述端子line_out_n用于将音频信号输出至所述扬声器单元;所述语音处理模块u7的引脚33分别连接所述电容c78的一端和所述电感器fb2的一端,所述电容c78的另一端接地,所述语音处理模块u7的引脚35分别连接所述电感器fb2的另一端和所述电容c79的一端,所述电容c79的另一端接模拟地,所述电容c79的一端还连接电源1.8v。

16.进一步地,所述扬声器单元包括单声道音频功率放大器u6,连接器j5,电感器fb1,双稳压二极管esd12、esd13,电容c62、c63、c68、c69、c70、c67、c66、c64、c65,电阻r39、r40、r41、r43、r44、r42;所述单声道音频功率放大器u6的引脚1分别连接所述端子pa

‑

shdn和所述电阻r39的一端,所述单声道音频功率放大器u6的引脚2分别连接所述电阻r40的一端和所述电容c62的一端,所述单声道音频功率放大器u6的引脚3分别连接所述电阻r40的另一端、所述电容c63的一端以及所述电阻r43的一端,所述电容c63的另一端连接所述电阻r41的一端,所述电阻r39的另一端、所述电容c62的另一端以及所述电阻r41的另一端相连后接地,所述电阻r43的另一端连接所述电容c68的一端,所述电容c68的另一端连接所述端子

spkp,所述单声道音频功率放大器u6的引脚4分别连接所述电阻r42的一端、所述电容c67的一端、以及所述电阻r44的一端,所述电阻r44的另一端分别连接所述电容c69的一端和所述电容c70的一端,所述电容c69的另一端连接所述端子skpn,所述电容c70的另一端连接所述端子line_in,所述单声道音频功率放大器u6的引脚5分别连接所述电阻r42的另一端、所述电容c67的另一端以及所述电容c65的一端,所述电容c65的一端还分别连接所述双稳压二极管esd12的一端和所述连接器j5的引脚2,所述单声道音频功率放大器u6的引脚6分别接所述电容c66的一端和所述电感器fb1的一端,所述电容c66的另一端接地,所述电感器fb1的另一端连接电源5v,所述单声道音频功率放大器u6的引脚7接地,所述单声道音频功率放大器u6的引脚8分别连接所述电容c64的一端、所述双稳压二极管esd13的一端以及所述连接器j5的引脚1,所述电容c66的另一端接地,所述电容c64的另一端和所述电容c65的另一端相连后接地,所述双稳压二极管esd12的另一端和所述双稳压二极管esd13的另一端分别接地,所述连接器j5的引脚4和引脚3相连后接地。

17.进一步地,所述存储单元包括存储卡插槽j4,双稳压二极管esd5、esd6、esd7、esd8、esd9、esd10以及esd11,电容c50,电阻r33、r34、r35;所述存储卡插槽j4为micro sd/tf存储卡插槽;所述存储卡插槽j4的引脚1分别连接所述双稳压二极管esd5的一端和所述端子sdc0

‑

d2,所述存储卡插槽j4的引脚2分别连接所述双稳压二极管esd6的一端和所述端子sdc0

‑

d3,所述存储卡插槽j4的引脚3依次分别连接所述电阻r33的一端、所述双稳压二极管esd7的一端和所述端子sdc0

‑

cmd,所述存储卡插槽j4的引脚4分别连接所述电阻r34的一端和所述电阻r33的另一端,所述电阻r33的另一端还分别连接所述端子dcdc1,所述电容c50的另一端接地,所述存储卡插槽j4的引脚5分别连接所述双稳压二极管esd8的一端和所述电阻r35的一端,所述电阻r35的另一端连接所述端子sdc0

‑

cmd,所述存储卡插槽j4的引脚6接地,所述存储卡插槽j4的引脚7分别连接所述双稳压二极管esd9的一端和所述端子sdc0

‑

d0,所述存储卡插槽j4的引脚8分别连接所述双稳压二极管esd10的一端和所述端子sdc0

‑

d1,所述存储卡插槽j4的引脚9分别连接所述双稳压二极管esd11的一端、所述电阻r34的另一端和所述端子sdc0

‑

det,所述双稳压二极管esd5的另一端、所述双稳压二极管esd6的另一端、所述双稳压二极管esd7的另一端、所述双稳压二极管esd8的另一端、所述双稳压二极管esd9的另一端、所述双稳压二极管esd10的另一端、所述双稳压二极管esd11的另一端相连后接地,所述存储卡插槽j4的引脚13、引脚12、引脚11以及引脚10相连后接地。

18.进一步地,所述单刀双掷模拟开关u15、u16、u17的型号为74lvc1g3157。

19.进一步地,所述以太网phy层芯片u10的型号为lan8720a。

20.进一步地,所述语音处理模块u7的型号为fm1188,所述单声道音频功率放大器u6的型号为lm4890。

21.本发明的有益效果在于,本发明提供的一种同时接入数字和模拟室内机的双模智能对讲系统,包括mcu单元、数模单元、电源单元、网络接口单元、麦克风单元以及扬声器单元,数模单元将接入的数字室内机的数字信号和模拟室内机的模拟信号传送至mcu单元;mcu单元通过处理器内置的数模转换器和乘法器,将接收到的模拟室内机的模拟信号转换为数字信号,与接收到的数字室内机的数字信号进行通话模式切换,通过麦克风单元和扬声器单元实现数字室内机和模拟室内机对讲;本发明兼顾模拟和数字对讲系统的优点,实现可以同时接入模拟和数字室内机01的双模智能对讲系统,以满足不同用户的需求。

附图说明

22.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

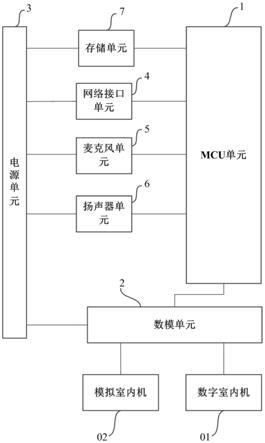

23.图1是本发明实施例提供的一种同时接入数字和模拟室内机的双模智能对讲系统的系统组成框图。

24.图2是本发明实施例提供的一种同时接入数字和模拟室内机的双模智能对讲系统的mcu单元电路原理图。

25.图3是本发明实施例提供的一种同时接入数字和模拟室内机的双模智能对讲系统的数模单元电路原理图。

26.图4是本发明实施例提供的一种同时接入数字和模拟室内机的双模智能对讲系统的电源单元电路原理图。

27.图5是本发明实施例提供的一种同时接入数字和模拟室内机的双模智能对讲系统的网络接口单元电路原理图。

28.图6是本发明实施例提供的一种同时接入数字和模拟室内机的双模智能对讲系统的麦克风单元电路原理图。

29.图7是本发明实施例提供的一种同时接入数字和模拟室内机的双模智能对讲系统的扬声器单元电路原理图。

30.图8是本发明实施例提供的一种同时接入数字和模拟室内机的双模智能对讲系统的存储单元电路原理图。

31.上述图中的标记为1、mcu单元;2、数模单元;3、电源单元;4、网络接口单元;5、麦克风单元;6、扬声器单元;7、存储单元;01、数字室内机;02、模拟室内机。

具体实施方式

32.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

33.本发明的附图中相同或相似的标号对应相同或相似的部件;在本发明的描述中,需要理解的是,若有术语“上”、“下”、“左”、“右”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此附图中描述位置关系的用语仅用于示例性说明,不能理解为对本专利的限制,对于本领域的普通技术人员而言,可以根据具体情况理解上述术语的具体含义。

34.以下结合附图与具体实施例,对本发明的技术方案做详细的说明。

35.如图1至图8所示,为本发明提供的较佳实施例。

36.参照图1,本发明提供的一种同时接入数字和模拟室内机的双模智能对讲系统,包括mcu单元1、数模单元2、电源单元3、网络接口单元4、麦克风单元5以及扬声器单元6;mcu单元1分别与数模单元2、电源单元3、网络接口单元4、麦克风单元5以及扬声器单元6电性相

连,电源单元3还分别与数模单元2、网络接口单元4、麦克风单元5以及扬声器单元6电性相连,数模单元2还分别接入数字室内机01和模拟室内机02;

37.电源单元3用于为mcu单元1、数模单元2、网络接口单元4、麦克风单元5以及扬声器单元6提供工作电源,网络接口单元4用于mcu单元1通过以太网与外部设备进行数据交换,存储单元7用于存储mcu单元1的处理数据;

38.数模单元2用于将接入的数字室内机01的数字信号和模拟室内机02的模拟信号传送至mcu单元1;mcu单元1通过处理器内置的数模转换器和乘法器,将接收到的模拟室内机02的模拟信号转换为数字信号,与接收到的数字室内机01的数字信号进行通话模式切换,通过麦克风单元5和扬声器单元6实现数字室内机01和模拟室内机02对讲;

39.参照图2,mcu单元1包括处理器u5,电容c51、c52、c53,电阻r19、r20、r22、r23、r24、r25、r26、r27、r31、r32;处理器u5的型号为a64youpiao;处理器u5的引脚2连接电阻r31的一端,电阻r31的另一端分别连接端子pa

‑

shdn和电阻r32的一端,端子pa

‑

shdn用于功放控制,电阻r32的另一端连接端子out_mcu_pa

‑

shdn,处理器u5的引脚16连接模拟地,处理器u5的引脚48、引脚44、引脚41、引脚38、引脚35以及引脚32相连后接地,处理器u5的引脚58、引脚59以及引脚60相连后接电源5v,处理器u5的引脚61和引脚62相连后接地,处理器u5的引脚63分别连接电容c53的一端和端子,电容c53的另一端接地,处理器u5的引脚76分别连接电容c51的一端和电容c52的一端,电容c51的另一端和电容c52的另一端相连后接地,处理器u5的引脚92和引脚93相连后接地,处理器u5的引脚94接电源1.8v,处理器u5的引脚95和引脚96相连后接端子,处理器u5的引脚97连接电阻r22的一端,电阻r22的另一端分别接io口gpio4和电阻r26的一端,电阻r26的另一端接端子out_mcu_gp4,处理器u5的引脚98连接电阻r23的一端,电阻r23的另一端分别接io口gpio5和电阻r27的一端,电阻r27的另一端接端子out_mcu_gp5,处理器u5的引脚100连接电阻r20的一端,电阻r20的另一端分别接io口gpio3和电阻r25的一端,电阻r25的另一端接端子out_mcu_gp3,处理器u5的引脚102连接电阻r19的一端,电阻r19的另一端分别接io口gpio2和电阻r24的一端,电阻r24的另一端接端子out_mcu_gp2;

40.处理器u5的引脚119连接端子uart3

‑

tx,用于串口数据发送;处理器u5的引脚118连接端子uart3

‑

rx,用于串口数据接收;处理器u5的引脚77连接端子bt

‑

uart

‑

rx,用于蓝牙串口数据接收;处理器u5的引脚67连接端子bt

‑

uart

‑

tx,用于蓝牙串口数据发送;处理器u5的引脚57连接端子mdio,为以太网管理接口;处理器u5的引脚56连接端子mdc,为以太网数据传输接口;处理器u5的引脚52连接端子rxd0,为数据接收信号线;处理器u5的引脚53连接端子rxd1,为数据接收信号线;处理器u5的引脚54连接端子refclko,为以太网时钟信号线;处理器u5的引脚50连接端子rxer,为接收数据错误提示信号线;处理器u5的引脚55连接端子txen,为数据传输使能信号线;处理器u5的引脚48连接端子txd0,为数据发送信号线;处理器u5的引脚49连接端子txd1,为数据发送信号线;处理器u5的引脚51连接端子crs

‑

dv,为以太网控制信号接口;处理器u5的引脚1连接端子lan_reset,用于连接以太网复位按钮;处理器u5的引脚96和引脚95相连后接端子dcdc1,用于传输dc信号;处理器u5的引脚24连接端子spkp,为音频正差分输出端;处理器u5的引脚25连接端子spkn,为音频负差分输出端;处理器u5的引脚19连接端子hpoutr,为右耳机接口;处理器u5的引脚20连接端子hpoutl,为左耳机接口;处理器u5的引脚7连接端子twi1

‑

sda,为twi接口的串行数据线;处理器u5的引脚

8连接端子twi1

‑

sck,为twi接口的同步时钟线;处理器u5的引脚22连接端子linein_p,用于连接声卡插口;处理器u5的引脚23连接端子linein_n,用于连接声卡插口;处理器u5的引脚112、引脚111、引脚109以及引脚107分别连接端子sdc0

‑

d0、端子sdc0

‑

d1、端子sdc0

‑

d2以及端子sdc0

‑

d3,用于存储卡的数据读写;处理器u5的引脚113连接端子sdc0

‑

clk,用于存储卡的时钟控制;处理器u5的引脚110连接端子sdc0

‑

cmd,用于存储卡的读写控制;处理器u5的引脚108连接端子sdc0

‑

det,用于存储卡的检测;

41.参照图3,数模单元2包括单刀双掷模拟开关u15、u16、u17,数字信号接入器j1208,数字信号传输器j11,电容c141、c143、c142、c144、c145、c146、c319、c149、c150、c151、c152、c318,电阻r159、r160、r161、r369、r370、r164、r367、r368、r165、r166、r168、r170、r337、r336、r167、r169、r171;数模单元2包括单刀双掷模拟开关u15、u16、u17用于将模拟室内机02的模拟信号传送至mcu单元1,数字信号接入器j1208和数字信号传输器j11用于将数字室内机01的数字信号传送至mcu单元1;

42.单刀双掷模拟开关u15的引脚1接输出信号端line_out,单刀双掷模拟开关u15的引脚2接地,单刀双掷模拟开关u15的引脚3接输出信号端line_in_t,单刀双掷模拟开关u15的引脚4分别连接电容c141的一端和电阻r159的一端,电容c141的另一端和电阻r159的另一端相连后接地,单刀双掷模拟开关u15的引脚5分别连接电容c143的一端和电源3.3v,电容c143的另一端接地,单刀双掷模拟开关u15的引脚6连接io口gpio2;单刀双掷模拟开关u16的引脚1接输出信号端line_in_l,单刀双掷模拟开关u16的引脚2接地,单刀双掷模拟开关u16的引脚3接输出信号端mic_out,单刀双掷模拟开关u16的引脚4分别连接电容c144的一端和电阻r160的一端,电容c144的另一端和电阻r160的另一端相连后接地,单刀双掷模拟开关u16的引脚5分别连接电容c142的一端和电源3.3v,电容c142的另一端接地,单刀双掷模拟开关u16的引脚6连接io口gpio3;单刀双掷模拟开关u17的引脚1接输出信号端line_out,单刀双掷模拟开关u17的引脚2接地,单刀双掷模拟开关u17的引脚3接输出信号端mic_out_t,单刀双掷模拟开关u17的引脚4分别连接电容c146的一端和电阻r161的一端,电容c146的另一端和电阻r161的另一端相连后接地,单刀双掷模拟开关u17的引脚5分别连接电容c145的一端和电源3.3v,电容c145的另一端接地,单刀双掷模拟开关u17的引脚6连接io口gpio4;

43.数字信号接入器j1208的引脚1接端子mic_in,数字信号接入器j1208的引脚13和引脚2相连后接模拟地,数字信号接入器j1208的引脚5接地,数字信号接入器j1208的引脚6接电源5.2v,数字信号接入器j1208的引脚9连接电容c319的一端,电容c319的另一端接地,数字信号接入器j1208的引脚10连接电阻r370的一端,电阻r370的另一端连接数字信号传输器j11的引脚10,数字信号接入器j1208的引脚14连接电阻r369的一端,电阻r369的另一端连接数字信号传输器j11的引脚8,数字信号传输器j11的引脚1分别连接电容c150的一端和电阻r164的一端,电容c150的另一端接地,电容c150的一端还连接电容c149的一端,电容c149的另一端接地,电阻r164的另一端接电源12v,数字信号传输器j11的引脚2分别连接电阻r336的一端、电阻r165的一端以及电阻r166的一端,数字信号传输器j11的引脚3分别连接电阻r337的一端、电阻r168的一端以及电阻r170的一端,电阻r337的另一端与电阻r336的另一端相连后接地,电阻r165的另一端连接端子uart3

‑

tx,电阻r166的另一端连接端子bt

‑

uart

‑

rx,电阻r168的另一端连接端子bt

‑

uart

‑

tx,电阻r170的另一端连接端子uart3

‑

rx,数字信号传输器j11的引脚4分别连接电阻r169的一端、电阻r167的一端以及电容c151的一端,电阻r167的一端还连接电阻r171的一端,电阻r171的另一端与电容c151的另一端相连后接地,电阻r169的另一端连接io口gpio5,电阻r167的另一端连接端子out_ad_rst,数字信号传输器j11的引脚6连接端子cvbsout,数字信号传输器j11的引脚5、引脚7、引脚9、引脚11以及引脚12相连后接地,数字信号传输器j11的引脚8还分别连接电容c318的一端和电阻r367的一端,电容c318的另一端接地,电阻r367的另一端接端子spk_out,数字信号传输器j11的引脚10还分别连接电容c152的一端和电阻r368的一端,电容c152的另一端接地,电阻r368的另一端连接端子mic_in。

44.上述技术方案提供的一种同时接入数字和模拟室内机的双模智能对讲系统,包括mcu单元1、数模单元2、电源单元3、网络接口单元4、麦克风单元5以及扬声器单元6,数模单元2将接入的数字室内机01的数字信号和模拟室内机02的模拟信号传送至mcu单元1;mcu单元1通过处理器内置的数模转换器和乘法器,将接收到的模拟室内机02的模拟信号转换为数字信号,与接收到的数字室内机01的数字信号进行通话模式切换,通过麦克风单元5和扬声器单元6实现数字室内机01和模拟室内机02对讲;本发明兼顾模拟和数字对讲系统的优点,实现可以同时接入模拟和数字室内机01的双模智能对讲系统,以满足不同用户的需求。

45.作为本发明的一种实施方式,参照图4,电源单元3包括单片同步整流降压稳压器u1和u2,正向低压降稳压器u3,插座j1,整流器f1,共模电感l1,电感器l2和l3,mos管q1和q2,三极管q3和q4,极性电容c9、c11、c13、c33,发光二极管d5,二极管d1、d2、d3、d4、d6,电容c1、c2、c3、c4、c5、c6、c7、c10、c8、c12、c22、c23、c24、c14、c16、c15、c17、c18、c19、c20、c21、c39、c40、c41、c25、c27、c26、c28、c29、c30、c31、c32、c34、c35、c36、c37、c38,电阻r1、r7、r8、r4、r3、r5、r2、r6、r10、r12、r11、r13、r14、r17、r15、r18、r16;插座j1的引脚1和引脚4相连后接端子,插座j1的引脚2和引脚相连后分别接端子、输入电源12v、电容c2的一端,电容c2的一端还分别连接电容c3的一端和整流器f1的引脚1,插座的引脚4还分别连接电容c2的另一端和电容c3的另一端,整流器f1的引脚2分别连接电容c4的一端和电容c5的一端,电容c5的一端还连接共模电感l1的引脚1,电容c3的另一端还分别连接电容c4的另一端和电容c5的另一端,电容c5的另一端还连接共模电感的引脚2,共模电感的引脚3分别连接电容c6的一端和电容c7的一端,共模电感l1的引脚4连接电容c6的另一端,电容c7的另一端与电容c6的另一端相连后接地,电容c7的一端还连接二极管d1的正极,二极管d1的负极分别连接极性电容c9的正极和电容c10的一端,极性电容c9的负极接地,电容c10的另一端接地,电容c10的一端还分别连接极性电容c11的正极和电阻r1的一端,极性电容c11的负极接地,电阻r1的一端还分别连接mos管q1的漏极、mos管q2的漏极、电阻r3的一端、电容c8的一端以及电阻r4的一端,电阻r1的另一端连接二极管d3的负极,二极管d3的正极分别连接电阻r8的一端和电阻r7的一端,电阻r7的另一端接地,电阻r8的另一端连接三极管q4的基极,三极管q4的发射极接地,三极管q4的集电极分别连接电阻r4的另一端和三极管q3的基极,三极管q3的发射极接地,三极管q3的集电极连接电阻r5的一端,电容c8的另一端和电阻r3的另一端相连后接mos管q2的栅极,电容c8的另一端和电阻r3的另一端相连的连接点与电阻r5的另一端相连后接mos管q1的栅极,mos管q1的源极分别连接电容c1的一端、单片同步整流降压稳压器的引脚2以及电容c22的一端,电容c1的另一端和电容c22的另一端分别接地,mos管q2的源极分别连接电源12v和电容c12的一端,电容c12的另一端接地,电容c12的一端还分别

连接极性电容c13的正极和电阻r2的一端,极性电容c13的负极接地,电阻r2的另一端分别连接二极管d2的正极和电阻r6的一端,电阻r6的另一端接地,二极管d2的负极分别连接正向低压降稳压器u3的引脚2和电容c37的一端,电容c37的一端还连接电容c38的一端,电容c37的另一端和电容c38的另一端相连后接地,正向低压降稳压器u3的引脚2还与引脚4相连后接电容c36的一端,电容c36的另一端接地,正向低压降稳压器u3的引脚3分别连接电容c35的一端和电容c34的一端,电容c34的一端还连接电容c32的一端,电容c34的另一端和电容c35的另一端分别接地,单片同步整流降压稳压器u2的引脚1连接电容c25的一端,单片同步整流降压稳压器u2的引脚3分别连接电容c25的另一端和二极管d6的正极,二极管d6的负极接地,单片同步整流降压稳压器u2的引脚3分别连接电容c25的另一端相连后连接电感器l3的一端,电感器l3的另一端与电阻r15的一端、电容c26的一端、电容c28的一端、电容c29的一端、电容c30的一端、电容c31的一端、电容c32的一端、电阻r16的一端以及极性电容c33的正极相连,单片同步整流降压稳压器u2的引脚5与电阻r15的另一端和电容c26的另一端相连后接电阻r18的一端,电阻r18的另一端接地,电容r28的另一端和电容r29的另一端相连后接地,电容c30的另一端、电容c31的另一端、电容c32的另一端、发光二极管d5的负极、极性电容c33的负极分别接地,电阻r16的另一端连接发光二极管d5的正极,单片同步整流降压稳压器u2的引脚6连接电容c27的一端,电容c27的另一端连接电阻r17的一端,电阻r17的另一端接地,单片同步整流降压稳压器u2的引脚4和引脚9分别接地,单片同步整流降压稳压器u2的引脚8连接电容c41的一端,电容c41的另一端接地,单片同步整流降压稳压器u2的引脚7连接电阻r14的一端,电阻r14的另一端分别连接单片同步整流降压稳压器u2的引脚2和电容c40的一端,电容c40的另一端接地,电阻r14的另一端还分别连接电源12v和电容c39的一端,电容c39的另一端接地,单片同步整流降压稳压器u1的引脚2分别连接电阻r10的一端和电容c22的一端,单片同步整流降压稳压器u1的引脚7连接电阻r10的另一端,电阻r10的一端还连接电容c23的一端,电容c23的另一端接地,单片同步整流降压稳压器u1的引脚8连接电容c24的一端,电容c24的另一端接地,单片同步整流降压稳压器u1的引脚6连接电容c16的一端,电容c16的另一端连接电阻r12的一端,电阻r12的另一端接地,单片同步整流降压稳压器u1的引脚1连接电容c14的一端,电容c14的另一端与单片同步整流降压稳压器u1的引脚3相连后连接电感器l2的一端,单片同步整流降压稳压器u1的引脚3还连接二极管d4的负极,二极管d4的正极接地,电感器l2的另一端与电阻r11的一端、电容c15的一端、电容c17的一端、电容c18的一端、电容c19的一端、电容c20的一端以及电容c21的一端相连,单片同步整流降压稳压器u1的引脚5分别连接电阻r11的另一端、电容c15的另一端、电阻r13的一端,电阻r13的另一端接地,电容c17的另一端和电容c18的另一端相连后接地,电容c19的另一端、电容c20的另一端、电容c21的另一端分别接地,电容c21的一端还接电源5.1v。

46.具体地,单片同步整流降压稳压器u1和u2的型号为gs2953,正向低压降稳压器u3的型号为ams1117

‑

3v3。

47.作为本发明的一种实施方式,参照图5,网络接口单元4包括以太网phy层芯片u10,以太网变压器t1,晶振y2,电容c113、c114、c115、c120、c122、c121、c123、c124,发光二极管d7和d8,电阻r103、r104、r105、r107、r108、r109、r110、r111、r112、r113、r114、r115;以太网phy层芯片u10的引脚1和引脚19相连后分别连接以太网变压器t1的引脚2、引脚7以及电容

c120的一端,电容c120的另一端接地,以太网phy层芯片u10的引脚6分别连接端子vddc

‑

eth和电容c114的一端,电容c114的一端还连接电容c115的一端,电容c114的另一端和电容c115的另一端相连后接地,以太网phy层芯片u10的引脚9分别连接端子vcc

‑

eth和电容c113的一端,电容c113的另一端接地,电容c113的一端还连接电阻r103的一端,以太网phy层芯片u10的引脚12分别连接电阻r103的另一端和端子mdio,以太网phy层芯片u10的引脚13连接端子mdc,以太网phy层芯片u10的引脚8连接电阻r104的一端,电阻r104的另一端连接端子rxd0,以太网phy层芯片u10的引脚7连接电阻r105的一端,电阻r105的另一端连接端子rxd1,以太网phy层芯片u10的引脚14连接电阻r107的一端,电阻r107的另一端连接端子refclko,以太网phy层芯片u10的引脚10连接端子rxer,以太网phy层芯片u10的引脚16连接端子txen,以太网phy层芯片u10的引脚17连接电阻r108的一端,电阻r108的另一端连接端子txd0,以太网phy层芯片u10的引脚18连接电阻r109的一端,电阻r109的另一端连接端子txd1,以太网phy层芯片u10的引脚11连接端子crs

‑

dv,以太网phy层芯片u10的引脚15分别连接电阻r112的一端和电容c124的一端,电阻r112的另一端连接端子vcc

‑

eth,电容c124的另一端接地,电阻r112的一端与电容c124的一端的连接点连接电阻r113的一端,电阻r113的另一端连接端子lan_reset,以太网phy层芯片u10的引脚5分别连接晶振y2的引脚1,以太网phy层芯片u10的引脚4分别连接晶振y2的引脚3和电容c123的一端,电容c121的另一端与电容c123的另一端相连后接地,晶振y2的引脚2接地,以太网phy层芯片u10的引脚25接地,以太网phy层芯片u10的引脚24连接电阻r116的一端,以太网phy层芯片u10的引脚2分别连接电阻r117的一端和电阻r115的一端,电阻r116的另一端和电阻r117的另一端相连后接地,电阻r115的另一端连接发光二极管d8的正极,以太网phy层芯片u10的引脚3连接电阻r114的一端,电阻r114的另一端连接发光二极管d7的正极,发光二极管d7的负极和发光二极管d8的负极相连后接地,以太网phy层芯片u10的引脚21连接以太网变压器t1的引脚1,以太网phy层芯片u10的引脚20连接以太网变压器t1的引脚3,以太网phy层芯片u10的引脚23连接以太网变压器t1的引脚6,以太网phy层芯片u10的引脚22连接以太网变压器t1的引脚8,以太网变压器t1的引脚16连接数据发送线phy

‑

txp,以太网变压器t1的引脚14连接数据发送线phy

‑

txn,以太网变压器t1的引脚11连接数据接收线phy

‑

rxp,以太网变压器t1的引脚9连接数据接收线phy

‑

rxn,以太网变压器t1的引脚15连接电阻r111的一端,以太网变压器t1的引脚10连接电阻r110的一端,电阻r110的另一端和电阻r111的另一端相连后连接电容c122的一端,电容c122的另一端接地。

48.具体地,以太网phy层芯片u10的型号为lan8720a。

49.作为本发明的一种实施方式,参照图6,麦克风单元5包括语音处理模块u7,读写芯片u8,晶振y1,电容c78、c79、c81、c82、c83、c84、c80、c89、c85、c86、c88、c94、c95、c96、c97、c98、c99、c101、c102、c103、c104、c109、c90、c91、c92、c87、c93、c100,电感器fb4、fb2、fb3、fb5、fb6、fb7、fb8,电阻r51、r53、r54、r56、r58、r62、r63、r57、r59、r60、r61、r67、r72、r73、r76、r78、r89、r66、r69、r74、r79、r90、r91、r92、r93、r94、r95、r52、r55、r64、r65、r70、r71、r75、r77、r82、r83、r84、r85、r86、r87、r80、r364、r81;语音处理模块u7的引脚39连接电阻r57的一端,电阻r57的另一端连接电容c89的一端,电容c89的另一端分别连接r54的一端和电阻r56的一端,语音处理模块u7的引脚40连接电阻r59的一端,电阻r59的另一端连接电容c85的一端,电容c85的另一端分别连接电阻r63的一端和电阻r58的一端,语音处理模块u7

的引脚41连接电阻r60的一端,电阻r60的另一端连接电容c86的一端,电容c86的另一端分别连接电阻r53的一端和电阻r56的另一端,语音处理模块u7的引脚42连接电阻r61的一端,电阻r61的另一端连接电容c88的一端,电容c88的另一端分别连接电阻r62的一端和电阻r58的另一端,电阻r62的另一端和电阻r63的另一端分别接模拟地,电阻r54的另一端与电阻r53的另一端相连后接电容c80的一端,电容c80的另一端接模拟地,电容c80的一端还连接电阻r51的一端,电阻r51的另一端分别连接电容c84的一端和电感器fb4的一端,电容c84的另一端接模拟地,电感器fb4的另一端分别连接电容c83的一端和电容c82的一端,电容c82的一端还分别连接电容c81的一端和语音处理模块u7的引脚19,电容c82的一端还连接端子dcdc1,电容c83的另一端、电容c82的另一端以及电容c81的另一端分别接模拟地,语音处理模块u7的引脚43连接电容c94的一端,电容c94的另一端连接电容c95的一端,电容c95的一端还分别连接电阻r66的一端和电阻r69的一端,电阻r66的另一端连接电容c96的一端,电容c96的另一端、电阻r69的另一端以及电容c95的另一端相连后接模拟地,电阻r66的另一端还分别连接电感器fb7的一端和电阻r68的一端,语音处理模块u7的引脚44连接电容c97的一端,电容c97的另一端连接电容c99的一端,电容c99的一端还分别连接电阻r74的一端和电阻r79的一端,电阻r74的另一端连接电容c98的一端,电容c98的另一端、电阻r79的另一端以及电容c99的另一端相连后接模拟地,电阻r74的另一端还分别连接电感器fb8的一端和电阻r68的另一端,电阻r68的另一端还连接电阻r95的一端,电感器fb7的另一端分别连接电阻r90的一端、电阻r91的一端以及电阻r92的一端,电感器fb8的另一端分别连接电阻r92的另一端、电阻r93的一端以及电阻r94的一端,电阻r90的另一端连接端子spkp,电阻r94的另一端连接端子spkn,电阻r91的另一端连接端子hpoutl,电阻r93的另一端和电阻r95的另一端相连后接端子hpoutr,语音处理模块u7的引脚30连接电阻r67的一端,电阻r67的另一端连接电容c81的一端,语音处理模块u7的引脚31分别连接电阻r89的一端和电容c103的一端,电阻r89的另一端连接电容c82的一端,电容c103的另一端接模拟地,语音处理模块u7的引脚22连接电阻r72的一端,语音处理模块u7的引脚21连接电阻r73的一端,语音处理模块u7的引脚25连接电阻r76的一端,语音处理模块u7的引脚26连接电阻r78的一端,电阻r72的另一端、电阻r73的另一端、电阻r76的另一端以及电阻r78的另一端相连后接模拟地,语音处理模块u7的引脚27分别连接晶振y1的引脚1和电容c104的一端,语音处理模块u7的引脚28分别连接晶振y1的引脚3和电容c109的一端,电容c104的另一端和电容c109的另一端相连后接模拟地,语音处理模块u7的引脚37连接电容c101的一端,语音处理模块u7的引脚45连接电容c101的另一端后接模拟地,语音处理模块u7的引脚46连接电容c102的一端,电容c102的另一端接模拟地,语音处理模块u7的引脚7、引脚18以及引脚29相连后接模拟地,语音处理模块u7的引脚38接模拟地,语音处理模块u7的引脚24分别连接电阻r85的一端和电阻r87的一端,电阻r87的另一端连接端子twi1

‑

sda,语音处理模块u7的引脚23分别连接电阻r84的一端和电阻r86的一端,电阻r86的另一端连接端子twi1

‑

sck,语音处理模块u7的引脚12连接电阻r75的一端,语音处理模块u7的引脚13连接电阻r77的一端,语音处理模块u7的引脚17连接电阻r82的一端,语音处理模块u7的引脚20连接电阻r83的一端,电阻r75的另一端分别连接电阻r82的另一端和电阻r84的另一端,电阻r77的另一端与电阻r83的另一端以及电阻r85的另一端相连后接模拟地,语音处理模块u7的引脚16连接读写芯片u8的引脚5,语音处理模块u7的引脚15连接读写芯片u8的引脚6,读写芯片u8的引脚7连接电

阻r80的一端,读写芯片u8的引脚6还连接电阻r364的一端,读写芯片u8的引脚5还连接电阻r81的一端,读写芯片u8的引脚8与电阻r80的另一端、电阻r364的另一端以及电阻r81的另一端相连后接电容c100的一端,电容c100的另一端接地,读写芯片u8的引脚1、引脚2、引脚3以及引脚4相连后接地,语音处理模块u7的引脚10连接电阻r65的一端,语音处理模块u7的引脚32连接电阻r70的一端,语音处理模块u7的引脚14连接电阻r71的一端,电阻r65的另一端与电阻r70的另一端以及电阻r71的另一端相连后接模拟地,语音处理模块u7的引脚47连接电容c90的一端,电容c90的另一端连接电阻r64的一端,电阻r64的另一端连接电容c91的一端,电容c91的一端分别连接输出信号端line_out、电感器fb3的一端、电感器fb5的一端、电感器fb6的一端以及电容c92的一端,电感器fb3的另一端分别连接端子linein_n和电阻r52的一端,电感器fb5的另一端分别连接电阻r52的另一端和电阻r55的一端,电阻r55的一端还连接端子linein_p,电感器fb6的另一端分别连接电容c87的一端和电阻r55的另一端,电阻r55的另一端连接端子line_out_p,电容c91的另一端与电容c92的另一端相连后接模拟地,电容c92的另一端还分别连接电容c87的一端和电容c93的一端,电容c93的另一端连接端子line_out_n,端子line_out_p和端子line_out_n用于将音频信号输出至扬声器单元6;语音处理模块u7的引脚33分别连接电容c78的一端和电感器fb2的一端,电容c78的另一端接地,语音处理模块u7的引脚35分别连接电感器fb2的另一端和电容c79的一端,电容c79的另一端接模拟地,电容c79的一端还连接电源1.8v。

50.作为本发明的一种实施方式,参照图7,扬声器单元6包括单声道音频功率放大器u6,连接器j5,电感器fb1,双稳压二极管esd12、esd13,电容c62、c63、c68、c69、c70、c67、c66、c64、c65,电阻r39、r40、r41、r43、r44、r42;单声道音频功率放大器u6的引脚1分别连接端子pa

‑

shdn和电阻r39的一端,单声道音频功率放大器u6的引脚2分别连接电阻r40的一端和电容c62的一端,单声道音频功率放大器u6的引脚3分别连接电阻r40的另一端、电容c63的一端以及电阻r43的一端,电容c63的另一端连接电阻r41的一端,电阻r39的另一端、电容c62的另一端以及电阻r41的另一端相连后接地,电阻r43的另一端连接电容c68的一端,电容c68的另一端连接端子spkp,单声道音频功率放大器u6的引脚4分别连接电阻r42的一端、电容c67的一端、以及电阻r44的一端,电阻r44的另一端分别连接电容c69的一端和电容c70的一端,电容c69的另一端连接端子skpn,电容c70的另一端连接端子line_in,单声道音频功率放大器u6的引脚5分别连接电阻r42的另一端、电容c67的另一端以及电容c65的一端,电容c65的一端还分别连接双稳压二极管esd12的一端和连接器j5的引脚2,单声道音频功率放大器u6的引脚6分别接电容c66的一端和电感器fb1的一端,电容c66的另一端接地,电感器fb1的另一端连接电源5v,单声道音频功率放大器u6的引脚7接地,单声道音频功率放大器u6的引脚8分别连接电容c64的一端、双稳压二极管esd13的一端以及连接器j5的引脚1,电容c66的另一端接地,电容c64的另一端和电容c65的另一端相连后接地,双稳压二极管esd12的另一端和双稳压二极管esd13的另一端分别接地,连接器j5的引脚4和引脚3相连后接地。

51.作为本发明的一种实施方式,参照图8,存储单元7包括存储卡插槽j4,双稳压二极管esd5、esd6、esd7、esd8、esd9、esd10以及esd11,电容c50,电阻r33、r34、r35;存储卡插槽j4为micro sd/tf存储卡插槽;存储卡插槽j4的引脚1分别连接双稳压二极管esd5的一端和端子sdc0

‑

d2,存储卡插槽j4的引脚2分别连接双稳压二极管esd6的一端和端子sdc0

‑

d3,存

储卡插槽j4的引脚3依次分别连接电阻r33的一端、双稳压二极管esd7的一端和端子sdc0

‑

cmd,存储卡插槽j4的引脚4分别连接电阻r34的一端和电阻r33的另一端,电阻r33的另一端还分别连接端子dcdc1,电容c50的另一端接地,存储卡插槽j4的引脚5分别连接双稳压二极管esd8的一端和电阻r35的一端,电阻r35的另一端连接端子sdc0

‑

cmd,存储卡插槽j4的引脚6接地,存储卡插槽j4的引脚7分别连接双稳压二极管esd9的一端和端子sdc0

‑

d0,存储卡插槽j4的引脚8分别连接双稳压二极管esd10的一端和端子sdc0

‑

d1,存储卡插槽j4的引脚9分别连接双稳压二极管esd11的一端、电阻r34的另一端和端子sdc0

‑

det,双稳压二极管esd5的另一端、双稳压二极管esd6的另一端、双稳压二极管esd7的另一端、双稳压二极管esd8的另一端、双稳压二极管esd9的另一端、双稳压二极管esd10的另一端、双稳压二极管esd11的另一端相连后接地,存储卡插槽j4的引脚13、引脚12、引脚11以及引脚10相连后接地。

52.优选地,单刀双掷模拟开关u15、u16、u17的型号为74lvc1g3157。

53.优选地,语音处理模块u7的型号为fm1188,单声道音频功率放大器u6的型号为lm4890。

54.具体地,通话模式切换通过设置io口gpio2、gpio3、gpio4、gpio5高低电平实现,例如,io口gpio2为高电平时,数字室内机01和模拟室内机02处于通话状态;io口gpio3为低电平时,数字室内机01和模拟室内机02处于非通话状态;io口gpio4为低电平时,数字室内机01和模拟室内机02处于非通话状态,io口gpio4为高电平时,数字室内机01和模拟室内机02处于通话状态,io口gpio5为高电平时,数字室内机01和模拟室内机02处于通话状态。

55.以上对本发明的实施例进行了详细的说明,但本发明的创造并不限于本发明,熟悉本领域的技术人员在不违背本发明精神的前提下,还可以做出许多同等变型或替换,这些同等变型或替换均包含在本申请的权利要求所限定的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1