时延积分传感器的制作方法

1.本发明是有关一种时延积分传感器,特别有关一种采用空间补偿实现使用滚动快门的时延积分互补式金属氧化物半导体图像传感器。

背景技术:

2.时延积分(time delay integration,tdi)传感器使用面积阵列图像传感器从影像平台获取影像,该影像平台相对被取像物体或场景以等速度移动。时延积分传感器在概念上可视为线性阵列的堆栈,其中每一线性阵列在传感器移动一列像素距离所需要的时间越过相同的场景点。

3.传统上,只有电荷耦合装置(charge coupled device,ccd)技术适用于时延积分应用,因为电荷耦合装置本质上就是通过将电荷在像素间传递的方式来运作,而当传感器越过取像场景的场景点时使得像素之间的电荷累积。然而,电荷耦合装置的影像装置成本较高且耗费较高电能。

4.使用互补式金属氧化物半导体(complementary metal

‑

oxide

‑

semiconductor,cmos)电路虽然可实现低功率、高累积度及高速的目的,但却具有较高的噪声。虽然使用4

‑

晶体管(4t)像素架构可以降低噪声,但4t像素采用滚动式快门(rolling shutter)技术。使用滚动式快门频率会在所获取的影像中产生假影,这是由于所有的像素并非在相同时间中累积电荷。

5.因此,美国专利号us 9148601中公开了一种用于时延积分取像的cmos图像传感器。请参照图1所示,该cmos图像传感器包含多个像素列(pixel column)112,每一像素列112配置成与沿轨方向(along

‑

track direction)d

a_t

平行。为了补偿cmos图像传感器的滚动快门的积分期间,每一像素列112的两个相邻像素之间另配置有一物理距离150,其中,若假设所述像素列112具有n行,每一个物理距离150则等于一像素高度的1/n。

6.本发明则提供其他的采用空间补偿来实现使用滚动快门的时延积分cmos图像传感器。

技术实现要素:

7.本发明的目的在于提供一种根据像素高度及滚动快门的行时间差与图框(frame)期间决定像素间的分隔距离的tdi cmos图像传感器。

8.本发明还提供一种可在固定的分隔距离下对应不同条件改变所述列时间差的tdi cmos影像传感器。

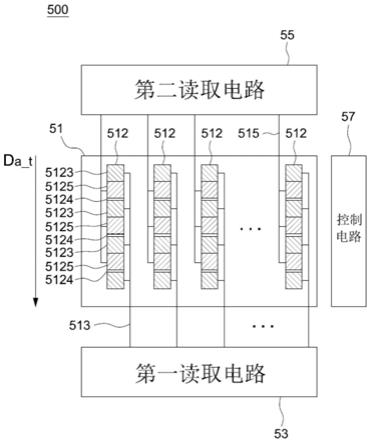

9.为达上述目的,本发明提供一种时延积分互补式金属氧化物半导体图像传感器,其使用滚动快门获取影像图框并用于相对场景朝向沿轨方向移动。所述图像传感器包含像素阵列,该像素阵列包含多个像素列,每一所述像素列包含多个像素配置于所述沿轨方向,且每一所述像素列的两相邻像素之间具有分隔距离,其中该分隔距离等于一个像素在所述沿轨方向的像素高度乘上所述滚动快门的行时间差与获取所述影像图框的图框期间的时

间比例。

10.除此之外,本发明还提供一种时延积分互补式金属氧化物半导体图像传感器,使用滚动快门获取影像图框并用于相对场景朝向沿轨方向移动。所述图像传感器包含像素阵列,该像素阵列包含多个像素列,每一所述像素列包含多个像素配置于所述沿轨方向,且每一所述像素列的两相邻像素之间具有分隔距离,其中该分隔距离等于一个像素在所述沿轨方向的像素高度加上该像素高度乘上所述滚动快门的行时间差与获取所述影像图框的图框期间的时间比例。

11.本发明还提供一种时延积分互补式金属氧化物半导体图像传感器,使用滚动快门获取影像图框并用于相对场景朝向沿轨方向移动。所述图像传感器包含像素阵列,该像素阵列包含多个像素列,每一所述像素列包含多个像素配置于所述沿轨方向,且所述像素的两相邻像素组之间具有分隔距离以补偿使用所述滚动快门时的行时间差,其中每一所述像素组包含第一像素及第二像素。

12.本发明还提供一种时延积分互补式金属氧化物半导体图像传感器,其使用滚动快门获取影像图框并用于相对场景朝向沿轨方向移动。所述图像传感器包含像素阵列以及多个积分器。该像素阵列包含多个像素列,每一所述像素列包含多个像素配置于所述沿轨方向,且每一所述像素列的两相邻像素之间具有分隔距离,其中该分隔距离等于一个像素在所述沿轨方向的像素高度乘上所述滚动快门的行时间差与获取所述影像图框的图框期间的时间比例。所述积分器用于在连续影像图框中,分别储存相对所述场景的相同位置的像素数据,其中,在一倍所述列时间差下,所述积分器的每一者用于在相邻的影像图框累积相对所述场景的所述相同位置的所述像素数据;及在两倍所述行时间差下,所述积分器的每一者用于在间隔的影像图框累积相对所述场景的所述相同位置的所述像素数据。

13.本发明还提供一种时延积分互补式金属氧化物半导体图像传感器,使用滚动快门获取影像图框并用于相对场景朝向沿轨方向移动。所述图像传感器包含像素阵列以及多个积分器。该像素阵列包含多个像素列,每一所述像素列包含多个像素配置于所述沿轨方向,且所述像素的两相邻像素组之间具有分隔距离以补偿使用所述滚动快门时的行时间差,其中每一所述素组包含第一像素及第二像素。所述积分器用于在连续影像图框中,分别储存相对所述场景的相同位置的像素数据,其中,在一倍所述行时间差下,所述积分器的每一者用于在相邻的影像图框累积相对所述场景的所述相同位置的所述像素数据,及在两倍所述行时间差下,与所述第一像素相关的积分器的每一者用于在下一个影像图框累积相对所述场景的所述相同位置的所述像素数据且与所述第二像素相关的积分器的每一者不用于在所述下一个影像图框累积相对所述场景的所述相同位置的所述像素数据。

14.本发明实施例中,所述分隔距离与像素阵列的尺寸(即像素数目)不直接相关,只要决定了图框期间及行时间差,即可决定所述分隔距离。

15.为了让本发明的上述和其他目的、特征和优点能更明显,下文将配合所附图示,详细说明如下。此外,于本发明的说明中,相同的构件以相同的符号表示,于此合先述明。

附图说明

16.图1是已知用于时延积分取像的cmos图像传感器的示意图;

17.图2是本发明第一实施例的tdi cmos图像传感器的示意图;

18.图3是图2的tdi cmos图像传感器的一种运作示意图;

19.图4a是图2的tdi cmos图像传感器的另一运作示意图;

20.图4b是图2的tdi cmos图像传感器中于分隔距离中配置缓冲器的示意图;

21.图5是本发明第二实施例的tdi cmos图像传感器的示意图;

22.图6是图5的tdi cmos图像传感器的运作示意图;

23.图7a至图7c显示图2的tdi cmos图像传感器在不同行时间差下的运作示意图;

24.图8a至图8c显示图2的tdi cmos图像传感器在不同行时间差下的另一运作示意图;及

25.图9a至图9c显示图5的tdi cmos图像传感器在不同行时间差下的运作示意图。

26.附图标记说明

27.500

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

tdi cmos图像传感器

28.51

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

像素阵列

29.512

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

像素列

30.5123

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一像素

31.5124

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

分隔距离

32.5125

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二像素

33.513、515

ꢀꢀꢀꢀꢀ

读取线

34.53

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一读取电路

35.55

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二读取电路

36.57

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制电路

37.d

a_t

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

沿轨方向

具体实施方式

38.本发明实施例的互补式金属氧化物半导体(cmos)图像传感器通过于沿轨方向(along

‑

track direction)配置像素分隔距离,以补偿使用滚动快门进行时间延迟(time delay integration,tdi)取像时的行时间差。藉此,连续影像图框可在被取像场景中,累积相对相同位置的像素数据,以增加信噪比(snr),其中,可累积的次数与像素阵列的尺寸相关。

39.时间延迟取像的概念为已知,本发明在于消除tdi cmos图像传感器使用滚动快门技术时所产生的取像失真。

40.请参照图2,其为本发明第一实施例的用于时延积分取像的cmos图像传感器200的示意图。tdi cmos图像传感器200是使用滚动快门(rolling shutter)获取影像图框并用于相对场景(scene)朝向沿轨方向d

a_t

移动,其中所述场景根据tdi cmos图像传感器200的应用而定。例如,当tdi cmos图像传感器200应用于扫描仪时,所述场景则为被扫描文件;当tdi cmos图像传感器200应用于卫星或飞行器时,所述场景则为地面。

41.滚动快门的运作则为已知,故于此不再详述。

42.tdi cmos图像传感器200包含像素阵列21。该像素阵列21包含多个像素列212。每一所述像素列212包含多个像素2123(此处以斜线区域表示)配置于所述沿轨方向d

a_t

(例如像素阵列21的纵向方向)。每一所述像素列212的两相邻像素之间具有分隔距离2124(此处

以空白区域表示)。

43.请参照图3,其显示图2的tdi cmos图像传感器200的一种运作示意图。一种实施方式中,所述分隔距离2124等于一个像素2123在所述沿轨方向d

a_t

的像素高度w乘上滚动快门的行时间差(line time difference)t与获取所述影像图框(例如图3显示3个影像图框)的图框期间t的时间比例,亦即w

×

t/t。

44.本发明中,所述行时间差t是指像素阵列21的两相邻像素行(pixel row)开始曝光或结束曝光的时间间隔。

45.图3中,假设场景包含三个位置或物体a、b及c朝向右方(即沿轨方向d

a_t

)移动。stage1及stage2表示每一像素列112的两行像素,其中,stage1及stage2之间具有所述分隔距离w

×

t/t。本发明中,图框期间t由场景的亮度及像素阵列21的感光度决定。tdi cmos图像传感器200的移动速度设定为所述像素高度w除以所述图框期间t。

46.由于图3是假设像素阵列21的所述像素列212具有两行像素,故tdi cmos图像传感器200获取一张影像图框的图框期间t内包含两个行时间,其具有行时间差t。此处,所述行时间是指一行像素完成曝光及读取所需的处理时间。例如,图3显示第一影像图框包含两行像素f

1_1

及f

1_2

;第二影像图框包含两行像素f

2_1

及f

2_2

;第三影像图框包含两行像素f

3_1

及f

3_2

。

47.本实施例中,tdi cmos图像传感器200还包含多个积分器,例如图3显示两个积分器31及32,其中,积分器例如是缓存器(数字积分器)或电容器(模拟积分器),且其数量较佳对应所述像素列212的数目,以决定被取像场景的宽度。积分器31及32分别用于累积相邻影像图框中,相对所述场景的相同位置或相同物体的像素数据。

48.例如,第一影像图框(例如包含f

1_1

及f

1_2

)中,stage1感测场景的位置或物体a的像素数据并累积(或加总)于积分器31,其显示为i

a

;此时积分器32尚未累积像素数据,故显示为0。

49.由于所述场景是以w/t的移动速度朝向沿轨方向d

a_t

移动,在第二影像图框(例如包含f

2_1

及f

2_2

)中,stage1感测所述场景的位置或物体b的像素数据并累积(或加总)于积分器32,其显示为i

b

;stage2感测所述场景的位置或物体a的像素数据并累积(或加总)于积分器31,其显示为2i

a

(表示累积两次)。

50.由于所述场景持续以w/t的移动速度朝向沿轨方向d

a_t

移动,在第三影像图框(例如包含f

3_1

及f

3_2

)中,先前累积于积分器31中相关于物体a的像素数据2i

a

先被读出。接着,stage1感测所述场景的位置或物体c的像素数据并累积(或加总)于积分器31,其显示为i

c

;stage2感测所述场景的位置或物体b的像素数据并累积(或加总)于积分器32,其显示为2i

b

(表示累积两次)。当持续感测所述场景时,tdi cmos图像传感器200则持续以图3所显示的方式累积并读出像素资料,以增加信噪比。

51.一种实施方式中,图框期间t(或称为一张影像图框的曝光期间)大于以滚动快门获取所述像素阵列21的全部像素行的行曝光时间和,例如图3显示每一影像图框的第二行像素完成曝光及读取后,还剩余额外时间t

extra

。

52.一种非限定的实施方式中,所述图框期间t与所述行曝光时间和的一时间差(即t

extra

)中,图像传感器200进入休眠模式,以节省耗能。

53.另一种非限定的实施方式中,tdi cmos图像传感器200的列模拟数字转换器(例如

包含于读取电路23中)在所述时间差t

extra

中用于对辅助像素(例如黑像素)的像素信号、像素阵列21的外部电压值或温度传感器的温度值进行模拟数字转换。更详言之,在所述时间差t

extra

中,所述列模拟数字转换器可用于针对所述像素列112以外的感测信号进行模拟数字转换,以增加tdi cmos图像传感器200的应用范围。本实施方式中,行时间较佳设定为处理一行像素数据所需的最短时间。

54.本实施例中,读取电路23例如使用相关性双重取样(cds)来对各像素进行取样。

55.请再参照图2,另一种实施方式中,所述分隔距离2124等于一个像素在沿轨方向d

a_t

的像素高度w加上该像素高度w乘上所述滚动快门的行时间差t与获取影像图框的图框期间t的时间比例,亦即w

×

(y+t/t)。

56.请同时参照图4a,其为图2的tdi cmos图像传感器200的另一种运作示意图。图4a中,假设场景包含八个位置或物体a至h朝向右方(即沿轨方向d

a_t

)移动。stage1至stage4表示一个像素列112的四行像素,其中,两相邻像素之间具有所述分隔距离w

×

(y+t/t),其中,y=0或正整数。图4a是显示y=1时的实施方式;当y=0时,则形成图3的实施方式。

57.由于图4a是假设像素阵列21具有四行像素,故tdi cmos图像传感器200获取一张影像图框的图框期间t内包含四个行时间,其两两间具有一行时间差t。例如,图4a显示影像图框包含四行像素f

1_1

至f

1_4

;下一个影像图框包含四行像素f

2_1

至f

2_4

;再下一个影像图框显示包含四行像素f

3_1

至f

3_4

;依此类推。

58.同理,tdi cmos图像传感器200还包含多个积分器,例如图4a显示四个积分器41至44。积分器41用于储存第一影像图框(例如f

1_1

至f

1_4

图框)及第二影像图框(例如f

3_1

至f

3_4

图框)中,相对所述场景的相同位置(例如位置或物体f)的像素数据,其中所述第一影像图框与所述第二影像图框相差一个影像图框(例如f

2_1

至f

2_4

图框)。其他积分器42至44的运作方式与积分器41相同,差别在于累积不同位置或物体的像素数据。

59.从图4a中可以看出,所述第一影像图框中用于感测所述相同位置(例如f)的像素数据(例如if)的第一像素(例如stage1)与所述第二影像图框中用于感测所述相同位置(例如f)的像素数据(例如if)的第二像素(例如stage2),是所述像素阵列21中同一像素列212的两相邻像素。因此,积分器(例如41至44)在所述第一影像图框与所述第二影像图框间的所述影像图框的图框期间中,不累积所述第一像素及所述第二像素的所述相同位置的所述像素数据if。位置或物体d及b的感测及累积,在图4a中亦以虚线及箭号表示。

60.图4a的实施方式中,由于积分器41至44是间隔一张影像图框(例如f

2_1

至f

2_4

图框)累积相对场景的相同位置或相同物体的像素数据,若假设所述像素列112具有n个像素,所述积分器41至44则累积n/2次相对所述场景的相同位置或相同物体的像素数据。

61.影像图框f

2_1

至f

2_4

的像素资料则累积于另一组积分器,其同样是间隔一张影像图框(例如f

3_1

至f

3_4

图框)累积相对所述场景的相同位置或相同物体的像素数据。

62.当y=n时,所述场景的相同位置会在n个影像图框后被同一像素列212中的下一个相邻像素感测。只要透过配置控制电路27输出的控制信号,所述场景的相同位置或物体的像素数据,可正确累积于相同积分器中。

63.此外,图4a的实施例中,由于像素列112的相邻像素之间具有较大的分隔距离2124,在需要获取较宽的场景影像的实施方式中,可通过在所述分隔距离2124中每相隔预定列像素即配置缓冲器用于缓冲或放大像素行的控制信号。例如图4b所示,分隔距离2124

中,配置有缓冲器49用于缓冲或放大像素控制信号,例如包括重置信号srst、电荷转移信号sgt及行选择信号srs等,但并不限于此。藉此,可使得具有高像素列数目的像素阵列得以正确运作。

64.请参照图5所示,其为本发明第二实施例的用于时延积分取像的cmos图像传感器500的示意图。tdi cmos图像传感器500同样使用滚动快门获取影像图框并相对场景朝向沿轨方向d

a_t

移动。

65.tdi cmos图像传感器500包含像素阵列51。该像素阵列51包含多个像素列512,每一所述像素列512包含多个像素配置于所述沿轨方向d

a_t

。所述像素的两相邻像素组之间具有分隔距离5124以补偿使用滚动快门时的行时间差,其中每一所述像素组包含第一像素5123及第二像素5125彼此相连接,亦即其间并不具有所述分隔距离5124。

66.tdi cmos图像传感器500还包含第一读取电路53及第二读取电路54。如图5所示,所述第一读取电路53通过读取线513耦接所述像素列512中的多个第一像素5123,以读取所述第一像素5123的像素数据;所述第二读取电路55通过读取线515耦接所述像素列512中的多个第二像素5125,以读取所述第二像素5125的像素数据。

67.请参照图6,其显示图5的cmos图像传感器500的一种运作示意图。一种实施方式中,所述分隔距离5124等于一个像素在所述沿轨方向d

a_t

的像素高度w乘上滚动快门的行时间差t与获取所述影像图框(例如图6显示2个影像图框)的图框期间t的时间比例,亦即w

×

t/t。

68.图6中,假设场景包含八个位置或物体a至h朝向右方(即沿轨方向d

a_t

)移动。

69.本实施例中,读取电路53及55例如使用相关性双重取样来对各像素进行取样。图6中,stage1及stage2、stage3及stage4、stage5及stage6、stage7及stage8分别表示一个像素列112的像素组,其中stage1、stage3、stage5、stage7例如为第一像素5123;而stage2、stage4、stage6、stage8例如为第二像素5125。两相邻像素组之间具有所述分隔距离w

×

t/t。

70.由于图6是假设像素阵列51中在所述沿轨方向d

a_t

具有4个像素组,故tdi cmos图像传感器500获取一张影像图框的图框期间t内包含四个行时间,其两两间具有行时间差t。例如,图6显示第一影像图框包含四行像素组f

1_1

至f

1_4

;一第二影像图框包含四行像组f

2_1

至f

2_4

。

71.本实施例中,每一像素组中的第一像素5123与第二像素5125同时曝光且其像素数据分别被第一读取电路53及第二读取电路55同时累积。

72.例如,第一影像图框(例如f

1_1

至f

1_4

图框)的f

1_2

的行时间中,stage3及stage4同时曝光,stage3的像素数据(例如i

d

)被第一读取电路53累积至积分器63而stage4的像素数据(例如i

c

)被第二读取电路55累积至积分器64;所述第一影像图框的f

1_3

的行时间中,stage5及stage6同时曝光,stage5的像素数据(例如i

b

)被第一读取电路53累积至积分器65而stage6的像素数据(例如i

a

)被第二读取电路55累积至积分器66。第一影像图框的图框期间中其他行时间的曝光及累积方式与f

1_2

及f

1_3

的行时间相同。

73.例如,第二影像图框(例如f

2_1

至f

2_4

图框)的f

2_3

的行时间中,stage5及stage6同时曝光,stage5的像素数据(例如i

c

)被第一读取电路53累积至积分器64,其显示为2i

c

以表示累积两次;而stage6的像素数据(例如i

b

)被第二读取电路55累积至积分器65,其显示为2i

c

以表示累积两次。第二影像图框的图框期间中其他行时间的曝光及累积方式与f

2_3

的行时间相同。

74.例如,第一读取电路53及第二读取电路55分别通过开关组件(例如多任务器)耦接每一个积分器,所述开关组件通过控制信号(例如由控制电路57所产生)累积第一读取电路53或第二读取电路55所读取的像素数据至同一个积分器。可以了解的是,图6仅显示用于说明本发明的部分积分器。

75.更详言之,tdi cmos图像传感器500的多个积分器分别用于储存相邻的第一影像图框(例如包含f

1_1

至f

1_4

的图框)及第二影像图框(例如包含f

2_1

至f

2_4

的图框)中,相对场景的相同位置(例如b)的像素数据,其中所述第一影像图框中,相对所述场景的所述相同位置(例如b)的像素数据(例如i

b

)是由所述第一读取电路53读取而累积至一积分器65,而所述第二影像图框中,相对所述场景的所述相同位置(例如b)的像素数据(例如i

b

)是由所述第二读取电路55读取而累积至所述积分器65。只要透过配置控制电路57的输出信号,即使是由不同读取电路读出的像素数据,亦能够正确累积于相同积分器。其他积分器累积相关像素的像素数据的方式类似本段说明,故于此不再赘述。

76.其他实施方式中,上述图2及图5的实施例可以合并实现。例如,图5的两相邻像素组之间的分隔距离可为至少一个像素高度w加上一个像素高度w乘上滚动快门的行时间差t与获取影像图框的图框期间t的时间比例,亦即w

×

(y+t/t)。

77.某些实施方式中,本发明实施例的tdi cmos图像传感器200及500可操作于不同模式,例如包含正常模式及去噪模式。例如,正常模式下,tdi cmos图像传感器200及500以上述图3至图4a及图6的方式运行。在环境条件较差(例如环境光亮度比阈值低或噪声比阈值高)时,tdi cmos图像传感器200及500的处理器(例如微处理器、数字信号处理器或特定应用集成电路等)可根据目前环境条件自动选择运行模式,或者用户可通过tdi cmos图像传感器200及500的按键、开关或应用程序(app)来选择操作模式。

78.所述处理器连接至积分器(例如31~32、41~44、63~66、71~73、81~84或91~98)接收累积的像素数据并进行后处理。

79.接着,举例说明具有不同运行模式的tdi cmos图像传感器200及500的详细内容。去噪模式中,滚动快门的行时间差为正常模式的两倍,即2t。例如,去噪模式中,tdi cmos图像传感器200及500的多个像素在每个行时间(line time)中均进行强曝光(例如曝光时间较长和/或增益较高)以取得亮影像图框及弱曝光(例如曝光时间较短和/或增益较低)以取得暗影像图框。所述亮暗影像图框通过像素电路或读取电路的差分运算以产生差分影像图框,藉以消除噪声。需要改变行时间差的条件视不同应用而定。

80.此外,一种实施方式中,正常模式(例如一倍行时间差t)及去噪模式(例如两倍行时间差2t)下,tdi cmos图像传感器200及500相对被取像场景的移动速度相同。

81.请参照图7a至图7c所示,其为图2的tdi cmos图像传感器200在不同行时间差下的运作示意图,其中分隔距离2124等于w

×

(t/t)。本实施方式中,图7a是一倍行时间差的运作示意图;图7b是两倍行时间差的运作示意图;图7c是不同行时间差下tdi cmos图像传感器200的像素数据的累积及输出。

82.由于图7a至图7c的实施方式同样适用于图2的tdi cmos图像传感器200,故其像素阵列21包含多个像素列212,每一所述像素列212包含多个像素2123配置于沿轨方向da_t,

且每一所述像素列212的两相邻像素之间具有分隔距离2124。一种实施方式中,该分隔距离2124等于一个像素在沿轨方向da_t的像素高度w乘上滚动快门的行时间差t与获取影像图框的图框期间t的时间比例,因其已说明于上,故于此不再赘述。

83.本实施例中,tdi cmos图像传感器200是以包含三个积分器71~73为例进行说明。同样地,积分器71~73用于在连续影像图框中,分别储存相对被取像场景的相同位置的像素数据。

84.在图7a所示的正常模式下,tdi cmos图像传感器200的运行与图3相类似,积分器71~73的每一者用于在相邻的影像图框(例如显示为图框1至图框4)累积相对被取像场景的相同位置的像素数据。如图7a及7c所示,位置或物体a的像素数据i

a

在影像图框1至3均被累积(例如分别显示为1i

a

、2i

a

及3i

a

)至积分器。图7a及图7c中,积分器71~73例如是先进先出(fifo)缓冲器,因此每经过一个影像图框,积分器中的数据即被移动至下一个积分器,而积分器71则输出最终的累积像素数据至处理器。但本发明并不限于此,累积像素数据的方式也可如图3所示来进行,即同一个像素相关的像素数据累积至相同积分器。

85.在图7b所示的去噪模式下,tdi cmos图像传感器200的积分器71~73的每一者用于在间隔的影像图框累积相对被取像场景的相同位置的像素数据。如图7b及图7c所示,位置或物体a的像素数据i

a

在影像图框1及3均被累积(例如分别显示为1i

a

及2i

a

)至积分器,而在影像图框2则不被累积(例如均显示为1i

a

)至积分器。

86.如图7c所示,由于两倍行时间差下,被取像位置或物体的像素数据并不是在连续的影像图框被累积,所以积分器71~73的每一者累积相对被取像场景的相同位置的像素数据的累积次数,低于一倍行时间差下的累积次数。例如图7c显示一倍行时间差下像素资料的累积次数为3次而两倍行时间差下像素数据的累积次数为2次,但本发明并不限于此。

87.请参照图8a至图8c所示,其为图2的tdi cmos图像传感器200在不同行时间差下的另一运作示意图,其中分隔距离2124等于w

×

(t/t)。本实施方式中,图8a是一倍行时间差的运作示意图;图8b是两倍行时间差的运作示意图;图8c是不同行时间差下tdi cmos图像传感器200的像素数据的累积及输出。图8a至图8c与图7a至图7c的主要差异在于每行的像素数目不同且积分器的数目不同。

88.同样地,多个积分器81~84用于在连续影像图框中,分别储存相对被取像场景的相同位置的像素数据,其中,在一倍行时间差下,积分器81~84的每一者用于在相邻的影像图框累积相对被取像场景的相同位置的像素数据,例如图8a及图8c显示像素数据i

a

在影像图框1至4分别为1i

a

、2i

a

、3i

a

、4i

a

;在两倍行时间差下,积分器81~84的每一者用于在间隔的影像图框累积相对被取像场景的相同位置的像素数据,例如图8b及图8c显示像素数据i

a

在影像图框1及3分别为1i

a

、2i

a

,但像素数据i

a

在影像图框2不累积。

89.此外,图8b及图8c还显示在两倍行时间差下,一部分所述积分器(例如积分器81)不运行或被旁路(bypass),不运行的积分器并无特定限制。

90.假设影像图框2、影像图框3及影像图框4为连续的影像图框。图8a中,读取电路23(参照图2)连续地读取影像图框3中所述像素列的像素,例如像素stage1、像素stage2及像素stage3的像素数据均被读取并累积至相对应的积分器。图8b中,读取电路23间隔地读取影像图框3中所述像素列的像素,例如仅像素stage1及像素stage3的像素数据被读取并累积至相对应的积分器而像素stage2的像素数据不被读取。

91.请参照图9a至图9c所示,其为图5的tdi cmos图像传感器500在不同行时间差下的运作示意图,其中两像素组之间的分隔距离5124等于w

×

(t/t)。本实施方式中,图9a是一倍行时间差的运作示意图;图9b是两倍行时间差的运作示意图;图9c是不同行时间差下tdi cmos图像传感器500的像素数据的累积及输出。

92.由于图9a至图9c的实施方式同样适用于图5的tdi cmos图像传感器500,故其像素阵列51包含多个像素列512,每一所述像素列512包含多个像素配置于沿轨方向da_t,且所述像素的两相邻像素组之间具有分隔距离5124以补偿使用滚动快门时的行时间差t,其中每一所述像素组包含第一像素5123及第二像素5125。本实施例中,第二像素5125在所述沿轨方向da_t的远端且第一像素5123在所述沿轨方向da_t的近端。

93.本实施例中,tdi cmos图像传感器500是以包含八个积分器91~98为例进行说明。同样地,积分器91~98用于在连续影像图框中,分别储存相对被取像场景的相同位置的像素数据。

94.在图9a所示的正常模式下,tdi cmos图像传感器500的运行与图6相类似,积分器91~98的每一者用于在相邻的影像图框(例如显示为图框1至图框4)累积相对被取像场景的相同位置的像素数据。如图9a及9c所示,位置或物体f的像素数据i

f

在影像图框1至8均被累积(例如分别显示为1i

f

、2i

f

、3i

f

、4i

f

、5i

f

、6i

f

、7i

f

及8i

f

)至积分器。图9a及图9c中,积分器91~98例如是先进先出缓冲器,因此每经过一个影像图框,积分器中的数据即被移动至下一个积分器,而积分器91则输出最终的累积像素数据至处理器。但本发明并不限于此,累积像素数据的方式也可如图6所示来进行,即同一个像素相关的像素数据累积至相同积分器。

95.在图9b所示的去噪模式下,与第一像素5123相关的积分器的每一者用于在下一个影像图框累积相对被取像场景的相同位置的像素数据且与第二像素5125相关的积分器的每一者不用于在所述下一个影像图框累积相对被取像场景的相同位置的像素数据。如图9b及图9c所示,影像图框1中,位置或物体f(例如被像素stage1感测,而称为与第一像素5123相关)的像素数据i

f

在影像图框1及2均被读取及累积;影像图框1中,位置或物体e(例如被像素stage2感测,而称为与第二像素5125相关)的像素数据i

e

在影像图框1及4才被读取及累积而在影像图框2及3不被读取及累积。

96.换句话说,本实施方式中,在两倍行时间差下,被取像场景的一个相同位置的像素数据交替的在相邻影像图框或间隔两个影像图框被累积至相关的积分器。例如图9b及9c中,位置或物体f的像素数据i

f

在影像图框1及2被连续读取及累积(例如分别显示为1i

f

及2i

f

)但在影像图框3及4不被读取及累积(例如均显示为2i

f

),而在影像图框5及6再被连续读取及累积(例如分别显示为3i

f

及4i

f

)。

97.同理,由于在两倍行时间差下被取像位置或物体的像素数据并不是连续的被累积,所以积分器91~98的每一者累积相对被取像场景的相同位置的像素数据的累积次数,低于一倍行时间差下的累积次数。例如的9c显示两倍行时间差下像素资料的累积次数为4次而一倍行时间差下像素数据的累积次数为8次,但本发明并不限于此。

98.类似地,图9b及图9c中,一部分所述积分器(例如积分器91及92)不运行或被旁路,不运行的积分器并无特定限制。

99.藉此,本发明实施例的tdi cmos图像传感器200及500可以实现在固定的分隔距离下操作于不同行时间差。

100.可以了解的是,本发明各实施例及图式中的数值,例如像素数目、积分器数目、影像图框数目等仅用以说明,并非用以限定本发明。

101.综上所述,当cmos图像传感器使用滚动快门技术时,因为像素阵列的所有像素并非同时开始并结束曝光,而使得累积的像素感测数据并非完全相对应场景中的相同位置或物体而产生失真。有鉴于此,本发明另提出一种使用滚动快门的时延积分cmos传感器(例如参照图2及图5)及其运作方法(例如参照图3、图4a及图6),其通过设置不同的像素分隔距离,来补偿滚动快门的行时间差所造成的失真。通过相对配置控制电路的控制信号,即能正确累积相对位置的像素数据至相关的积分器。

102.虽然本发明已通过前述实例披露,但是其并非用以限定本发明,任何本发明所属技术领域中具有通常知识技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与修改。因此本发明的保护范围当视后附的权利要求所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1