四通道多功能芯片的制作方法

1.本发明属于微波单片集成电路领域,尤其涉及一种四通道多功能芯片。

背景技术:

2.在微波毫米波相控阵天线系统中,tr(transmitter and receiver)组件为相控阵天线基本模块单元,起到幅度控制、相位控制的功能,主要由限幅器、放大器和多功能芯片组成,而多功能芯片是tr组件的核心组件。针对不同功能的tr组件,多功能芯片需要不同的功能,由此多功能芯片的性能指标也会不同。

3.电压驻波比是衡量多功能芯片性能的重要指标。电压驻波比表示输入输出端口信号的反射程度,也可以体现端口的失配程度。现有技术中,tr组件的多功能芯片的输入端口接低噪声放大器芯片的输出端口,多功能芯片的输出端口接功率放大器芯片的输入端口,以在芯片之间进行信号传输。

4.但是,各个芯片进行信号传输时,多功能芯片的输入端口和输出端口的能量损失比较严重,即输入端口和输出端口的电压驻波比差。

技术实现要素:

5.有鉴于此,本发明实施例提供了一种四通道多功能芯片,以解决现有技术中四通道多功能芯片的输入端口和输出端口的电压驻波比差的问题。

6.本发明实施例的第一方面提供了一种四通道多功能芯片,包括:

7.多功能芯片的输入端、多功能芯片的四个输出端、多功能芯片的供电端、多功能芯片的接地端、放大器、栅端供电端、漏端供电端、一分四功分器、四个移相器、三个串转并驱动器、数据锁存端、数据输入端、时钟端和片选端;

8.多功能芯片的四个输出端包括多功能芯片的第一输出端、多功能芯片的第二输出端、多功能芯片的第三输出端和多功能芯片的第四输出端;

9.四个移相器包括第一移相器、第二移相器、第三移相器和第四移相器;

10.三个串转并驱动器包括第一串转并驱动器、第二串转并驱动器和第三串转并驱动器;

11.放大器分别连接多功能芯片的输入端、栅端供电端、漏端供电端和一分四功分器;

12.一分四功分器分别连接第一移相器、第二移相器、第三移相器和第四移相器,第一移相器连接多功能芯片的第一输出端,第二移相器连接多功能芯片的第二输出端,第三移相器连接多功能芯片的第三输出端,第四移相器连接多功能芯片的第四输出端;

13.第一串转并驱动器分别连接第二串转并驱动器、第三串转并驱动器、多功能芯片的供电端、多功能芯片的接地端、数据锁存端、数据输入端、时钟端和片选端,第二串转并驱动器与第三串转并驱动器连接;

14.第三串转并驱动器连接第一移相器和第二移相器,第二串转并驱动器连接第三移相器和第四移相器;

15.第一移相器、第二移相器、第三移相器和第四移相器中的至少之一包括移相功能模块,移相功能模块至少包括衰减电路。

16.本发明实施例与现有技术相比存在的有益效果是:

17.本发明实施例的一种四通道多功能芯片,包括:多功能芯片的输入端、多功能芯片的四个输出端、多功能芯片的供电端、多功能芯片的接地端、放大器、栅端供电端、漏端供电端、一分四功分器、四个移相器、三个串转并驱动器、数据锁存端、数据输入端、时钟端和片选端;第一移相器、第二移相器、第三移相器和第四移相器中的至少之一包括移相功能模块,移相功能模块至少包括衰减电路。本发明通过在移相器中设置衰减电路,对输出信号进行衰减,有效改善与移相器连接的输出端口的电压驻波比,从而提高四通道多功能芯片的性能。

附图说明

18.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

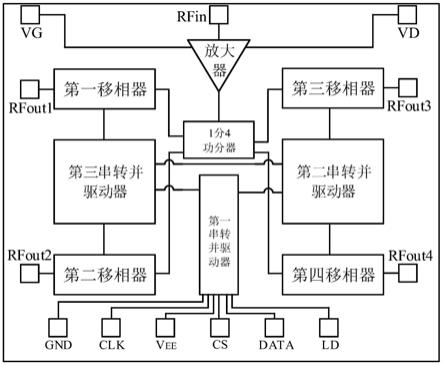

19.图1是本发明一实施例提供的一种四通道多功能芯片的结构示意图;

20.图2是本发明另一实施例提供的一种四通道多功能芯片的结构示意图;

21.图3是本发明实施例提供的一种四通道多功能芯片内rfin

‑

rfout1移相功能模块的电路示意图;

22.图4是本发明实施例提供的一种四通道多功能芯片内rfin

‑

rfout1移相功能模块的电路版图;

23.图5是本发明实施例提供的一种四通道多功能芯片的第一输出端口rfout1的电压驻波比测试曲线示意图;

24.图6是本发明实施例提供的一种四通道多功能芯片的第一输出端口rfout1的阻抗史密斯圆图测试曲线示意图;

25.图7是本发明实施例提供的改进后的一种四通道多功能芯片内rfin

‑

rfout1移相功能模块的电路示意图;

26.图8是本发明实施例提供的改进后的一种四通道多功能芯片内rfin

‑

rfout1移相功能模块的电路版图;

27.图9是本发明实施例提供的改进后的一种四通道多功能芯片的第一输出端口rfout1的电压驻波比测试曲线示意图;

28.图10是本发明实施例提供的改进后的一种四通道多功能芯片的第一输出端口rfout1的阻抗史密斯圆图测试曲线示意图。

具体实施方式

29.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本发明实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本发明。在其它情况中,省略对众所周知的系统、装置、电

路以及方法的详细说明,以免不必要的细节妨碍本发明的描述。

30.为了说明本发明的技术方案,下面对多通道多功能芯片的性能指标进行说明。

31.多通道多功能芯片重要性能指标如下:

32.1.工作频率:一般为一个工作频带范围,如14ghz~18ghz、19ghz~23ghz、29ghz~31ghz等。

33.2.增益:表示芯片对信号的放大能力,可以表示为输出功率比输入功率,即glin=pout/pin。

34.3.输入输出电压驻波比:表示输入输出端口信号的反射程度,也可以体现端口的失配程度,即vswr=(1+|γ|)/(1

‑

|γ|),式中γ为端口的电压反射系数。

35.4.移相位数、移相步进及移相范围:移相位数6位,移相步进5.625

°

,总计63个移相状态,移相范围5.625

°

~354.375

°

。

36.5.相对移相量:各个移相态的相对移相量为psi=|phase(相应移相态的s21)

‑

phase(参考态的s21)|。

37.6.移相精度:各个移相态的移相精度为δφi=psi

‑

相应移相态的标称值

38.7.移相均方根误差:其中n=63。

39.8.各通道间幅度一致性:

40.各通道参考态下增益gi=db(参考态的s21)i,i=1,2,3,

…

,n;

41.各通道间幅度一致性指同一频率下同一被测芯片在参考态下不同通道间的增益一致性,即δam=max(g1,g2,g3,

…

,gn)

‑

min(g1,g2,g3,

…

,gn)。

42.9.各通道间相位一致性:

43.各通道参考态下相位phi=|phase(参考态的s21)i|,i=1,2,3,

…

,n;

44.各通道间相位一致性指同一频率下同一被测芯片在参考态下不同通道间的相位一致性,δφn=max(ph1,ph2,ph 3,

…

,ph n)

‑

min(ph 1,ph 2,ph 3,

…

,ph n)。

45.注1:db()是将s参数的幅度相位形式转换为分贝表示的函数。

46.注2:phase()是将s参数的幅度相位形式转换为相位表示的函数。

47.注3:s参数中的2、1对应的是测试时被测芯片的输出端口和输入端口。

48.注4:参考态指不进行移相的状态。

49.在tr组件中,大多数情况下多功能芯片输入端口接低噪声放大器芯片的输出端口,多功能芯片输出端口接功率放大器芯片的输入端口;为尽量降低各个芯片之间能量传递的损失,要求各个芯片之间对接的端口具有良好的电压驻波比。本发明给出了一种优化方法,可改善多功能芯片的电压驻波比。为了说明本发明的技术方案,下面通过具体实施例来进行说明。

50.图1是本发明一实施例提供的一种四通道多功能芯片的电路示意图。如图1所示,该实施例的一种四通道多功能芯片包括:

51.多功能芯片的输入端rfin、多功能芯片的四个输出端rfout1

‑

rfout4、多功能芯片的供电端v

ee

、多功能芯片的接地端gnd、放大器、栅端供电端vg、漏端供电端vd、一分四功分器、四个移相器、三个串转并驱动器、数据锁存端ld、数据输入端data、时钟端clk和片选端cs;

52.多功能芯片的四个输出端包括多功能芯片的第一输出端rfout1、多功能芯片的第二输出端rfout2、多功能芯片的第三输出端rfout3和多功能芯片的第四输出端rfout4;

53.四个移相器包括第一移相器、第二移相器、第三移相器和第四移相器;

54.三个串转并驱动器包括第一串转并驱动器、第二串转并驱动器和第三串转并驱动器;

55.放大器分别连接多功能芯片的输入端rfin、栅端供电端vg、漏端供电端vd和一分四功分器;

56.一分四功分器分别连接第一移相器、第二移相器、第三移相器和第四移相器,第一移相器连接多功能芯片的第一输出端rfout1,第二移相器连接多功能芯片的第二输出端rfout2,第三移相器连接多功能芯片的第三输出端rfout3,第四移相器连接多功能芯片的第四输出端rfout4;

57.第一串转并驱动器分别连接第二串转并驱动器、第三串转并驱动器、多功能芯片的供电端v

ee

、多功能芯片的接地端gnd、数据锁存端ld、数据输入端data、时钟端clk和片选端cs,第二串转并驱动器与第三串转并驱动器连接;

58.第三串转并驱动器连接第一移相器和第二移相器,第二串转并驱动器连接第三移相器和第四移相器;

59.第一移相器、第二移相器、第三移相器和第四移相器中的至少之一包括移相功能模块,移相功能模块至少包括衰减电路。

60.在一实施例中,放大器对通过多功能芯片的输入端rfin输入的输入信号进行放大,放大后的输入信号经1分4功分器分配至第一移相器、第二移相器、第三移相器和第四移相器,第一移相器、第二移相器、第三移相器和第四移相器对流经各自的放大后的输入信号进行处理,其中,移相器为数字控制模式,移相步进5.625

°

,移相范围0

°

~354.375

°

。

61.进一步地,第一串转并驱动器、第二串转并驱动器和第三串转并驱动器组成24位串转并驱动器,输出24路0v/

‑

5v互补电压,分别为四个移相器内的phemt器件栅极提供0v或

‑

5v电压。第一串转并驱动器与外部输入端(数据锁存端ld、数据输入端data、时钟端clk和片选端cs)相连接,实现输入电平移位与单端转差分功能。第二串转并驱动器和第三串转并驱动器均为12位串转并驱动电路,共用时钟与锁存,级联形成24位串转并驱动电路,在规定的时序下实现24位串码转并行码;时钟端clk的输入信号进入第一串转并驱动器,产生差分信号1和2,分别输入第二串转并驱动器和第三串转并驱动器;数据锁存端ld的输入信号进入第一串转并驱动器,产生差分信号3和4,分别输入第二串转并驱动器和第三串转并驱动器;数据输入端data的输入信号进入第一串转并驱动器,产生差分信号5和6,进入第二串转并驱动器,经第二串转并驱动器串行输出后产生信号7和8,进入第三串转并驱动器。片选端cs的输入信号进入第一串转并驱动器,与时钟端clk的输入信号进行逻辑运算,以控制clk的输入信号。

62.在一实施例中,本技术通过在第一移相器、第二移相器、第三移相器和第四移相器中的至少之一设置的移相功能模块中的衰减电路,可有效改善与对应的移相器连接的输出端口的电压驻波比,以提高多通道多功能芯片的性能。

63.本发明实施例的一种四通道多功能芯片,包括:多功能芯片的输入端、多功能芯片的四个输出端、多功能芯片的供电端、多功能芯片的接地端、放大器、栅端供电端、漏端供电

端、一分四功分器、四个移相器、三个串转并驱动器、数据锁存端、数据输入端、时钟端和片选端;第一移相器、第二移相器、第三移相器和第四移相器中的至少之一包括移相功能模块,移相功能模块至少包括衰减电路。本发明通过在移相器中设置衰减电路,对输出信号进行衰减,有效改善与移相器连接的输出端口的电压驻波比,从而提高四通道多功能芯片的性能。

64.图2是本发明另一实施例提供的一种四通道多功能芯片的电路示意图。如图2所示,该实施例的一种四通道多功能芯片包括:

65.多功能芯片的输入端rfin、多功能芯片的四个输出端rfout1

‑

rfout4、多功能芯片的供电端v

ee

、多功能芯片的接地端gnd、放大器、栅端供电端vg、漏端供电端vd、一分四功分器、四个移相器、三个串转并驱动器、数据锁存端ld、数据输入端data、时钟端clk和片选端cs;

66.多功能芯片的四个输出端包括多功能芯片的第一输出端rfout1、多功能芯片的第二输出端rfout2、多功能芯片的第三输出端rfout3和多功能芯片的第四输出端rfout4;

67.四个移相器包括第一移相器、第二移相器、第三移相器和第四移相器;

68.三个串转并驱动器包括第一串转并驱动器、第二串转并驱动器和第三串转并驱动器;

69.放大器的第一输入端1连接多功能芯片的输入端rfin,放大器的第二输入端2连接栅端供电端vg,放大器的第三输入端3连接漏端供电端vd,放大器的输出端4连接一分四功分器的输入端1;

70.一分四功分器的第一输出端2连接第一移相器的第一输入端1,第一移相器的输出端3连接多功能芯片的第一输出端rfout1;一分四功分器的第二输出端3连接第二移相器的第一输入端1,第二移相器的输出端3连接多功能芯片的第二输出端rfout2;一分四功分器的第三输出端4连接第三移相器的第一输入端1,第三移相器的输出端3连接多功能芯片的第三输出端rfout3;一分四功分器的第四输出端5连接第四移相器的第一输入端1,第四移相器的输出端3连接多功能芯片的第四输出端rfout4;

71.第一串转并驱动器的引脚1和引脚7均连接多功能芯片的接地端gnd,第一串转并驱动器的引脚2连接时钟端clk,第一串转并驱动器的引脚3连接功能芯片的供电端v

ee

,第一串转并驱动器的引脚4连接片选端cs,第一串转并驱动器的引脚5连接数据输入端data,第一串转并驱动器的引脚6连接数据锁存端ld,第一串转并驱动器的引脚8连接第二串转并驱动器的引脚12,第一串转并驱动器的引脚9连接第二串转并驱动器的引脚11,第一串转并驱动器的引脚10连接第二串转并驱动器的引脚10,第一串转并驱动器的引脚11连接第二串转并驱动器的引脚9,第一串转并驱动器的引脚12连接第二串转并驱动器的引脚8,第一串转并驱动器的引脚13连接第二串转并驱动器的引脚7,第一串转并驱动器的引脚14连接第二串转并驱动器的引脚6,第一串转并驱动器的引脚15连接第二串转并驱动器的引脚5,第一串转并驱动器的引脚16连接第三串转并驱动器的引脚5,第一串转并驱动器的引脚17连接第三串转并驱动器的引脚4,第一串转并驱动器的引脚18连接第三串转并驱动器的引脚3,第一串转并驱动器的引脚19连接第三串转并驱动器的引脚2;

72.第三串转并驱动器的引脚6连接第二串转并驱动器的引脚4,第三串转并驱动器的引脚7连接第二串转并驱动器的引脚3;

73.第三串转并驱动器的引脚8连接第一移相器的第二输入端2,第三串转并驱动器的引脚1连接第二移相器的第二输入端2;第二串转并驱动器的引脚2连接第三移相器的第二输入端2,第二串转并驱动器的引脚1连接第四移相器的第二输入端2;

74.第一移相器、第二移相器、第三移相器和第四移相器中的至少之一包括移相功能模块,移相功能模块至少包括衰减电路。

75.在一实施例中,第三串转并驱动器与第一移相器、第二移相器的连接,可采用多条引线连接的形式,具体引线条数不作限定。以引线条数等于5为例,在第三串转并驱动器和第一移相器连接的情况下,第三串转并驱动器的引脚8a连接第一移相器的引脚2a,第三串转并驱动器的引脚8b连接第一移相器的引脚2b,第三串转并驱动器的引脚8c连接第一移相器的引脚2c,第三串转并驱动器的引脚8d连接第一移相器的引脚2d,第三串转并驱动器的引脚8e连接第一移相器的引脚2e。在第三串转并驱动器和第二移相器连接的情况下,第三串转并驱动器的引脚1a连接第二移相器的引脚2a,第三串转并驱动器的引脚1b连接第二移相器的引脚2b,第三串转并驱动器的引脚1c连接第二移相器的引脚2c,第三串转并驱动器的引脚1d连接第二移相器的引脚2d,第三串转并驱动器的引脚1e连接第二移相器的引脚2e。

76.同上述实施例,第二串转并驱动器与第三移相器、第四移相器的连接也可采用多条引线连接的形式,此处不再赘述。

77.现有技术中,四通道多功能芯片rfin

‑

rfout1通道、rfin

‑

rfout2通道、rfin

‑

rfout3通道和rfin

‑

rfout4通道的移相功能模块的电路结构容易导致四通道多功能芯片的四个输出端口的电压驻波比差,从而影响四通道多功能芯片的性能,下面以现有技术中的移相功能模块的电路示意图为例进行说明。

78.图3为现有技术中的四通道多功能芯片rfin

‑

rfout1通道的移相功能模块的电路示意图,由电感ind1~ind7、电容c1~c6、电阻r1~r2和phemt器件d1~d16组成。in端口接四通道多功能芯片内1分4功分器的第一输出端2,out端口为四通道多功能芯片的第一输出端rfout1。电容c3~c5、电感ind5~ind7和phemt器件d13~d16组成180

°

位,phemt器件d12为5.625

°

位,电阻r2、电感ind4和phemt器件d9~d11组成22.5

°

位,电感ind3和phemt器件d8组成11.25

°

位,电阻r1、电感ind2和phemt器件d5~d7组成45

°

位,电容c1~c2、电感ind1和phemt器件d1~d4组成90

°

位,具体加电工作方式如表1所示。

79.表1 phemt器件栅压和移相器基本态对照表

[0080] 参考态5.625

°

11.25

°

22.5

°

45

°

90

°

180

°

354.375

°

d10v0v0v0v0v

‑

5v0v

‑

5vd20v0v0v0v0v

‑

5v0v

‑

5vd3‑

5v0v0v0v0v0v0v0vd4‑

5v0v0v0v0v0v0v0vd50v0v0v0v

‑

5v0v0v

‑

5vd6‑

5v0v0v0v0v0v0v0vd7‑

5v0v0v0v0v0v0v0vd80v0v

‑

5v0v0v0v0v

‑

5vd90v0v0v

‑

5v0v0v0v

‑

5v

d

10

‑

5v0v0v0v0v0v0v0vd

11

‑

5v0v0v0v0v0v0v0vd

12

0v

‑

5v0v0v0v0v0v

‑

5vd

13

‑

5v0v0v0v0v0v0v0vd

14

‑

5v0v0v0v0v0v0v0vd

15

0v0v0v0v0v0v

‑

5v

‑

5vd

16

0v0v0v0v0v0v

‑

5v

‑

5v

[0081]

图4为现有技术中的四通道多功能芯片rfin

‑

rfout1通道的移相功能模块的电路版图,黑框内为电容c6,其容值0.58pf。图5为现有技术中的四通道多功能芯片的第一输出端口rfout1的电压驻波比的测试曲线示意图,由于移相功能单元为5.625

°

步进的6位移相器,参考态和移相态总计有26=64个状态,所以电压驻波比曲线有64根。从图5可以看出所有电压驻波比曲线中最大值达到了2.6。图6为四通道多功能芯片在64个状态下rfout1端口阻抗的史密斯圆图测试曲线,史密斯圆图圆心实部阻抗为50ω,对应电压驻波比为最佳理想值1。图6为现有技术中的四通道多功能芯片的第一输出端口rfout1的阻抗史密斯圆图测试曲线示意图,从图6可以看出所有曲线中距离史密斯圆图圆心最远的点为m1点,其实部阻抗为0.431

×

50=21.55ω,所以该点的电压驻波比最差。

[0082]

针对现有技术中的四通道多功能芯片的四个输出端口的电压驻波比差的问题,本技术提供一种改进的移相功能模块,其中,改进的移相功能模块包括:衰减电路、移相电路、移相功能模块的输入端和移相功能模块的输出端,移相功能模块的输入端、移相电路、衰减电路和移相功能模块的输出端依次连接。其中,衰减电路包括:π型固定衰减器。在移相功能模块中设置π型固定衰减器,可有效改善多功能芯片输出端口的电压驻波比。

[0083]

图7是本发明一实施例提供的一种改进后的移相功能模块的电路示意图。

[0084]

如图7所示,该实施例的一种改进后的移相功能模块的电路包括:

[0085]

第三电阻r3、第四电阻r4、第五电阻r5和第一接地端gnd1;第三电阻r3的第一端与第五电阻r5的第一端连接,第五电阻r5的第二端与第一接地端连接,第一接地端还与第四电阻r4的第一端连接,第四电阻r4的第二端与第三电阻r3的第二端连接;

[0086]

第一电阻r1、第二电阻r2、第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5、第一电感ind1、第二电感ind2、第三电感ind3、第四电感ind4、第五电感ind5、第六电感ind6、第七电感ind7、第一phemt d1、第二phemt d2、第三phemt d3、第四phemt d4、第五phemt d5、第六phemt d6、第七phemt d7、第八phemt d8、第九phemt d9、第十phemt d10、第十一phemt d11、第十二phemt d12、第十三phemt d13、第十四phemt d14、第十五phemt d15、第十六phemt d16、第二接地端gnd2、第三接地端gnd3、第四接地端gnd4、第五接地端gnd5、第六接地端gnd6和第七接地端gnd7;

[0087]

第十四phemt d14的第一端s连接第四电容c4的第一端,第四电容c4的第二端分别连接第七电感ind7的第一端和第三电容c3的第一端,第七电感ind7的第二端连接第二接地端gnd2,第三电容c3的第二端连接第十三phemt d13的第一端s,第十三phemt d13的第二端d分别连接第十二phemt d12的第一端d和第十五phemt d15的第一端d,第十五phemt d15的第二端s连接第五电感ind5的第一端,第五电感ind5的第二端分别连接第六电感ind6的第一端和第五电容的第一端,第五电容的第二端连接第三接地端,第六电感ind6的第二端连

接第十六phemt d16的第一端s,第十六phemt d16的第二端d连接第十四phemt d14的第二端d;

[0088]

第十二phemt d12的第二端s连接第九phemt d9的第一端d,第九phemt d9的第三端m分别连接第十phemt d10的第一端d和第二电阻r2的第一端,第十phemt d10的第二端s分别连接第十一phemt d11的第一端s和第二电阻r2的第二端,第二电阻r2的第二端还连接第四电感ind4的第一端,第四电感ind4的第二端和第十一phemt d11的第二端d均连接第四接地端gnd4;

[0089]

第九phemt d9的第二端s连接第八phemt d8的第一端d,第八phemt d8的第三端m连接第三电感ind3的第一端,第三电感ind3的第二端连接第五接地端gnd5;

[0090]

第八phemt d8的第二端s连接第五phemt d5的第一端d,第五phemt d5的第三端m连接分别连接第六phemt d6的第一端d和第一电阻r1的第一端,第六phemt d6的第二端s分别连接第七phemt d7的第一端s和第一电阻r1的第二端,第一电阻r1的第二端还连接第二电感ind2的第一端,第七phemt d7的第二端d和第二电感ind2的第二端均连接第六接地端gnd6;

[0091]

第五phemt d5的第二端s连接第二phemt d2的第一端d,第二phemt d2的第二端s连接第二电容c2的第一端,第二电容c2的第二端分别连接第一电容c1的第一端和第一电感ind1的第一端,第一电感ind1的第二端连接第七接地端gnd7,第一电容c1的第二端连接第一phemt d1的第一端s,第一phemt d1的第二端d连接第三phemt d3的第一端d,第三phemt d3的第二端s连接第四phemt d4的第一端s,第四phemt d4的第二端d连接第二phemt d2的第一端d;

[0092]

移相功能模块的输入端in连接第一phemt d1的第二端d,第十四phemt d14的第二端d连接第三电阻r3的第二端,第三电阻r3的第一端连接移相功能模块的输出端out。

[0093]

从图7可以看出,为了改善rfout1端口电压驻波比,把图3中的电容c6更换为图7中由r3~r5组成的π型固定衰减器,其中r3=10ω,r4=2900ω,r5=2460ω。图8为改进后的多功能芯片rfin

‑

rfout1通道移相功能模块的电路版图,对比图4和图8可以看出黑框内的版图由电容c6更换为电阻r3~r5构成的π型固定衰减器。

[0094]

图9为改进后的多功能芯片rfout1端口电压驻波比在64个状态下的测试曲线,电压驻波比最大值为1.8;图10为改进后的多功能芯片在64个状态下rfout1端口阻抗的史密斯圆图测试曲线,可以看出所有曲线中距离史密斯圆图圆心最远的m1点其实部阻抗为0.726

×

50=36.3ω,相比于改进前的21.55ω更接近史密斯圆图圆心。

[0095]

rfin

‑

rfout2、rfin

‑

rfout3和rfin

‑

rfout4通道内的移相功能单元与rfin

‑

rfout1通道内的移相功能单元是一样的,可以采取同样的方法改善rfout2、rfout3和rfout4端口的电压驻波比。

[0096]

通过比较图5、图6、图9和图10可以看出,用电阻构成的π型固定衰减器替代电容,改变电路的端口实部阻抗,可有效改善端口电压驻波比。

[0097]

在一实施例中,参见图2,移相功能模块的输入端in连接多功能芯片的1分4功分器的输出端口,移相功能模块的输出端out为多功能芯片的输出端口。

[0098]

具体地,在第一移相器中设置移相功能模块的情况下,移相功能模块的输入端in连接多功能芯片的1分4功分器的第一输出端口2,而移相功能模块的输出端out为多功能芯

片的第一输出端口rfout1。而对于第二移相器、第三移相器和第四移相器中设置移相功能模块,移相功能模块的输入端in和移相功能模块的输出端out的连接关系同上原理,此处不再赘述。

[0099]

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1