回旋时间解交错电路及回旋时间解交错电路的操作方法与流程

1.本公开是有关于一种回旋时间解交错电路,特别是一种能够有效使用内存频宽的回旋时间解交错电路。

背景技术:

2.在高级电视系统委员会(advanced television systems committee,atsc)所制定的3.0版规范中,用以收发讯号的实体层会利用时间交错(time interleave)的机制增加讯号传输对于丛发错误(burst error)的抗性。图1是回旋时间交错器(convolution time interleaver,cti)t1及回旋时间解交错器(convolution time de-interleaver,ctdi)t2的示意图。

3.回旋时间交错器t1可包含切换电路sw1及sw2及(n-1)组移位暂存器sra1至sra(n-1),其中n为大于1的整数。每一组移位暂存器sra1至sra(n-1)可包含数量相异的移位暂存器以提供不同时间长度的延迟。切换电路sw1具有n个输出端oa1至oan,切换电路sw1的输出端oa2至oan分别耦接至(n-1)组移位暂存器sra1至sra(n-1)中对应的一组移位暂存器。切换电路sw2具有n个输入端ia1至ian,切换电路sw2的输入端ia2至ian分别耦接至(n-1)组移位暂存器sra1至sra(n-1)中对应的一组移位暂存器,而切换电路sw2的输入端ia1则会耦接至切换电路sw1的输出端oa1。

4.回旋时间交错器t1在传输连续数据时,切换电路sw1会依序经由输出端oa1至oan将数据传出,而切换电路sw2则会依序经由输入端ia1至ian接收数据并将接收到的数据输出至外部的传输通道ch1。由于(n-1)组移位暂存器sra1至sra(n-1)可以提供不同时间长度的延迟,因此连续数据的传输顺序会被打散而与其他的数据交错传输。如此一来,在传输通道中发生丛发错误时,也不至于使整段连续数据都发生错误,而仍可透过自动纠错的机制得出正确的数据。

5.回旋时间解交错器t2可包含切换电路sw3及sw4及(n-1)组移位暂存器srb1至srb(n-1)。每一组移位暂存器srb1至srb(n-1)可包含数量相异的移位暂存器以提供不同时间长度的延迟。切换电路sw3具有n个输出端ob1至obn,切换电路sw3的输出端ob1至ob(n-1)分别耦接至(n-1)组移位暂存器srb1至srb(n-1)中对应的一组移位暂存器。切换电路sw4具有n个输入端ib1至ibn,切换电路sw4的输入端ib1至ib(n-1)分别耦接至(n-1)组移位暂存器srb1至srb(n-1)中对应的一组移位暂存器,而切换电路sw4的输入端ibn则会耦接至切换电路sw3的输出端obn。

6.回旋时间解交错器t2在接收到通道ch1所传来的数据时,切换电路sw3会依序经由输出端ob1至obn将数据传至(n-1)组移位暂存器srb1至srb(n-1)及切换电路sw4的输入端ibn,而切换电路sw4则会依序经由输入端ib1至ibn接收数据并输出。由于(n-1)组移位暂存器srb1至srb(n-1)可以提供不同时间长度的延迟,因此回旋时间解交错器t2可将原先被回旋时间交错器t1改变传输顺序的数据回复到原来的连续次序。

7.然而,回旋时间交错器t1及回旋时间解交错器t2中的移位暂存器sra1至sra(n-1)

及移位暂存器srb1至srb(n-1)需占用大量的电路面积及较高的硬体成本。此外,在回旋时间解交错器t2中,若欲利用硬体使用效率较佳且成本较低的内存来取代移位暂存器,则又会因为写入内存地址不连续而导致内存的频宽被浪费,甚至延长每笔数据输出所需的时间,造成系统效率低落的问题。

技术实现要素:

8.本发明的一实施例提供一种回旋时间解交错电路。回旋时间解交错电路包含输出缓冲电路、输入缓冲电路、内存、输入控制单元、输出控制单元及控制器。

9.该输出缓冲电路包含h个第一输出暂存单元组,每一组第一输出暂存单元包含w个第一输出暂存单元,其中h及w为大于1的整数。该输入缓冲电路包含与该h个第一输出暂存单元组相对应的h个第一输入暂存单元组,其中第h个第一输入暂存单元组的第一输入暂存单元的数量为w与h的和减去h的数值,且h为小于或等于h的正整数。该内存包含k个第一内存区块,每一第一内存区块包含与该h个第一输出暂存单元组及h个第一输入暂存单元组相对应的h个第一内存单元组,及每一第一内存单元组包含w个第一内存单元,其中k为正整数。该输入控制单元用以将h笔输入数据依序对应地写入该h个第一输入暂存单元组。该输出控制单元用以依序将该h个第一输出暂存单元组中所储存的h笔输出数据输出。该控制器用以在每w次对该h个第一输入暂存单元组各写入一笔输入数据后,将每一第一输入暂存单元组中最久未被写入的w个第一输入暂存单元所储存的数据写入具有一优先写入顺序的一第一内存区块中对应的一第一输入暂存单元组,及在对该k个第一内存区块分别写入w乘以h笔数据后,将具有一优先读出顺序的一第一内存区块中所储存的数据写入该输出缓冲电路的该h个第一输出暂存单元组。

10.其中每一第一输出暂存单元、每一第一输入暂存单元及每一第一内存单元皆具有相同的一位元容量,及每一第一内存区块的位元容量为该内存的单笔读写频宽的整数倍。

11.本发明的另一实施例提供一种回旋时间解交错电路的操作方法。该回旋时间解交错电路包含一输出缓冲电路、一输入缓冲电路及一内存,该输出缓冲电路包含h个第一输出暂存单元组,每一第一输出暂存单元组包含w个第一输出暂存单元,该输入缓冲电路包含与该h个第一输出暂存单元组相对应的h个第一输入暂存单元组,第h个第一输入暂存单元组的第一输入暂存单元的数量为w与h的和减去h的数值,该内存包含k个第一内存区块,每一第一内存区块包含与该h个第一输出暂存单元组及h个第一输入暂存单元组相对应的h个第一内存单元组,及每一第一内存单元组包含w个第一内存单元,其中每一第一输出暂存单元、每一第一输入暂存单元及每一第一内存单元皆具有相同的一位元容量,每一第一内存区块的位元容量为该内存的单笔读写频宽的整数倍,h及w为大于1的整数,k为正整数,及h为小于或等于h的正整数。

12.该方法包含将h笔输入数据依序对应地写入该h个第一输入暂存单元组,在将该h笔输入数据依序对应地写入该h个第一输入暂存单元组的同时,依序将该h个第一输出暂存单元组中所储存的h笔输出数据输出,在每w次对该h个第一输入暂存单元组各写入一笔输入数据后,将每一第一输入暂存单元组中最久未被写入的w个第一输入暂存单元所储存的数据写入具有一优先写入顺序的一第一内存区块中对应的一第一输入暂存单元组,及在对该k个第一内存区块分别写入w乘以h笔数据后,将具有一优先读出顺序的一第一内存区块

中所储存的数据写入该输出缓冲电路的该h个第一输出暂存单元组。

附图说明

13.图1是回旋时间交错器及回旋时间解交错器的示意图。

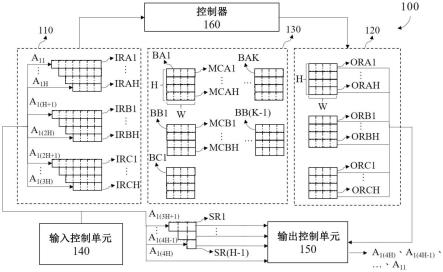

14.图2是本发明一实施例的回旋时间解交错电路的示意图。

15.图3是本发明一实施例的操作回旋时间解交错电路的方法的流程图。

16.图4至图8为图1的回旋时间解交错电路在不同阶段下搬迁数据的示意图。

具体实施方式

17.图2是本发明一实施例的回旋时间解交错电路100的示意图。回旋时间解交错电路100包含输入缓冲电路110、输出缓冲电路120、内存130、输入控制单元140、输出控制单元150及控制器160。

18.输入缓冲电路110可包含h个输入暂存单元组,包含第一输入暂存单元组ira1至irah,其中h为大于1的整数,且h个第一输入暂存单元组ira1至irah可分别包含不同数量的第一输入暂存单元以提供不同的延迟长度。举例来说,第h个第一输入暂存单元组的第一输入暂存单元的数量可以是w与h的和减去h的数值,其中h及w为大于1的整数,而h为小于或等于h的正整数。在图2中,h及w皆为4,在此情况下,第一个第一输入暂存单元组ira1可包含7个输入暂存单元,第二个第一输入暂存单元组ira2可包含6个输入暂存单元,而第三个第一输入暂存单元组irah可包含4个输入暂存单元。

19.输出缓冲电路120可包含与h个第一输入暂存单元组ira1至irah相对应的h个第一输出暂存单元组,包含第一输出暂存单元组ora1至orah,每一组第一输出暂存单元组ora1至orah可包含w个第一输出暂存单元。内存130可包含k个第一内存区块ba1至bak,其中k为正整数,在本实施例中,k为3。每一第一内存区块ba1至bak可包含与h个第一输入暂存单元组ira1至irah及h个第一输出暂存单元组ora1至orah相对应的h个第一内存单元组,包含第一内存单元组mca1至mcah,而每一第一内存单元组mca1至mcah可包含w个第一内存单元。

20.在本实施例中,每一第一输出暂存单元、每一第一输入暂存单元及每一第一内存单元可皆具有相同的位元容量,例如但不限于32位元。此外,每一第一内存区块ba1至bak的位元容量可以是内存130的单笔读写频宽的整数倍,以确保每次在对第一内存区块ba1至bak进行写入或读取时,能够有效地使用到内存130的全部频宽。举例来说,在本实施例中,内存130的单笔读写频宽为256位元,在h及w皆为4的情况下,第一内存区块ba1的总位元容量为512位元,即为内存130的单笔读写频宽的两倍。

21.在本实施例中,内存130可以是双倍数据率同步动态随机存取内存(double data rate synchronous dynamic random access memory,ddr sdram),且每一第一内存区块ba1至bak中的h个第一内存单元组可具有连续的地址。因此,回旋时间解交错电路100可以利用h个第一输入暂存单元组ira1至irah先暂存一定数量的数据之后,再一次对第一内存区块ba1至bak中对应的第一内存区块写入多笔数据,如此一来,就可以较为有效地利用内存130的读写频宽,而不会频繁地对内存130进行单一笔数据的写入操作而造成频宽的浪费。此外,在有些实施例中,内存130可能还包含更多数量的内存单元并可供系统中的其他电路使用,在此情况下,由于回旋时间解交错电路100可以一次连续写入多笔数据,因此也

可以避免内存130被回旋时间解交错电路100频繁的占用,而耽误其他电路的操作。

22.在有些实施例中,为了确保回旋时间解交错电路100能够较有效率地将数据从h个第一输入暂存单元组ira1至irah中搬移到第一内存区块ba1至bak,设计者可以先依据内存130的读写频宽来决定h及w的数值以设定第一内存区块ba1至bak的大小,并对应地决定输入缓冲电路110及输出缓冲电路120中暂存单元的数量。

23.此外,在本实施例中,h个第一输出暂存单元组ora1至orah的总位元容量可与每一第一内存区块ba1至bak的总位元容量相同,例如皆为w

×h×

32个位元。因此,当内存130中的k个第一内存区块ba1至bak都被写入数据时,便可将其中最久未被写入数据的第一内存区块的数据一起读出,并存入h个第一输出暂存单元组ora1至orah中。如此一来,就可以避免频繁地对内存130进行单一笔数据的读取操作而造成频宽的浪费。

24.图3是本发明一实施例的操作回旋时间解交错电路100的方法200的流程图。方法200可包含步骤s210至s240。

25.s210:将输入数据依序对应地写入h个第一输入暂存单元组ira1至irah;

26.s220:依序将h个第一输出暂存单元组ora1至orah中所储存的h笔输出数据输出;

27.s230:在每w次对h个第一输入暂存单元组ira1至irah各写入一笔输入数据后,将每一第一输入暂存单元组中最久未被写入的w个第一输入暂存单元所储存的数据写入具有优先写入顺序的第一内存区块中对应的一第一输入暂存单元组;及

28.s240:在对k个第一内存区块ba1至bak分别都写入w乘以h笔数据后,将具有优先读出顺序的第一内存区块中所储存的数据写入输出缓冲电路120的h个第一输出暂存单元组ora1至orah。

29.在步骤s210中,输入控制单元140可将h笔连续的输入数据a

11

至a

1h

依序且对应地写入h个第一输入暂存单元组ira1至irah中。此外,在将h笔输入数据a

11

至a

1h

依序写入h个第一输入暂存单元组ira1至irah的同时,输出控制单元150也同步执行步骤s220。在步骤s220中,输出控制单元150可依序将h个第一输出暂存单元组ora1至orah中所储存的h笔输出数据输出。

30.图4至图8为回旋时间解交错电路100在不同阶段下搬迁数据的示意图,为方便说明,在图4至图8中,h及w皆为4,且k为3,然而在本发明的其他实施例中,h及w也可以是大于1的其他整数,而k也可以是其他正整数。在图4中,h个第一输出暂存单元组ira1至irah已依序分别被写入了w笔输入数据a

11

至a

w1

、a

12

至a

w2

、a

13

至a

w3

及a

1h

至a

wh

。也就是说,在h个第一输出暂存单元组ira1至irah中已存入了相当于一个第一内存区块ba1所能够容纳的数据量,此时,控制器160可以执行步骤s230以将每一第一输入暂存单元组ira1至irah中最久未被写入的w个第一输入暂存单元所储存的数据写入具有优先写入顺序的第一内存区块中对应的一第一输入暂存单元组。在有些实施例中,第一内存区块ba1至bak中最久未被写入的一第一内存区块可具有优先写入顺序,然而在第一内存区块ba1至bak皆尚未被写入的情况下,也可依据系统预定的顺序来决定第一内存区块ba1至bak中何者具有优先写入顺序。在图5中,第一内存区块bak可具有优先写入顺序,因此控制器160会将每一第一输入暂存单元组ira1至irah中最久未被写入的w个第一输入暂存单元所储存的数据写入第一内存区块bak中。

31.此外,在图5中,输入控制单元140可记录h个第一输入暂存单元组ira1至irah中每

一个输入暂存单元的地址及被写入数据的先后顺序,因此当输入控制单元140接收到输入数据b

11

至b

w1

、b

12

至b

w2

、b

13

至b

w3

及b

1h

至b

wh

时,可将输入数据b

11

至b

w1

、b

12

至b

w2

、b

13

至b

w3

及b

1h

至b

wh

依序写入至h个第一输入暂存单元组ira1至irah中最久未被写入的w个输入暂存单元。此时,控制器160会再次执行步骤s230以将每一第一输入暂存单元组ira1至irah中最久未被写入的w个第一输入暂存单元所储存的数据写入具有优先写入顺序的第一内存区块中对应的一第一输入暂存单元组。在此情况下,若第一内存区块ba2具有优先写入顺序,则在图5中四个第一输入暂存单元组ira1至irah中最久未被写入的w个第一输入暂存单元所储存的数据将会在图6中被写入第一内存区块ba2。

32.此外,在图6中,输入控制单元140也已依序将输入数据c

11

至c

w1

、c

12

至c

w2

、c

13

至c

w3

及c

1h

至c

wh

写入至h个第一输入暂存单元组ira1至irah中最久未被写入的w个输入暂存单元。此时,控制器160会再次执行步骤s230以将每一第一输入暂存单元组ira1至irah中最久未被写入的w个第一输入暂存单元所储存的数据写入具有优先写入顺序的第一内存区块中对应的一第一输入暂存单元组。此时,由于第一内存区块ba1是最久未被写入的第一内存区块,因此会具有优先写入顺序,因此在图6中四个第一输入暂存单元组ira1至irah中最久未被写入的w个第一输入暂存单元所储存的数据会在图7中被写入第一内存区块ba1。再者,在图7中,由于第一内存区块ba1至bak都已各被写入了w乘以h笔数据,因此控制器160将会执行步骤s240,以将具有优先读出顺序的第一内存区块中所储存的数据写入输出缓冲电路120的h个第一输出暂存单元组ora1至orah。

33.在本实施例中,第一内存区块ba1至bak中最久未被写入的第一内存区块会具有优先读出顺序,因此在图8中,控制器160会将第一内存区块bak中所储存的数据写入至h个第一输出暂存单元组ora1至orah。在本实施例中,控制器160可以依据固定的顺序将数据写入至h个第一输出暂存单元组ora1至orah,而输出控制单元150也可依据固定的顺序将h个第一输出暂存单元组ora1至orah中的数据输出。在图8的实施例中,输出控制单元150将会依序输出数据a

1h

、a

13

、a

2h

、a

12

、a

23

、a

3h

、a

11

、a

22

、a

33

及a

wh

。

34.再者,在图7中,输入控制单元140已依序将输入数据d

11

至d

w1

、d

12

至d

w2

、d

13

至d

w3

及d

1h

至d

wh

写入至h个第一输入暂存单元组ira1至irah中最久未被写入的w个输入暂存单元,因此在图8中,控制器160还会再次执行步骤s230,并将每一第一输入暂存单元组ira1至irah中最久未被写入的w个第一输入暂存单元所储存的数据写入目前具有优先写入顺序的第一内存区块bak中对应的一第一输入暂存单元组。此外,在图8中,输入控制单元140也会依序将输入数据e

11

至e

w1

、e

12

至e

w2

、e

13

至e

w3

及e

1h

至e

wh

写入至h个第一输入暂存单元组ira1至irah中最久未被写入的w个输入暂存单元,并重复前述的步骤。

35.由于h个第一输入暂存单元组ira1至irah各包含了不同数量的输入暂存单元,因此被写入h个第一输入暂存单元组ira1至irah的数据将会在延迟不同的时间后才被输出。此外,虽然控制器160在将h个第一输入暂存单元组ira1至irah中部分数据写入第一内存区块ba1至bak的过程,并不会对回旋时间解交错电路100的数据输入及输出时序造成延迟,然而因为回旋时间解交错电路100会在第一内存区块ba1至bak都已被写入数据之后,才将最久未被写入的第一内存区块中的数据写入至h个第一输出暂存单元组ora1至orah,因此实际上第一内存区块ba1至bak的数量k也会影响到延迟时间的长短。举例来说,如果每次对h个第一输入暂存单元组ira1至irah各写入一笔数据可称为一个循环,则在w及h为4且k为3

的情况下,h个第一输入暂存单元组ira1至irah将可分别提供3至0个循环的延迟,而第一内存区块ba1至bak则可另外提供12个循环的延迟。也就是说,被写入第一输入暂存单元组ira1的输入数据a

11

将在第15个循环结束后,由输出切换电路150输出,而被写入第一输入暂存单元组ira2的输入数据a

12

将在第14个循环结束后,由输出切换电路150输出,并依次类推。

36.此外,在本实施例中,输入控制单元140是依据h个第一输入暂存单元ira1至irah的地址来对其中的输入暂存单元进行写入操作,因此本发明并不限定每一第一输入暂存单元组ira1至irah需以图4至图8所示的排列方式来储存数据。在有些其他实施例中,只要输入控制单元140能够纪录各个输入暂存单元的地址及其对应被写入的先后顺序,即可依据方法200来进行操作。相似地,控制器160也是依据第一内存区块ba1至bak的地址来对其中的内存单元进行写入操作,因此本发明并不限定每一第一内存区块ba1至bak需以图4至图8所示的排列方式来储存数据。在有些其他实施例中,只要输入控制单元140能够纪录各个内存单元的地址及其对应被写入的先后顺序,即可依据方法200来进行操作。

37.在图2中,输入缓冲电路110还可包含h个第二输入暂存单元组irb1至irbh,h个第二输入暂存单元组irb1至irbh的设置可与h个第一输入暂存单元组ira1至irah相同,举例来说,第h个第二输入暂存单元组irbh的第二输入暂存单元的数量会是w与h的和减去h的数值。此外,输出缓冲电路120还可包含与h个第二输入暂存单元组irb1至irbh的相对应的h个第二输出暂存单元组orb1至orbh,且每一组第二输出暂存单元orb1至orbh可包含w个第二输出暂存单元。再者,内存130还可包含(k-1)个第二内存区块bb1至bb(k-1),每一第二内存区块可包含与h个第二输入暂存单元组irb1至irbh及h个第二输出暂存单元组orb1至orbh相对应的h个第二内存单元组mcb1至mcbh,且每一第二内存单元组mcb1至mcbh可包含w个第二内存单元。

38.在此情况下,方法200还可在对h个第一输入暂存单元组ira1至irah写入h笔输入数据a

11

至a

1h

之后,利用输入切换电路140将另外h笔输入数据a

1(h+1)

至a

1(2h)

依序对应地写入h个第二输入暂存单元组irb1至irbh,并且可以在输出h个第一输出暂存单元组ora1至orah中所储存的h笔输出数据之后,利用输出切换电路150依序将h个第二输出暂存单元组orb1至orbh中所储存的h笔输出数据输出。

39.此外,方法200还可在每w次对h个第二输入暂存单元组irb1至irbh各写入一笔输入数据后,利用控制器160将每一第二输入暂存单元组irb1至irbh中最久未被写入的w个第二输入暂存单元所储存的数据写入(k-1)个第二内存区块bb1至bb(k-1)中最久未被写入的第二内存区块中对应的一第二内存单元组,并在对(k-1)个第二内存区块bb1至bb(k-1)分别写入w乘以h笔数据后,将(k-1)个第二内存区块中最久未被写入的一第二内存区块中所储存的数据写入输出缓冲电路120的h个第二输出暂存单元组orb1至orbh。

40.如此一来,h个第二输入暂存单元组irb1至irbh、(k-1)个第二内存区块bb1至bb(k-1)及h个第二输出暂存单元组orb1至orbh也可以提供不同长度的时间延迟。举例来说,被写入h个第一输入暂存单元组ira1至irah的输入数据a

11

至a

1h

将分别在延迟15、14、13及12个循环后,由输出切换电路150输出,而被写入h个第二输入暂存单元组irb1至irbh的输入数据a

1(h+1)

至a

1(2h)

将分别在延迟11、10、9及8个循环后,由输出切换电路150输出。也就是说,回旋时间解交错电路100可以依据系统需求的延迟时间,使输入缓冲电路110包含更多

的h个输入暂存单元组,并使内存130包含对应的内存区块,及使输出缓冲电路120包含对应的输出暂存单元,以提供对应的延迟效果。举例来说,输入缓冲电路110还可包含h个第三输入暂存单元组irc1至irch,输出缓冲电路120还可包含与h个第三输入暂存单元组irc1至irch的相对应的h个第三输出暂存单元组orc1至orch,且内存130还可包含一个第三内存区块bc1。在此情况下,被写入h个第三输入暂存单元组irc1至irch的输入数据a

1(2h+1)

至a

1(3h)

将分别在延迟7、6、5及4个循环后,由输出切换电路150输出

41.再者,在图2的实施例中,回旋时间解交错电路100还可包含(h-1)个移位暂存单元组sr1至sr(h-1),每一移位暂存单元组sr1至sr(h-1)可以包含不同数量的移位暂存单元,以提供不同长度的时间延迟。举例来说,第i个移位暂存单元组可包含(h-i)个移位暂存单元,其中i为等于或小于(h-1)的正整数,且h为大于2的整数。在h为4的情况下,第一个移位暂存单元组sr1可包含3个移位暂存单元,第二个移位暂存单元组sr2可包含2个移位暂存单元,而第(h-1)个移位暂存单元组sr(h-1)可包含1个移位暂存单元。

42.在此情况下,方法200可以在对h个第三输入暂存单元组irc1至irch各写入一笔输入数据之后,将另外(h-1)笔输入数据a

1(3h+1)

至a

1(4h-1)

依序对应地写入(h-1)个移位暂存单元组sr1至sr(h-1)中的(h-1)个首位移位暂存单元,并在输出h个第三输出暂存单元组orc至orch所储存的h笔数据之后,依序将(h-1)个移位暂存单元组sr1至sr(h-1)中的(h-1)个末位移位暂存单元中所储存的(h-1)笔输出数据输出。接着,在对(h-1)个首位移位暂存单元写入(h-1)笔输入数据a

1(3h+1)

至a

1(4h-1)

,并将(h-1)个末位移位暂存单元中所储存的(h-1)笔输出数据输出后,输入控制单元140可将一笔输入数据a

1(4h)

直接传送至输出控制单元150以无延迟的方式输出。也就是说,被写入(h-1)个移位暂存单元组sr1至sr(h-1)的输入数据a

1(3h+1)

至a

1(4h-1)

将分别在延迟3、2及1个循环后,由输出切换电路150输出,且输入数据a

1(4h)

将在没有被延迟的情况下直接通过输入控制单元140及输出控制单元150而被输出。

43.如同前述的说明,在h及w为4且k为3的情况下,图2中的回旋时间解交错电路100可以提供16种不同的延迟来对输入数据进行解交错的操作。然而,在其他实施例中,使用者也可依据实际的需求,选择h、w及k的适当数值,以提供系统所需的延迟效果。

44.综上所述,本发明的实施例所提供的回旋时间解交错电路及操作回旋时间解交错电路的方法可以利用硬体使用效率较佳且成本较低的内存来储存数据以提供每笔数据所需的延迟时间,并且可以利用输入暂存单元先暂存一定数量的数据之后,再一次对内存中对应的内存区块写入多笔数据。因此,本发明的实施例所提供的回旋时间解交错电路及操作回旋时间解交错电路可以较有效地利用内存的读写频宽,而不会频繁地对内存进行单一笔数据的写入操作而造成频宽的浪费。

45.【符号说明】

46.t1:回旋时间交错电路

47.t2、100:回旋时间解交错电路

48.sw1、sw2、sw3、sw4:切换电路

49.oa1至oan、ob1至obn:输出端

50.ia1至ian、ib1至ibn:输入端

51.sra1至sra(n-1)、srb1至srb(n-1)、sr1至sr(h-1):移位暂存器组

52.ch1:通道

53.110:输入缓冲电路

54.120:输出缓冲电路

55.130:内存

56.140:输入控制单元

57.150:输出控制单元

58.160:控制器

59.ira1至irah、irb1至irbh、irc1至irch:输入暂存单元组

60.ora1至orah、orb1至orbh、orc1至orch:输出暂存单元组

61.ba1至bak、bb1至bb(k-1)、bc1:内存区块

62.mca1至mcah、mcb1至mcbh:内存单元组

63.a

1(h+1)

、a

1(2h)

、a

1(2h+1)

、a

1(3h)

、a

1(3h+1)

、a

1(4h-1)

、a

1(4h)

、a

21

、a

31

、a

w1

、a

11

、a

21

、a

31

、a

w1

、a

12

、a

22

、a

32

、a

w2

、a

13

、a

23

、a

33

、a

w3

、a

1h

、a

2h

、a

3h

、a

wh

、b

11

至b

wh

、c

11

至c

wh

、d

11

至d

wh

、e

11

至e

wh

:数据

64.200:方法

65.s210至s240:步骤。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1