一种判决反馈均衡器

1.本发明涉及微电子技术领域,更为具体地说,涉及一种判决反馈均衡器。

背景技术:

2.随着串口数据率达到56gbs乃至112gbs时,传统的nrz方式由于信道损耗过大,并且普通的均衡方式对于恢复信号越发的困难。对此,pam4方式开始取代nrz成为了主流的编码方式。pam4同样带来了巨大的挑战,首先便是高频,高速的码率对于传统的模拟均衡方式是一个巨大的挑战,因此adc+dsp的均衡方案开始应运而出。而判决反馈均衡器(decision feedback equalizers,dfe)是serdes接收器中的dsp中用来补偿符号间干扰(inter symbol interference,isi)的常见的均衡器。现有的判决反馈均衡器有待改进。

技术实现要素:

3.有鉴于此,本发明提供了一种判决反馈均衡器,有效解决了现有技术存在的技术问题,提高了判决反馈均衡器的运行频率,降低了其功耗。

4.为实现上述目的,本发明提供的技术方案如下:

5.一种判决反馈均衡器,包括:第一支路至第n支路,第j支路接入第j输入数据,n为大于或等于2的整数,j为大于0且小于或等于n的整数,所述第j支路包括:

6.抽头系数元件,所述抽头系数元件用于调取1-tap的抽头系数,且将所述抽头系数分别与pam4信号的第一电平数据至第四电平数据相乘后,输出第一结果至第四结果,其中,所述抽头系数与第i电平数据相乘得到第i结果,i为大于或等于1且小于或等于4的整数;

7.求和元件,所述求和元件用于将所述第j输入数据与所述第i结果求和后,输出第i求和结果;

8.判决元件,所述判决元件用于对所述第i求和结果进行判决后,输出第i判决结果;

9.四选一多路复用器,所述第k支路的四选一多路复用器用于根据第k+1支路的四选一多路复用器的输出,自所述第k支路的第一判决结果至第四判决结果中选择目标判决结果输出,其中,第n支路的四选一多路复用器用于根据第一支路的四选一多路复用器的输出,自所述第n支路的第一判决结果至第四判决结果中选择目标判决结果输出,k为大于或等于1且小于n的整数。

10.可选的,包括:第一寄存器,所述第一寄存器用于存储1-tap的所述抽头系数,且所述抽头系数元件自所述第一寄存器调取所述抽头系数。

11.可选的,包括:第二寄存器,所述第二寄存器用于存储所述求和元件输出的所述第i求和结果,且所述判决元件自所述第二寄存器获取所述第i求和结果。

12.可选的,包括:第三寄存器,所述第三寄存器用于存储所述判决元件输出的所述第i判决结果,且所述四选一多路复用器自所述第三寄存器获取所述第i判决结果。

13.可选的,包括:第四寄存器,所述第四寄存器用存储所述四选一多路复用器输出的所述目标判决结果。

14.可选的,n为32。

15.可选的,所述判决元件参考所述pam4信号的眼图中至少一个周期时间内三个眼睛各自相应平均值,对所述第i求和结果进行判决后输出所述第i判决结果。

16.可选的,所述判决元件根据以下公式对相应求和结果进行判决后输出相应判决结果:

17.第一判决结果=2*下均值-第二判决结果;

18.所述第二判决结果=(下均值+中间均值)/2;

19.第三判决结果=(上均值+中间均值)/2;

20.第四判决结果=2*上均值-所述第三判决结果;

21.其中,所述上均值为所述pam4信号的眼图中上眼睛相应平均值,所述中间均值为所述pam4信号的眼图中中间眼睛相应平均值,所述下均值为所述pam4信号的眼图中下眼睛相应平均值。

22.可选的,所述中间均值的获取过程包括:将所述第j数据经过第j积分器处理后得到第j初始中间值;对第一初始中间值至第n初始中间值进行求和求平均后得到所述中间均值;

23.所述上均值的获取过程包括:判断出所述第j数据大于或等于所述中间均值时,将所述第j数据经过所述第j积分器处理后得到第j初始上值;对所有初始上值进行求和求平均后得到所述上均值;

24.所述下均值的获取过程包括:判断出所述第j数据小于所述中间均值时,将所述第j数据经过所述第j积分器处理后得到第j初始下值;对所有初始下值进行求和求平均后得到所述下均值。

25.可选的,所述第j积分器包括:加法器、触发器、第一乘法器和第二乘法器;

26.所述加法器的第一输入端接入所述第j输入数据,所述加法器的第二输入端接入所述第二乘法器的输出端;

27.所述触发器的第一输入端接入所述加法器的输出端,所述触发器的第二输入端接入所述触发器的输出端,所述第二乘法器的输入端接入所述触发器的输出端,所述触发器用于将所述加法器的输出信号和所述触发器的输出信号相加并延迟一个码元输出;

28.所述第一乘法器的输入端接入所述触发器的输出端,所述第一乘法器的输出端为所述第j积分器的输出端,所述第一乘法器和所述第二乘法器用于调整接入信号的带宽。

29.相较于现有技术,本发明提供的技术方案至少具有以下优点:

30.本发明提供了一种判决反馈均衡器,包括:第一支路至第n支路,第j支路接入第j输入数据,n为大于或等于2的整数,j为大于0且小于或等于n的整数,所述第j支路包括:抽头系数元件,所述抽头系数元件用于调取1-tap的抽头系数,且将所述抽头系数分别与pam4信号的第一电平数据至第四电平数据相乘后,输出第一结果至第四结果,其中,所述抽头系数与第i电平数据相乘得到第i结果,i为大于或等于1且小于或等于4的整数;求和元件,所述求和元件用于将所述第j输入数据与所述第i结果求和后,输出第i求和结果;判决元件,所述判决元件用于对所述第i求和结果进行判决后,输出第i判决结果;四选一多路复用器,所述第k支路的四选一多路复用器用于根据第k+1支路的四选一多路复用器的输出,自所述第k支路的第一判决结果至第四判决结果中选择目标判决结果输出,其中,第n支路的四选

一多路复用器用于根据第一支路的四选一多路复用器的输出,自所述第n支路的第一判决结果至第四判决结果中选择目标判决结果输出,k为大于或等于1且小于n的整数。

31.由上述内容可知,本发明提供的技术方案,通过抽头系数元件预先计算出四个可能输出的结果,而后通过处理判决后由四选一多路复用器输出最终的目标判决结果,进而提高了判决反馈均衡器的运行频率,降低了其功耗。

附图说明

32.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

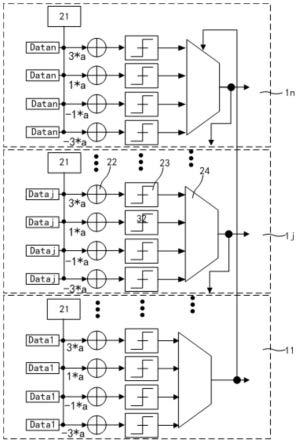

33.图1为本发明实施例提供的一种判决反馈均衡器的结构示意图;

34.图2为本发明实施例提供的另一种判决反馈均衡器的结构示意图;

35.图3为本发明实施例提供的一种pam4信号的眼图;

36.图4为本发明实施例提供的一种中间均值的求取过程框图;

37.图5为本发明实施例提供的一种上均值和下均值的求取过程框图;

38.图6为本发明实施例提供的一种积分器的结构示意图。

具体实施方式

39.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

40.正如背景技术所述,随着串口数据率达到56gbs乃至112gbs时,传统的nrz方式由于信道损耗过大,并且普通的均衡方式对于恢复信号越发的困难。对此,pam4方式开始取代nrz成为了主流的编码方式。pam4同样带来了巨大的挑战,首先便是高频,高速的码率对于传统的模拟均衡方式是一个巨大的挑战,因此adc+dsp的均衡方案开始应运而出。而判决反馈均衡器(decision feedback equalizers,dfe)是serdes接收器中的dsp中用来补偿符号间干扰(inter symbol interference,isi)的常见的均衡器。现有的判决反馈均衡器有待改进。

41.基于此,本发明实施例提供了一种判决反馈均衡器,有效解决了现有技术存在的技术问题,提高了判决反馈均衡器的运行频率,降低了其功耗。

42.为实现上述目的,本发明实施例提供的技术方案如下,具体结合图1至图6对本发明实施例提供的技术方案进行详细的描述。

43.如图1所示,为本发明实施例提供的一种判决反馈均衡器的结构示意图,其中,判决反馈均衡器包括:第一支路11至第n支路1n,第j支路1j接入第j输入数据dataj,n为大于或等于2的整数,j为大于0且小于或等于n的整数,所述第j支路1j包括:

44.抽头系数元件21,所述抽头系数元件21用于调取1-tap的抽头系数a,且将所述抽头系数a分别与pam4信号的第一电平数据至第四电平数据相乘后,输出第一结果至第四结

果,其中,所述抽头系数a与第i电平数据相乘得到第i结果,i为大于或等于1且小于或等于4的整数;及所述第一电平数据为-3,所述第二电平数据为-1,所述第三电平数据为1,所述第四电平数据为3。

45.求和元件22,所述求和元件22用于将所述第j输入数据dataj与所述第i结果求和后,输出第i求和结果。

46.判决元件23,所述判决元件23用于对所述第i求和结果进行判决后,输出第i判决结果。

47.四选一多路复用器24,所述第k支路的四选一多路复用器24用于根据第k+1支路的四选一多路复用器24的输出,自所述第k支路的第一判决结果至第四判决结果中选择目标判决结果输出,其中,第n支路1n的四选一多路复用器24用于根据第一支路11的四选一多路复用器24的输出,自所述第n支路1n的第一判决结果至第四判决结果中选择目标判决结果输出,k为大于或等于1且小于n的整数。

48.可以理解的,本发明实施例提供的第一支路至第n支路是并行的支路,且第j支路中包括有四个并行的接入端口分别接入第j输入数据,以分别与相应的结果进行求和处理。在本发明一实施例中,本发明提供的n为32,即本发明实施例提供的判决反馈均衡器可以为并行32路的判决反馈均衡器。

49.由上述内容可知,本发明实施例提供的技术方案,通过抽头系数元件预先计算出四个可能输出的结果,而后通过处理判决后由四选一多路复用器输出最终的目标判决结果,进而提高了判决反馈均衡器的运行频率,降低了其功耗。

50.如图2所示,为本发明实施例提供的另一种判决反馈均衡器的结构示意图,本发明提供的判决反馈均衡器包括:第一寄存器31,所述第一寄存器31用于存储1-tap的所述抽头系数,且所述抽头系数元件21自所述第一寄存器31调取所述抽头系数。

51.和/或,如图2所示,判决反馈均衡器包括:第二寄存器32,所述第二寄存器32用于存储所述求和元件22输出的所述第i求和结果,且所述判决元件23自所述第二寄存器32获取所述第i求和结果。

52.和/或,如图2所示,判决反馈均衡器包括:第三寄存器33,所述第三寄存器33用于存储所述判决元件23输出的所述第i判决结果,且所述四选一多路复用器24自所述第三寄存器33获取所述第i判决结果。

53.和/或,如图2所示,判决反馈均衡器包括:第四寄存器34,所述第四寄存器34用存储所述四选一多路复用器24输出的所述目标判决结果。

54.可以理解的,本发明实施例提供的判决反馈均衡器采用寄存器实现流水线式结构,进而能够进一步的加快判决反馈均衡器的运行频率,使得整个系统的运行速度大幅度改善。可选的,本发明实施例提供的第一寄存器、第二寄存器、第三寄存器和第四寄存器可以为独立的寄存器,还可以为同一个寄存器,对此本发明不做具体限制。

55.在本发明一实施例中,本发明提供的所述判决元件参考所述pam4信号的眼图中至少一个周期时间内三个眼睛各自相应平均值,对所述第i求和结果进行判决后输出所述第i判决结果。如图3所示,为本发明实施例提供的一种pam4信号的眼图,其中,横坐标为时间time,纵坐标为振幅real amplitude。可见,由于pam4信号的四个电平数据,故而每一时刻都会有三个眼睛和四个电平。其中,判决元件根据眼图中每个眼睛的最中间的平均值进行

判决,从而得到四个电平数据各自对应的理想值(理想值即判决结果)输出。

56.在本发明一实施例中,本发明提供的所述判决元件根据以下公式对相应求和结果进行判决后输出相应判决结果:

57.第一判决结果=2*下均值-第二判决结果;

58.所述第二判决结果=(下均值+中间均值)/2;

59.第三判决结果=(上均值+中间均值)/2;

60.第四判决结果=2*上均值-所述第三判决结果;

61.其中,所述上均值为所述pam4信号的眼图中上眼睛相应平均值,所述中间均值为所述pam4信号的眼图中中间眼睛相应平均值,所述下均值为所述pam4信号的眼图中下眼睛相应平均值。

62.如图4所示,为本发明实施例提供的一种中间均值的求取过程框图,其中,所述中间均值mid的获取过程包括:将所述第j数据dataj经过第j积分器4j处理后得到第j初始中间值midj;对第一初始中间值mid1至第n初始中间值midn进行求和求平均后得到所述中间均值mid。

63.如图5所示,为本发明实施例提供的一种上均值和下均值的求取过程框图,所述上均值up的获取过程包括:判断出所述第j数据dataj大于或等于所述中间均值mid时,将所述第j数据dataj经过所述第j积分器4j处理后得到第j初始上值upj;对所有初始上值进行求和求平均后得到所述上均值up。

64.以及,所述下均值down的获取过程包括:判断出所述第j数据dataj小于所述中间均值mid时,将所述第j数据dataj经过所述第j积分器4j处理后得到第j初始下值downj;对所有初始下值进行求和求平均后得到所述下均值down。

65.如图6所示,为本发明实施例提供的一种积分器的结构示意图,其中,积分器为数字一阶∑

△

积分器,本发明实施例提供的所述第j积分器包括:加法器401、触发器402、第一乘法器403和第二乘法器404。

66.所述加法器401的第一输入端接入所述第j输入数据dataj,所述加法器401的第二输入端接入所述第二乘法器404的输出端。

67.所述触发器402的第一输入端接入所述加法器401的输出端,所述触发器402的第二输入端接入所述触发器402的输出端,所述第二乘法器404的输入端接入所述触发器402的输出端,所述触发器402用于将所述加法器401的输出信号和所述触发器402的输出信号相加并延迟一个码元输出。

68.所述第一乘法器403的输入端接入所述触发器402的输出端,所述第一乘法器403的输出端为所述第j积分器的输出端,所述第一乘法器403和所述第二乘法器404用于调整接入信号的带宽,进而根据需要将输出的曲线改变的更加精准。

69.可以理解的,本发明实施例提供的积分器设计更加简单,并不会随着数据量的增加而扩大资源,其改变精度只需要通过乘法器调节带宽,进而无需增加滤波器的深度。

70.本发明实施例提供了一种判决反馈均衡器,包括:第一支路至第n支路,第j支路接入第j输入数据,n为大于或等于2的整数,j为大于0且小于或等于n的整数,所述第j支路包括:抽头系数元件,所述抽头系数元件用于调取1-tap的抽头系数,且将所述抽头系数分别与pam4信号的第一电平数据至第四电平数据相乘后,输出第一结果至第四结果,其中,所述

抽头系数与第i电平数据相乘得到第i结果,i为大于或等于1且小于或等于4的整数;求和元件,所述求和元件用于将所述第j输入数据与所述第i结果求和后,输出第i求和结果;判决元件,所述判决元件用于对所述第i求和结果进行判决后,输出第i判决结果;四选一多路复用器,所述第k支路的四选一多路复用器用于根据第k+1支路的四选一多路复用器的输出,自所述第k支路的第一判决结果至第四判决结果中选择目标判决结果输出,其中,第n支路的四选一多路复用器用于根据第一支路的四选一多路复用器的输出,自所述第n支路的第一判决结果至第四判决结果中选择目标判决结果输出,k为大于或等于1且小于n的整数。

71.由上述内容可知,本发明实施例提供的技术方案,通过抽头系数元件预先计算出四个可能输出的结果,而后通过处理判决后由四选一多路复用器输出最终的目标判决结果,进而提高了判决反馈均衡器的运行频率,降低了其功耗。

72.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1