数据通信设备的控制器和方法与流程

1.本公开涉及一种用于数据通信的技术,且更具体地,涉及一种用于以最佳频率和相位恢复脉冲振幅调制4(pulse-amplitude modulation 4;4-pam)数据和数据时钟的数据通信设备的控制器和方法。

背景技术:

2.最近,用于数据通信的技术遇到了创造具有更快数据速率的小型且紧凑的器件的挑战,因而,可满足用户对于高数据速率通信的需要,且因此可降低生产成本。这种情形的实例中的一个为自动化工厂的生产线,所述生产线利用需要被监测的极大量的器件。每一器件产生包含高质量图像和视频的大量数据。从多个器件收集的所有数据需要在相对相同的时间传输到控制中心,因而自动化工厂的管理者可确定生产线的当前状态。此外,由于管理者并不总是在生产场所待命,因此管理者可使用移动器件接收所有数据,以便能够监测生产线的当前状态。因此,极需创造能够接收极大量数据的紧凑器件。另外,具有高数据速率(即pam-4)的数据的传输可能产生一些干扰,例如符号间干扰(inter symbol interference;isi),因而,由接收器接收到的数据不能完美地恢复,且产生较高的比特误差率(bit error rate;ber)。此外,传输器通常传输大量数据,而不包含数据时钟。然而,为了产生具有小ber的恢复的数据,需要在频率和相位方面正确地恢复数据时钟。因此,应减少器件的电子电路以便压缩生产成本。

技术实现要素:

3.本公开提出包含用于数据通信系统的控制器的设备和方法。控制器(即,301)包含具有特定结构和顺序的多个单元以处理输入数据,以便产生具有最佳频率和相位的恢复的数据时钟和具有小ber的恢复的数据。控制器(即,301)包含包络检测器cdr 306以检测表示最佳的恢复的数据时钟的包络数据峰值,且包络检测器cdr还具有逻辑以在cdr ffe输出处计算

‘

pre_cursor-post_cursor’值,接着mm检测器cdr使用所述

‘

pre_cursor-post_cursor’值来锁定到此真实峰值相位且对其进行连续跟踪。因此,通过使用最佳的恢复的数据时钟,可产生具有小ber的恢复的数据。

4.根据一些实施例,数据通信设备的控制器配置成从通过模数转换器(adc)接收到的输入数据产生恢复的数据时钟和恢复的数据。控制器包含第一均衡器、第一多路复用器、第一检测器、第二检测器、第二多路复用器、数据时钟发生器以及第二均衡器。第一均衡器耦接到adc且配置成接收且均衡输入数据。第一多路复用器耦接到第一均衡器和adc。第一检测器耦接到第一均衡器且配置成检测最佳输入数据采样相位,其中最佳输入数据采样相位表示输入数据峰值。第二检测器耦接到第一多路复用器,且配置成根据输入数据产生包络数据且相对于输入数据采样相位检测包络峰值,其中包络峰值表示包络数据峰值。第二多路复用器耦接到第一检测器和第二检测器。数据时钟发生器耦接到多路复用器和adc且配置成产生恢复的数据时钟。第二均衡器耦接到adc且配置成产生恢复的数据。第二多路复

用器配置成在初始包络数据峰值检测期间选择第二检测器输出,且在第二检测器被锁定到最佳输入数据采样相位之后,第二多路复用器配置成选择第一检测器输出。

5.根据一些实施例,第二检测器包含绝对模块、平均模块、第一延迟模块、符号模块以及加法器。绝对模块耦接到adc且配置成产生对应于输入数据的绝对数据。平均模块耦接到绝对模块且配置成从绝对数据计算平均数据。第一延迟模块耦接到平均模块且配置成从平均数据产生第一延迟数据。符号模块耦接到第一延迟模块和平均模块且配置成检查平均数据相对于第一延迟数据是增加还是减少。加法器和第二延迟模块耦接到符号模块且配置成从平均数据检测平均数据峰值。平均数据和平均数据峰值分别表示包络数据和包络数据峰值。

6.在一些实施例中,adc以恢复的数据时钟的1

×

速率(每一符号一个样本)对输入数据进行采样。在一些实施例中,第二检测器确定第一检测器的最佳偏移。在一些实施例中,由第二检测器计算的最佳偏移被第一检测器使用,以使得其锁定到由第二检测器检测到的最佳输入数据采样相位。

7.在一些实施例中,第一检测器更包含时序误差检测器和滤波器模块。时序误差检测器耦接到第一均衡器,且配置成根据由第一均衡器均衡的输入数据来计算时序误差。滤波器模块耦接到时序误差检测器,且配置成通过使用二阶滤波器来对时序误差进行滤波。

8.在一些实施例中,由第一检测器检测到的输入数据峰值通过由第二检测器计算的最佳偏移(

‘

pre_cursor-post_cursor’值)来调节。在一些实施例中,输入数据为pam4。在一些实施例中,控制器实施用于56gbps serdes接收器或外围组件互连标准gen6接收器。

9.在一些实施例中,数据通信设备的控制器配置成通过模数转换器(adc)从输入数据产生恢复的数据时钟和恢复的数据。控制器包含第一均衡器、第一检测器、第一多路复用器、第二检测器、添加单元、第一数据时钟发生器、第二均衡器以及第三检测器。第一均衡器耦接到信号转换器电路且配置成均衡输入数据作为均衡数据。第一检测器耦接到第一均衡器且配置成从输入数据检测输入数据峰值。第一多路复用器耦接到第一均衡器和信号转换器电路。第二检测器耦接到第一多路复用器,且配置成从输入数据或均衡数据产生包络数据且从包络数据检测包络数据峰值。添加单元耦接到第二检测器和第三均衡器。第一数据时钟发生器耦接到添加单元和信号转换器电路,且配置成产生恢复的数据时钟。第二均衡器耦接到信号转换器电路且配置成产生恢复的数据。第三检测器耦接到信号转换器电路和添加单元,且配置成根据输入数据峰值产生数据相位代码或校正的输入数据峰值。加法器通过添加来自第二检测器和第三检测器的相位值来产生adc采样相位。此采样相位将锁定到包络数据峰值。

10.根据一些实施例,第三检测器更包含数据相位检测器、第二多路复用器、第三均衡器以及第二数据时钟发生器。数据相位检测器耦接到信号转换器电路,且配置成匹配输入数据采样相位和中间数据时钟。第二多路复用器耦接到第二检测器和第三检测器。第三均衡器耦接到第二多路复用器且配置成产生均衡数据。第二数据时钟发生器耦接到第三均衡器和第三检测器,且配置成产生中间数据时钟。

11.根据一些实施例,第二检测器包含绝对模块、平均模块、第一延迟模块、符号模块、加法器以及第二延迟模块。绝对模块耦接到信号转换器电路或第一多路复用器,且配置成从有符号的数据产生绝对数据。平均模块耦接到绝对模块且配置成从绝对数据计算平均数

据。第一延迟模块耦接到平均模块且配置成从平均数据产生第一延迟数据。符号模块耦接到第一延迟模块和平均模块且配置成检查平均数据相对于第一延迟数据是增加还是减少。加法器和第二延迟模块耦接到符号模块且配置成从平均数据检测平均数据峰值。平均数据和平均数据峰值分别表示包络数据和包络数据峰值。

12.根据一些实施例,平均模块配置成通过在n单位间隔ui内针对28gsps(56gbps pam4)的符号率对绝对数据求平均值来计算平均数据的一个数据样本。平均数据的一个数据样本表示包络数据的一个数据样本。根据一些实施例,通过28gsps/56gbps的更新速率来计算接下来的数据样本。56gbps表示每秒56千兆字节,且28gsps表示在pam4中编码的等效于56gbps的每秒28千兆符号。平均数据的接下来的数据样本表示包络数据的接下来的数据样本。

13.根据一些实施例,一种数据通信设备的方法包含以下步骤:均衡输入数据作为均衡数据;从输入数据检测输入数据峰值;从输入数据或均衡数据产生包络数据且从包络数据检测包络数据峰值;根据包络数据峰值和校正的输入数据峰值来产生偏移值;根据偏移值产生恢复的数据时钟;根据恢复的数据时钟产生恢复的数据;以及根据输入数据峰值产生校正的输入数据峰值;通过添加来自第二检测器和第三检测器的相位值来产生数据采样相位;以及将包络数据峰值锁定到采样相位,其中设备包含:接收器,配置成接收具有模拟数据形式的接收到的数据;以及信号转换器电路,配置成使用恢复的数据时钟将接收到的数据从模拟数据形式转换成数字数据形式。

14.根据一些实施例,根据输入数据峰值产生校正的输入数据峰值更包含以下步骤:根据输入数据和中间数据时钟来产生输入数据采样相位;根据输入数据峰值和输入数据采样相位来产生中间输入数据峰值;根据输入数据峰值和输入数据采样相位来产生校正的输入数据峰值;以及根据校正的输入数据峰值来产生中间数据时钟。

15.根据一些实施例,从输入数据或均衡数据产生包络数据和从包络数据检测包络数据峰值更包含以下步骤:从有符号的数据产生绝对数据;从绝对数据计算平均数据;从平均数据产生第一延迟数据;检查平均数据相对于第一延迟数据是增加还是减少;以及从平均数据检测平均数据峰值。平均数据和平均数据峰值分别表示包络数据和包络数据峰值。

附图说明

16.当结合随附图式阅读时,根据以下详细描述最佳地理解本公开的各方面。应注意,根据业界中的标准惯例,各种特征未按比例绘制。实际上,出于论述清楚起见,可任意增大或减小各种特征的尺寸。

17.图1示意性地示出根据本公开的实施例的数据通信系统的框图。

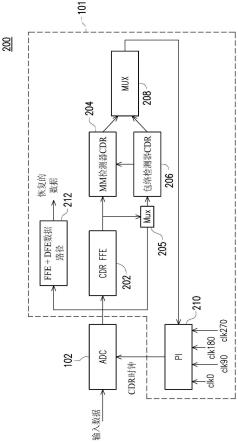

18.图2示意性地示出根据本公开的实施例的adc和包含多个单元的控制器的框图。

19.图3示意性地示出根据本公开的另一实施例的adc和包含多个单元的控制器的框图。

20.图4示意性地示出根据本公开的实施例的adc和包含多个模块的包络检测器cdr的框图。

21.图5示意性地示出根据本公开的实施例的由cn和ctle的组合所产生的脉冲响应的图表。

22.图6示意性地示出根据本公开的实施例的相对于ui两端的采样相位的信号分量和isi分量的曲线图。

23.图7示意性地示出根据本公开的实施例的控制器的启动顺序。

24.图8示意性地示出根据本公开的实施例的用于数据通信的设备的方法。

25.图9a至图9e示意性地示出根据本公开的实施例的控制器中的多个模块的启动的每一步骤。

26.图10示意性地示出根据本公开的实施例的mm检测器cdr的滤波器。

27.附图标号说明

28.100:数据通信系统;

29.101、200、300、301:控制器;

30.102:模数转换器;

31.103:连续时间线性均衡器;

32.103-1:模拟线性处理单元;

33.103-2:电压增益放大器;

34.104:接收器;

35.105:信道;

36.107:传输器;

37.202:时钟和数据恢复前馈均衡器;

38.204、304:米勒-穆勒检测器时钟和数据恢复;

39.205、208、308、314:多路复用器;

40.206、306:包络检测器时钟和数据恢复;

41.210、310、320:相位内插器;

42.212:前馈均衡器和判决反馈均衡器数据路径;

43.316:相位内插器滤波器;

44.318、412、1014:加法器;

45.322:继电器式相位检测器;

46.330:单元;

47.404:绝对模块;

48.406:平均模块;

49.408:第一延迟模块;

50.410:符号模块;

51.414:第二延迟模块;

52.1002:mm检测器;

53.1010:cdr滤波器;

54.1011:比例均衡器;

55.1012:第一积分均衡器;

56.1013:第一整合单元;

57.1015:第二积分均衡器;

58.1016:第二整合单元;

59.a:第一延迟数据;

60.b:平均数据;

61.clk、clkb:中间时钟;

62.clk0、clk90、clk180、clk270:相位;

63.s702、s703、s704、s705、s706、s707、s708、s709、s802、s803、s804、s805、s806:步骤。

具体实施方式

64.以下公开内容提供用于实施本公开的不同特征的许多不同实施例或实例。下文描述组件和布置的具体实例来简化本公开。当然,这些组件和布置仅为实例且并不意图为限制性的。举例来说,在以下描述中,第一特征在第二特征上方或上的形成可包含第一特征与第二特征直接接触地形成的实施例,且还可包含额外特征可在第一特征与第二特征之间形成以使得第一特征与第二特征可以不直接接触的实施例。另外,本公开可在各种实例中重复参考标号和/或字母。这种重复是出于简化和清楚的目的且本身并不指示所论述的各种实施例和/或配置之间的关系。

65.另外,例如“在

…

之下”、“在

…

下方”、“下部”、“在

…

上方”、“上部”以及类似者的空间相对术语可为易于描述而在本文中用来描述如图式中所示出的一个元件或特征与另一元件或特征的关系。除图式中所描绘的定向之外,空间相对术语意图涵盖器件在使用或操作时的不同定向。设备可以其它方式定向(旋转90度或处于其它定向)且本文中所使用的空间相对描述词可同样相应地进行解译。

66.本公开公开了用于以高数据速率接收数据的设备和方法,且设备被创造为紧凑的以便降低生产成本。用于恢复数据和数据时钟的电路中的一个为米勒-穆勒(mueller-muller)。然而,如果isi不是很高,那么米勒-穆勒对于从输入数据中恢复时钟是有效的。在具有高数据速率、pam-4编码以及强isi的数据的情况下,米勒-穆勒在恢复的数据时钟的频率和相位方面不能完美地恢复数据和数据时钟。米勒-穆勒不能为pam-4数据完美地恢复数据时钟的原因在于信道的脉冲响应不对称。由于接收到的数据或接收到的数据的脉冲响应不对称,且米勒-穆勒根据前光标数据和后光标数据具有相同水平的条件来检测所估计的峰值(光标数据样本),因此所估计的峰值不同于真实峰值。因此,在本公开的实施例中,提出包络检测器来解决这种问题。包络检测器通过基于数字信号处理原理执行一些功能来检测接收到的数据的真实峰值。此外,设备仅需要一个以每一符号一个样本(1

×

)频率采样的速率运行的模数转换器(analog to digital converter;adc)来将由接收器接收到的模拟数据采样为数字数据,因而,避免使用额外的adc或具有每一符号两个样本(2

×

)频率采样的速率的adc。因此,设备大小为紧凑的且设备生产成本降低。

67.具体来说,如下提供本公开的关于如何实施和配置包络检测器以改善米勒-穆勒检测器恢复由接收器接收到的接收到的数据的数据和数据时钟的功能的细节。

68.图1示出根据本公开的实施例的数据通信系统的框图。数据通信系统100可实施为具有一或多个传输器、接收器或其组合的电子移动器件或通信电子器件。在实施例中,数据通信系统100可应用于经由有线线路或无线线路连接的多个通信电子器件。

69.参考图1,数据通信系统100包含传输器(tx)107、信道(cn)105以及接收器(rx)

104。接收器104包含连续时间线性均衡器(continuous time equalizer;ctle)103、模数转换器(adc)102以及控制器101。ctle 103包含模拟线性处理单元(analog linear processing unit;alp)103-1和电压增益放大器(voltage gain amplifier;vga)103-2。传输器107耦接到信道105。传输器107接收原始数据且将所传输的数据传输到信道105。信道105耦接到接收器104的ctle 103。信道105将所传输的数据从传输器107携带到接收器104。到达接收器104的所传输的数据为接收到的数据。接收到的数据可与所传输的数据具有不同的振幅,且含有由包含isi的多个干扰产生的噪声。接收到的数据可为模拟数据。ctle 103耦接到adc 102。传输器将接收到的数据传送到adc 102作为输入数据。接收到的数据已由ctle 103(alp 103-1)处理以衰减低频数据。接收到的数据已进一步由ctle 103(vga 103-2)处理以扩增数据。adc 102耦接到控制器101。adc 102将从ctle 103接收到的输入数据从模拟数据转换为数字数据。数字数据可具有多个振幅/level,包含两个level、四个level或大于四个level。控制器101根据已由adc 102转换的输入数据来产生恢复的数据。在实施例中,传输器107、接收器104、adc 102以及控制器101可由多个电子电路实施。在实施例中,信道105可实施为包含信号的物理电线电缆或无线线路。在实施例中,控制器101可为处理器、现场可编程门阵列(field programmable gate array;fpga)、专用集成电路(application specific integrated circuit;asic)或任何集成可编程芯片。在实施例中,接收器可由56gbps serdes接收器或外围组件互连标准gen-6接收器实施。ctle 103可由2个极和1个具有可调整的电压增益放大器的零滤波器实施。

70.图2示出根据本公开的实施例的adc和包含多个单元的控制器的框图。框图200包含adc 102和控制器101。控制器101包含多个模块。adc 102配置成使用恢复的数据时钟将接收到的数据从模拟数据转换为数字数据。控制器101配置成从接收到的数据产生恢复的数据时钟和恢复的数据。接收到的数据可能遭受包含isi的多种噪声干扰。通过由控制器101在频率和相位方面正确地产生恢复的数据时钟,adc 102正确地对输入数据进行采样。因此,恢复的数据可正确地恢复且产生较低ber。

71.参考图2,控制器101包含时钟和数据恢复前馈均衡器(clock and data recovery feed forward equalizer;cdr ffe)202、多路复用器(mux)205、米勒-穆勒检测器时钟和数据恢复(mm检测器cdr)204、包络检测器时钟和数据恢复(包络检测器cdr)206、多路复用器(mux)208、相位内插器(phase interpolator;pi)210以及前馈均衡器和判决反馈均衡器数据路径(ffe+dfe数据路径)212。cdr ffe 202和ffe+dfe数据路径212可由有限脉冲响应(finite impulse response;fir)滤波器、无限脉冲响应(infinite impulse response;iir)滤波器或适合于数字信号处理的任何种类的滤波器来实施。cdr ffe 202和ffe+dfe数据路径212可应用于对具有高isi的数字数据进行滤波。mm检测器cdr 204和包络检测器cdr 206包含数字信号处理电路,其具有处理数字数据以检测数字数据的所估计的峰值的能力。对于包络检测器cdr 206的结构,稍后将按照图4进行详细描述。mm检测器cdr 204和包络检测器cdr 206分别产生cdr代码和另一cdr代码来控制pi 210以用于产生时钟。pi 210包含有时钟发生器,例如电压振荡器或电流振荡器。

72.在此实施例中,cdr ffe 202耦接到adc 102和mux 205,且配置成均衡输入数据。举例来说,输入数据包含isi,因而,与所传输的数据相比,输入数据的振幅已减小或衰减,或输入数据的频率已受到噪声频率的干扰。因此,cdr ffe 202对来自isi的输入数据滤波,

308以及pi 310具有分别与mm检测器cdr 204、包络检测器cdr 206、mux 205以及pi 210相同的功能。此外,相对于图2的控制器101,图3的控制器301具有包含加法器318和单元330的额外单元。单元330为继电器式(bang-bang)相位检测器cdr。单元330可实施为包含嵌入式振荡器的相位检测器,以检测输入数据与根据由mm检测器cdr 304产生的cdr代码所控制的嵌入式振荡器之间的相位差。

78.具体来说,如下描述控制器301的多个单元的布置。cdr ffe 202耦接到adc 102且配置成均衡输入数据作为均衡数据。mm检测器cdr 304耦接到cdr ffe 202且配置成从输入数据检测输入数据峰值。mux 308耦接到cdr ffe 202和adc 102。包络检测器cdr 306耦接到mux 308、mm检测器cdr 304以及加法器318,且配置成经由mux 308从输入数据或来自cdr ffe 202的均衡数据产生包络数据。包络检测器cdr 306接着从输入数据或均衡数据检测包络数据峰值。包络检测器cdr 306在检测包络数据峰值且完成cdr ffe 202的调适之后计算

‘

pre_cursor-post_cursor’偏移。当计算

‘

pre_cursor-post_cursor’偏移时,mux 308将cdr ffe输出连接到包络检测器cdr 306。在计算

‘

pre_cursor-post_cursor’偏移之后,包络检测器cdr 306初始化

‘

pre_cursor-post_cursor’偏移以由mm检测器cdr 304使用。加法器318耦接到包络检测器cdr 306和单元330。pi 310耦接到加法器318和adc 102且配置成产生恢复的数据时钟。ffe+dfe数据路径212耦接到adc 102且配置成产生恢复的数据。单元330耦接到adc 102和加法器318且配置成产生数据相位代码。由单元330产生的数据相位代码和由包络检测器cdr 306产生的另一cdr代码通过加法器318相加以产生组合代码。组合代码接着用于pi 310以产生具有最佳采样频率和最佳采样相位的cdr时钟。cdr时钟指定为恢复的数据时钟,其用于adc 102精确地对输入数据进行采样且产生数字数据形式。数字数据形式接着进一步由ffe+dfe数据路径212均衡以产生具有小ber的恢复的数据。

79.在此实施例中,单元330用于跟踪远端传输器时钟频率和本地振荡器频率中的有限百万分率(parts per million;ppm)差异。添加这种继电器式相位检测器cdr,这是因为包络检测器cdr是极低的带宽系统,且在基于包络检测的相位恢复期间,如果本地振荡器时钟与远端传输器时钟之间存在有限ppm差异,那么包络检测机制失败,因为包络检测机制需要在传入的数据相位的静态偏移相位处连续地采样以精确地计算包络值。因此其需要本地时钟频率以匹配传入的数据频率。

80.具体来说,单元330包含继电器式相位检测器322、mux 314、pi滤波器316以及pi 320。继电器式相位检测器322耦接到adc 102且配置成匹配输入数据相位和中间数据时钟。mux 314耦接到继电器式相位检测器322和mm检测器cdr 304。pi滤波器316耦接到mux 314且配置成产生均衡数据。pi 320耦接到pi滤波器316和继电器式相位检测器322且配置成产生中间数据时钟。

81.根据此实施例,pi滤波器316可为fir滤波器、iir滤波器或适合于信号处理的任何滤波器。pi 320的功能与pi 310类似。pi 320相对于pi 310的差异在于pi 320为继电器式相位检测器产生两个中间时钟(clk和clkb),而pi 310为adc产生cdr时钟。clkb为clk的互补。举例来说,如果clk具有上升边缘,那么clkb同时具有下降边缘。继电器式相位检测器322可实施为不归零(non-return-to-zero;nrz)继电器式相位检测器,因此其需要非常小的面积。继电器式相位检测器322可实施为由本领域的技术人员已知的另一相位检测器。继电器式相位检测器322将采样的数据与clk和clkb进行比较以产生相位差。相位差接着经由

pi滤波器316前馈到加法器318,以产生具有相位校正的cdr代码。这种校正的cdr代码接着由pi 310用来产生具有最佳频率和相位的cdr时钟。也就是说,通过将单元330包含到控制器301中,控制器301产生具有最佳频率和相位的恢复的数据时钟,因而,可产生具有小ber的恢复的数据。

82.图4示出根据本公开的实施例的adc和包含多个模块的包络检测器cdr的框图。包络检测器cdr 206包含绝对模块(abs)404、平均模块(avg)406、第一延迟模块408、符号模块(sign)410、加法器412以及第二延迟模块414。

83.参考图2和图4,abs 404耦接到adc 102。根据图3和图4,abs 404耦接到mux 308。abs 404配置成从有符号的数据产生绝对数据。举例来说,adc 102对输入数据进行采样以产生具有8位有符号的数据的数字数据形式。abs 404的输出馈送到avg 406的输入。avg 406配置成从绝对数据计算平均数据b。举例来说,当在2^17ui内累积输入的7位数据时,平均数据可为具有24位数据的数字数据。第一延迟模块408耦接到avg 406且配置成产生第一延迟数据a。第一延迟数据a可为相对于数据b具有t-1采样时间(采样时间约为2^17ui)的平均数据的数据样本。举例来说,如果在t采样时间处的当前数据表示数据b,那么数据a表示在早于数据b的采样时间的1个采样时间处的数据b的先前数据。且接着,数据a和数据b前馈到耦接到avg 406和第一延迟模块408的sign 410。sign 410配置成检查数据b相对于数据a是增加还是减少。如果数据b大于数据a,那么平均数据增加。相反,如果数据b小于数据a,那么平均数据减少。平均数据的增加表示sign 410的输出为负号,而平均数据的减少表示sign 410的输出为正号。通过确定符号是正还是负,可获得平均数据的方向。且接着,正号或负号接着输入到加法器412和耦接到sign 410的第二延迟模块414。加法器412和第二延迟模块414一起形成评估相位偏移的累加器。adc处的输入信号的离散时间表示可表示为传输器输出的样本与信道+接收器的模拟前端(包含vga和ctle)的组合系统的脉冲响应的乘积的总和,如等式1中所表示。在图5中绘示由cn和ctle产生的脉冲响应。第一项

‘

yin(0)*h(0)’为没有任何isi的理想输出。然而,由于信道isi,等式的第二部分损坏了输出。因此每一adc输入采样为信号分量和isi分量的总和。在图6中,相对于采样相位描绘信号分量(光标)和isi分量。接收器cdr需要找到且跟踪其中y_sig值最大的相位位置。包络检测器尝试相对于采样相位沿着ui估计y_sig分量。包络检测器获取adc输出,将其转换为绝对值,如等式3中所表示。

84.在等式1中,y_in(0)表示通常为随机序列的传输器输出,其中每一符号具有相等的正或负概率(各50%)。在等式2中,输出样本y_out表示为信号和isi分量的总和。y_out被较大的y_isi损坏,多数时候,y_isi的值小于y_sig,因为isi的所有贡献样本具有相同极性的概率非常小,因此多数时候y_out将匹配y_in的符号。因此,当添加y_out的连续样本时,由于添加了绝对值,因此项y_sig会累积,因为其始终转换为正号,而项y_isi会平均化,因为连续样本将具有随机极性和零均值分布的y_isi分量。因此,如果为大量样本(例如2^17个样本)累积项y_abs,那么y_isi会有效地抵消为小值(如果对于所有样本,yout符号始终与y_sig相同,那么理想地为0),这导致yabs_avg开始与y_sig成比例。cdr需要获得在ui中光标值最大的相位信息。

[0085][0086]

y_out=y_sig+y_isi

[0087]

等式2

[0088]yadc

=数字化(y_out)

[0089]

等式3

[0090]yabs

=y

adc

*符号(y

adc

)

[0091]

等式4

[0092][0093][0094]yacc

=y

sig_acc

+y

isi_acc

[0095]

等式7

[0096]

在另一实施例中,avg 406配置成通过在4.7微秒(例如2^17ui)内对绝对数据求平均值来计算平均数据的一个数据样本。平均数据的一个数据样本表示包络数据的一个数据样本。举例来说,adc 102通过使用具有1单位间隔(ui)的间隔的采样率来对输入数据进行采样以产生数字数据。在间隔4.7微秒内,数字数据具有多个数据样本。接着由abs 404处理在间隔4.7微秒的范围内的所有数据样本以产生绝对数据。绝对数据具有正号的数据且类似于等式4而产生。通过对绝对数据求平均值,可降低输入数据的噪声。此外,在眼数据图上,以高频率(即,56gbps或28gsps)进行采样的输入数据具有输入数据的不可辨识眼开口。因此,常规的mm检测器无法正确地执行数据峰值的检测。相反,通过对绝对数据求平均值以产生平均数据或包络数据,因为对绝对值求平均值的过程使用随机数据序列的统计性质以具有零均值,这导致isi分量平均化为零,而获取样本的绝对值的过程使得主光标(y_sig分量)极性始终为正,因此信号分量会随平均时间而累积。由于运用7位分辨率的每一样本对2^17个样本进行累积,因此包络数据具有24位分辨率,因而,可精确地执行包络数据峰值的检测。包络检测器为每个n-ui(例如2^17ui)提供输出,将当前的包络检测器输出与先前的包络检测器输出进行比较,且更新输入数据采样相位以使相位在包络增加的方向上移动。这将持续直到达到包络峰值,其后输入数据采样相位中的任何更新将导致下一个包络检测器输出值降低。一旦包络检测器已达到峰值,就冻结输入数据采样相位且启用并训练cdr-ffe均衡器,其后启用mm-cdr。

[0097]

在另一实施例中,使用延迟块408和符号差异块410将包络值随采样相位的变化计

算为增量或减量。延迟块408保持通过累积n-ui个样本(例如n=2^17)而计算的先前包络值。

[0098]

在另一实施例中,adc 102以恢复的数据时钟的1

×

速率对输入数据进行采样。换句话说,adc 102的采样速率与恢复的数据时钟的频率相同。通过使adc 102的采样速率与恢复的数据时钟的频率相同,adc 102不需要具有高分辨率特性,且可避免通信数据系统的开销。尽管adc 102仅具有以恢复的数据时钟的1

×

速率运行的频率,但数据通信系统100能够以最佳频率和相位产生恢复的数据时钟,因为数据通信系统100配备有包络检测器cdr 206或包络检测器cdr 306。包络检测器206或包络检测器306使输入数据最大化,且减少isi的存在以及检测输入数据的最佳峰值。因此,可产生最佳的恢复的数据时钟和恢复的数据。也就是说,通过在对应的数据通信系统100中包含包络检测器cdr 206或包络检测器cdr 306,具体来说,通过使用控制器200或控制器300的结构,可达成最佳的恢复的数据时钟和恢复的数据,因而,可获得接收到的数据的小ber。

[0099]

在另一实施例中,包络检测器cdr 206或包络检测器cdr 306确定mm检测器cdr 204或mm检测器cdr 304的最佳偏移。最佳偏移用于mm检测器cdr 204或mm检测器cdr 304以恢复由包络检测器cdr 206或包络检测器cdr 306检测到的最佳峰值。如我们先前所描述,常规的mm检测器根据如等式8中所描述的具有相同振幅的前光标和后光标来检测数据峰值。然而,因为接收到的数据或输入数据的数据眼由于不对称isi的存在而并不始终为对称的,所以由常规的mm检测器检测到的数据相位(中间峰值)未处于最佳峰值,且将导致较差的信噪比。因此,如等式9中所表示,需要用于将中间峰值转变为真实数据峰值的最佳偏移(optoffset)。包络检测器cdr 206或包络检测器cdr 306检测包络数据峰值且计算对应的

‘

pre_cursor-post_cursor’值,所述值为mm检测器cdr的最佳偏移。mm检测器cdr 204或mm检测器cdr 304接着使用这个最佳偏移来锁定到这个最佳输入数据采样相位且对其进行连续跟踪。因此,通过确定最佳偏移,mm检测器cdr204或mm检测器cdr 304可正确地检测真实数据峰值。也就是说,包络检测器cdr 206或包络检测器cdr 306通过将最佳偏移提供到mm检测器cdr 204或mm检测器cdr 304来改善mm检测器cdr 204或mm检测器cdr 304的性能。

[0100]

时序误差=pre_cursor-post_cursor

[0101]

等式8

[0102]

时序误差=pre_cursor-post_cursor-optoffset

[0103]

等式9

[0104]

图7示出根据本公开的实施例的控制器的启动顺序。由于控制器101或控制器301包含多个单元,因此为了产生恢复的数据时钟和恢复的数据,需要以特定顺序启动多个单元。

[0105]

参考图3和图7,举例来说,在步骤s702中,通过启动继电器式相位检测器322来开始控制器301的启动顺序。继电器式相位检测器322处理输入数据。所述继电器式相位检测器322运用由pi 320产生的clk和clkb相位将输入pam4数据采样为规则的pam2(nrz)数据。基于样本,所述继电器式相位检测器322产生路由到产生数据相位代码的pi滤波器的递增/递减信号,一旦锁定此继电器式相位检测器cdr(步骤s703),就通过启动包络检测器cdr 306来使顺序持续到步骤s704。由于mm检测器cdr仍未启动,因此adc 102的输出经由mux 308输入到包络检测器cdr 306。包络检测器cdr 306产生包络数据且检测表示恢复的数据

时钟的包络数据峰值。在启动mm检测器cdr 304之前首先启动包络检测器cdr 306的顺序至关重要,因为输入数据可能含有isi的高度存在。由于mm检测器cdr 304不具有最佳偏移,因此如果mm检测器304早于包络检测器cdr 306而启动,那么由mm检测器cdr 304检测到的数据峰值可能不表示真实数据峰值。当锁定包络检测器cdr(步骤s705)时,通过启动cdr ffe 202和ffe+dfe数据路径212来使顺序持续到步骤s706。通过启动cdr ffe 202和ffe+dfe数据路径212且已完成cdr ffe 202和ffe+dfe数据路径212的调适(步骤s707),准备好产生恢复的数据时钟和恢复的数据。恢复的数据时钟表示具有最佳频率和相位的数据时钟,因而可产生具有小ber的恢复的数据。由于包络检测器cdr 306已启动且检测包络数据峰值,因此通过计算mm检测器cdr最佳的

‘

pre_cursor-post_cursor’值来使顺序持续到步骤s708。且接着,在步骤s709中执行启动mm检测器cdr 304和禁用继电器式相位检测器322和包络检测器cdr的过程。mm检测器cdr 304根据由包络检测器cdr306检测到的包络数据峰值来计算偏移。也就是说,通过根据由图7所绘示的顺序来启动例如控制器301的多个单元,可产生具有最佳频率和相位的恢复的数据时钟和具有小ber的恢复的数据。

[0106]

图8示出根据本公开的实施例的用于数据通信的设备的方法。控制器包含步骤s802到步骤s806。由于cdr ffe对adc输出数据实施滤波过程,并且产生具有比输入数据更好的信噪比的均衡数据。在步骤s802中,包络检测器cdr从输入数据检测包络峰值。在步骤s803中,cdr ffe均衡adc输出数据且产生均衡数据。在cdr ffe滤波器调适已完成之后,在步骤s804中,包络检测器cdr中的逻辑估计mm检测器cdr用于检测最佳输入数据采样相位的

‘

pre_cursor

–

post_cursor’值。在步骤s804完成之后,在步骤s805中,mm检测器cdr被启用且开始跟踪输入数据采样相位,其条件是“pre_cursor-post_cursor”值等于在步骤s804中计算的值。在步骤s806中,ffe+dfe数据路径均衡器从adc输出数据产生均衡数据,所述均衡数据具有可能的最佳信噪比且因此具有较低的ber。

[0107]

另外,为了清楚地描述控制器301中的多个模块的逐步启动,提供了图9a至图9e。图9a至图9e示意性地示出图3中所给出的控制器301中的每一模块的启动的每一步骤。

[0108]

参考图9a,在步骤1中,启用/启动继电器式相位检测器cdr 330以获取频率锁定。如先前所提及,继电器式相位检测器cdr 330包含继电器式相位检测器322、mux 314、pi滤波器316以及pi 320。继电器式相位检测器cdr 330中的每一模块的启动绘示为标注“on”。另一方面,标注“off”表示模块尚未启动(即,pi 310尚未启动)。继电器式相位检测器322、mux 314、pi滤波器316以及pi 320形成继电器式检测器cdr环路。由于mm检测器cdr在此步骤中尚未启动,因此mux 314将信号从继电器式相位检测器322传送到pi滤波器316。继电器式相位检测器cdr环路将传入的pam4数据处理为简单的pam2信号且锁定到零交叉边缘,从而获取频率锁定。一旦继电器式相位检测器cdr 330已锁定,继电器式相位检测器cdr 330就准备好获取频率锁定,因而,控制器301执行下一步骤(步骤2)。

[0109]

参考图9b,在步骤2中,在继电器式相位检测器cdr 330跟踪传入的数据信号(输入数据)的零交叉边缘时,继电器式相位检测器cdr 330获取频率锁定。因此,在此步骤中,启动adc 102、cdr ffe 202、包络检测器cdr 306以及pi 310。mux 308将输入数据传送到包络检测器cdr 306。且接着,包络检测器cdr 306计算包络以获得最佳包络检测器cdr代码(另一cdr代码),且将此代码经由加法器318传送到pi 310以产生cdr时钟。加法器318从包络检测器cdr 306和继电器式相位检测器cdr 330接收信号。包络检测器cdr 306扫掠相位偏移,

同时找到每一相位偏移的包络值,且找到包络数据峰值。一旦包络检测器cdr 306找到包络数据峰值,控制器就执行步骤3。

[0110]

参考图9c,在步骤3中,执行cdr ffe调适。在于步骤2中检测最佳包络检测器cdr代码之后,启动cdr ffe 202且启用cdr ffe调适。一旦完成cdr ffe调适,控制器301就执行步骤4。

[0111]

参考图9d,在步骤4中,使用包络检测器cdr 306中的逻辑来计算

‘

pre_cursor-post_cursor’偏移。在此步骤中,使用mux 308将cdr ffe输出连接到包络检测器cdr 306。一旦计算

‘

pre_cursor-post_cursor’偏移,控制器301就执行步骤5。

[0112]

参考图9e,在步骤5中,启动mm检测器cdr 304和ffe+dfe数据路径。因此,停用(禁用)继电器式相位检测器322、pi 320以及包络检测器cdr 306。由于已调适cdr ffe 202,因此mm检测器cdr从cdr ffe 202接收信号。因此,由于已停用继电器式相位检测器322和pi 320,因此mux 314经由pi滤波器316将cdr代码从mm检测器cdr 304传送到加法器318。mm检测器cdr 304使用包络检测器cdr 306在先前的步骤中计算的

‘

pre_cursor-post_cursor’偏移。mm检测器cdr 306跟踪最佳采样相位且经由pi 310产生cdr时钟。adc 102将优化的cdr时钟用于对输入数据进行采样。最后,adc 102将采样的输入数据传送到ffe+dfe数据路径212以产生恢复的数据。通过这样做,可产生具有小ber的恢复的数据。

[0113]

图10示出根据本公开的实施例的mm检测器cdr的滤波器。mm检测器cdr 304包含mm检测器1002和cdr滤波器1010。cdr滤波器110包含比例均衡器1011、第一积分均衡器1012、第一整合单元1013、加法器1014、第二积分均衡器1015以及第二整合单元1016。mm检测器1002从例如cdr ffe输出接收信号。mm检测器1002根据前光标和后光标来计算时序误差(timing err=pre_cursor

–

post_cursor)。mm检测器1002耦接到cdr滤波器1010且将时序误差传送到cdr滤波器1010。cdr滤波器由2阶滤波器组成,且配置成对时序误差滤波。具体来说,mm检测器1002耦接到比例均衡器1011和第一积分均衡器1012。第一积分均衡器1012耦接到第一整合单元1013。第一整合单元1013和比例均衡器1011耦接到加法器1014。第二积分均衡器耦接到加法器1014和第二整合单元1016。第二整合单元1016产生用于mux 314的滤波器输出。

[0114]

前文已概述了数个实施例的特征以使得本领域的技术人员可更好地理解以下详细描述。本领域的技术人员应了解,其可易于使用本公开作为用于设计或修改用于进行本文中所引入的实施例的相同目的和/或达成相同优点的其它工艺和结构的基础。本领域的技术人员还应认识到,这类等效构造并不脱离本公开的精神和范围,且本领域的技术人员可在不脱离本公开的精神和范围的情况下在本文中作出各种改变、替代以及更改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1