视频处理系统以及方法与流程

1.本公开中所述实施例内容是有关于一种视频处理系统以及方法,特别关于一种可减轻系统处理电路工作量(loading)的视频处理系统以及方法。

背景技术:

2.随着技术的发展,越来越多电子装置会搭载摄影机以供使用者进行拍照或录像等功能。以录像为例,在现有技术中,当视频数据的分辨率越高,这些电子装置中的系统处理器的工作量将会越大。这会造成由系统处理器所运行的操作系统运行缓慢,甚至发生死机的问题。

技术实现要素:

3.本公开的一些实施方式是关于一种视频处理系统。视频处理系统包含系统处理电路以及视频处理电路。系统处理电路包含图像缓冲区以及开放多媒体加速层。图像缓冲区用以储存来自摄影机的视频数据。开放多媒体加速层用以提取相关于视频数据的至少一个数据参数。视频处理电路用以接收至少一个数据参数,依据至少一个数据参数从图像缓冲区接收视频数据,依据至少一个数据参数对视频数据进行编码以产生编码数据,且将编码数据传输至系统处理电路。

4.本公开的一些实施方式是关于一种视频处理方法。视频处理方法包含以下操作:通过系统处理电路的图像缓冲区储存来自摄影机的视频数据;通过系统处理电路的开放多媒体加速层提取相关于视频数据的至少一个数据参数;通过视频处理电路接收至少一个数据参数;通过视频处理电路依据至少一个数据参数从图像缓冲区接收视频数据;通过视频处理电路依据至少一个数据参数对视频数据进行编码以产生编码数据;以及通过视频处理电路将编码数据传输至系统处理电路。

5.综上所述,在本公开中,系统处理电路可提取视频数据的数据参数且将数据参数传输至视频处理电路。接着,视频处理电路可依据数据参数直接从图像缓冲区接收视频数据以进行后续的编码。据此,系统处理电路无需对视频数据进行多次复制,因此可降低系统处理电路的工作量,进而使得操作系统可运行顺畅。

附图说明

6.为让本公开的上述和其他目的、特征、优点与实施例能够更明显易懂,附图说明如下:

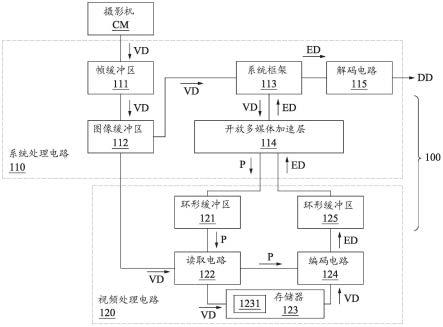

7.图1是依照本公开一些实施例所描绘的视频处理系统的示意图;以及

8.图2是依照本公开一些实施例所描绘的视频处理方法的流程图。

具体实施方式

9.在本文中所使用的术语“耦接”也可指“电性耦接”,且术语“连接”也可指“电性连

接”。“耦接”及“连接”也可指两个或多个元件相互配合或相互互动。

10.参考图1。图1是依照本公开一些实施例所描绘的视频处理系统100的示意图。

11.以图1示例而言,视频处理系统100包含系统处理电路110以及视频处理电路120。系统处理电路110耦接视频处理电路120以及摄影机cm。

12.视频处理系统100可设置于电子装置的系统芯片(system on chip,soc)上。在一些实施例中,若上述电子装置为智能电视,则摄影机cm可设置于智能电视的系统芯片的外部。在一些其他的实施例中,若上述电子装置为智能手机,则摄影机cm可与视频处理系统100整合且设置于智能手机的内部。

13.摄影机cm可用以进行拍照或录像等功能。以下将以录像功能为例进行说明。

14.在功能上,系统处理电路110主要运行与电子装置的操作系统相关的应用程序。举例而言,若该电子装置搭载安卓(android)操作系统,系统处理电路110可运行与安卓操作系统相关的应用程序。而视频处理电路120主要用以处理来自摄影机cm的视频数据vd。举例而言,当摄影机cm执行录像功能时,摄影机cm会产生视频数据vd。而视频处理电路120可对来自摄影机cm的视频数据vd进行编码且将编码后的数据回传至系统处理电路110。

15.以图1示例而言,系统处理电路110包含帧缓冲区(frame buffer)111、图像缓冲区(graphic buffer)112、系统框架(frame work)113、开放多媒体加速(open media acceleration,openmax)层114以及解码电路115。在一些实施例中,系统框架113以及开放多媒体加速层114是以软件实现且储存于系统处理电路110的储存元件中。

16.帧缓冲区111耦接摄影机cm以及图像缓冲区112。图像缓冲区112耦接系统框架113。开放多媒体加速层114耦接于系统框架113与视频处理电路120之间。系统框架113还耦接解码电路115。

17.以图1示例而言,视频处理电路120包含环形缓冲区(ring buffer)121、读取电路122、存储器123、编码电路124以及环形缓冲区125。

18.环形缓冲区121耦接开放多媒体加速层114以及读取电路122。读取电路122耦接存储器123以及编码电路124。编码电路124耦接存储器123以及环形缓冲区125。环形缓冲区125耦接开放多媒体加速层114。

19.以下将以视频处理系统100设置于搭载安卓操作系统的智能电视为例进行说明,但本公开不以此为限。

20.在操作上,当摄影机cm执行录像功能时,摄影机cm会产生原始的视频数据vd。视频数据vd会传输至帧缓冲区111。举例而言,在帧缓冲区111中的视频数据vd会以一帧一帧的形式储存。接着,视频数据vd可通过应用程序接口(例如:camerahal)被转化且储存至图像缓冲区112。该应用程序接口可利用软件实现。举例而言,视频数据vd会依据操作系统(例如:安卓操作系统)的规范储存于图像缓冲区112中。在一些实施例中,图像缓冲区112可配置于系统处理电路110的动态随机存取存储器(dynamic random-access memory,dram)中。

21.视频数据vd可通过操作系统的系统框架113传输至开放多媒体加速层114。而开放多媒体加速层114可提取相关于视频数据vd的至少一个数据参数p。接着,开放多媒体加速层114可将数据参数p传输至视频处理电路120。在一些实施例中,数据参数p可包含视频数据vd在图像缓冲区112中的物理地址(physical address)、视频数据vd的数据尺寸(size)以及视频数据vd的编码格式中的至少一个。数据尺寸例如是数据长度。编码格式例如是yuv

或rgb。在一些实施例中,前述物理地址、数据尺寸以及编码格式可封装于数据结构中,以传输至视频处理电路120。

22.视频处理电路120可从系统处理电路110接收数据参数p,且依据数据参数p从图像缓冲区112接收视频数据vd。具体而言,环形缓冲区121可从开放多媒体加速层114接收数据参数p,且将数据参数p传输至读取电路122。而读取电路122可接收数据参数p,且依据数据参数p向存储器123请求视频处理缓冲区1231。另一方面,读取电路122可依据数据参数p将储存于图像缓冲区112中的视频数据vd读取出来。举例而言,读取电路122可依据数据参数p所携带的物理地址判断要读取的视频数据vd被储存于图像缓冲区112中的对应位置,且可依据数据参数p所携带的数据尺寸判断欲读取的视频数据vd的数据量。据此,读取电路122可依据上述的物理地址以及数据尺寸将储存于图像缓冲区112中的视频数据vd读取出来。接着,读取电路122可将读取出来的视频数据vd存入视频处理缓冲区1231。视频处理缓冲区1231的容量则可依据从图像缓冲区112读取出来的视频数据vd的数据量而决定。

23.编码电路124可接收来自读取电路122的数据参数p且接收来自视频处理缓冲区1231的视频数据vd。如前所述,数据参数p还可包含视频数据vd的编码格式。也就是说,编码电路124可依据数据参数p中的编码格式(例如:yuv或rgb)对视频数据vd进行编码以产生编码数据ed。

24.接着,开放多媒体加速层114可接收来自环形缓冲区125的编码数据ed。开放多媒体加速层114可将编码数据ed传送至系统框架113。而系统框架113可将编码数据ed传输至解码电路115。而解码电路115可对编码数据ed进行解码以产生解码数据dd。

25.在一些实施例中,解码数据dd可供显示器显示出对应的影像。在一些其他的实施例中,解码数据dd也可被储存起来。

26.在一些相关技术中,摄影机所产生的视频数据会先被复制至开放多媒体加速层的缓冲区。接着,再从开放多媒体加速层的缓冲区复制至视频处理电路中的共享存储器中。换句话说,视频数据在系统处理电路中会被多次复制。然而,多次的复制将会增加系统处理电路的工作量。尤其,编码前的视频数据的数据量非常庞大且随着视频数据的分辨率越高,系统处理电路的工作量将会越大。这会造成由系统处理器所运行的操作系统运行缓慢,甚至发生当机的问题。

27.相较于上述这些相关技术,在本公开中,系统处理电路110可提取视频数据vd的数据参数p且将数据参数p传输至视频处理电路120。接着,视频处理电路120可依据数据参数p直接从图像缓冲区112接收(复制)视频数据vd以进行后续的编码。据此,视频数据vd无需在系统处理电路110中进行多次复制,因此可降低系统处理电路110的工作量,进而使得操作系统可运行顺畅。

28.另外,视频处理电路120主要是以硬件实现。据此,相较于上述这些相关技术利用软件(系统框架113、开放多媒体加速层114)进行数据复制,以硬件实现的视频处理电路120的数据复制速度较快,因此本公开可提高对视频数据vd的处理效率。

29.再者,通过本公开的作法,无需降低视频数据vd的分辨率或帧率,也无需关闭其他由系统处理电路110所运行的应用程序。

30.参考图2。图2是依照本公开一些实施例所描绘的视频处理方法200的流程图。以图2示例而言,视频处理方法200包含操作s210、操作s220、操作s230、操作s240、操作s250以及

操作s260。应了解到,在本实施方法中所提及的操作,除特别说明其顺序的外,均可依实际需要调整其前后顺序,甚至可同时或部分同时执行

31.在一些实施例中,视频处理方法200可应用于图1中的视频处理系统100中,但本公开不以此为限。为易于理解,以下段落将结合图1的视频处理系统100进行描述。

32.在操作s210中,通过系统处理电路110的图像缓冲区112储存来自摄影机cm的视频数据vd。在一些实施例中,摄影机cm可设置于电子装置的系统芯片外部。在一些实施例中,摄影机cm可设置于电子装置的系统芯片上。

33.在操作s220中,通过系统处理电路110的开放多媒体加速层114提取相关于视频数据vd的数据参数p。在一些实施例中,数据参数p包含视频数据vd在图像缓冲区112的物理地址、视频数据vd的数据尺寸以及视频数据vd的编码格式中的至少一个。

34.在操作s230中,通过视频处理电路120接收数据参数p。在一些实施例中,数据参数p可从开放多媒体加速层114传输至环形缓冲区121。

35.在操作s240中,通过视频处理电路120依据数据参数p从图像缓冲区112接收视频数据vd。在一些实施例中,读取电路122可依据上述的物理地址以及数据尺寸将储存于图像缓冲区112中的视频数据vd读取出来。

36.在操作s250中,通过视频处理电路120依据数据参数p对视频数据vd进行编码以产生编码数据ed。在一些实施例中,编码电路124可依据数据参数p中的编码格式(例如:yuv或rgb)对视频数据vd进行编码以产生编码数据ed。

37.在操作s260中,通过视频处理电路120将编码数据ed传输至系统处理电路110。在一些实施例中,编码数据ed可从环形缓冲区125传输至开放多媒体加速层114,且通过系统框架113传输至解码电路115。

38.综上所述,在本公开中,系统处理电路可提取视频数据的数据参数且将数据参数传输至视频处理电路。接着,视频处理电路可依据数据参数直接从图像缓冲区接收视频数据以进行后续的编码。据此,系统处理电路无需对视频数据进行多次复制,因此可降低系统处理电路的工作量,进而使得操作系统可运行顺畅。

39.各种功能性元件和模块已在此公开。对于本技术领域普通技术人员而言,功能模块可由电路(不论是专用电路,或是在一个或多个处理器及编码指令控制下操作的通用电路)实现,其一般而言包含用以相应于此处描述的功能及操作对电气回路的操作进行控制的晶体管或其他电路元件。进一步地理解,一般而言电路元件的具体结构与互连,可由编译器(compiler),例如寄存器传送语言(register transfer language,rtl)编译器决定。寄存器传送语言编译器对与汇编语言代码(assembly language code)相当相似的脚本(script)进行操作,将脚本编译为用于布局或制作最终电路的形式。确实地,寄存器传送语言以其促进电子和数字系统设计过程中的所扮演的角色和用途而闻名。

40.虽然本公开已以实施方式公开如上,然其并非用以限定本公开,任何本领域普通技术人员,在不脱离本公开的精神和范围内,当可作各种的改变与改进,因此本公开的保护范围当视后附的权利要求范围所界定的为准。

41.附图标记说明:

42.100:视频处理系统

43.110:系统处理电路

44.111:帧缓冲区

45.112:图像缓冲区

46.113:系统框架

47.114:开放多媒体加速层

48.115:解码电路

49.120:视频处理电路

50.121:环形缓冲区

51.122:读取电路

52.123:存储器

53.1231:视频处理缓冲区

54.124:编码电路

55.125:环形缓冲区

56.200:视频处理方法

57.cm:摄影机

58.vd:视频数据

59.ed:编码数据

60.dd:解码数据

61.p:数据参数

62.s210,s220,s230,s240,s250,s260:操作

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1