用于互连协议的错误处理的方法、控制器以及存储设备与流程

1.本发明涉及一种电子设备,特别涉及用于互连协议的错误处理的方法、控制器以及存储设备。

背景技术:

2.现今移动设备(如智能手机、平板电脑、多媒体设备、穿戴式设备之类的运算设备)中产生和处理的数据量不断增加,移动设备内部的芯片对芯片的或受移动设备影响的互连接口技术需要进一步的演进,从而达至能够满足更高的传输速度、低功耗操作、具可扩充性、支援多工处理、易于采用等目标。

3.为此,行动产业处理器接口(mobile industry processor interface,mipi)联盟开发出能够符合上述目标的互连接口技术,例如关于物理层的mipi m-phy规范以及关于统一协议(unified protocol,unipro)的mipi unipro规范。另一方面,联合电子设备工程委员会(joint electron device engineering council,jedec)利用mipi m-phy规范及通用传输协议mipi unipro规范推出下一代高性能非易失性存储器标准,称为通用闪存存储(universal flash storage,ufs),其可实现每秒十亿位等级的高速传输及低功耗操作,并具有高阶行动系统所需的功能和可扩展性,从而有助于为业界快速的采用。

4.技术人员在依据这些互连接口技术来开发的产品为相关芯片、电子模块或电子设备时,要确保产品的功能及操作能够符合规范。举例而言,依据ufs标准而实现的系统如包含了运算设备及非易失性存储器的存储设备,运算设备及存储设备分别担任本地的(local)主机与遥距的(remote)设备的角色。主机与设备建立起双向的链路(link),且主机与设备之间的链路可以在任何一个传输方向上配置为多个(最多4个)通道(lane)。相对应地,主机与设备各自地配置依据unipro规范的互连协议的处理电路需要具备处理多个通道的功能。

5.依据unipro规范需要在数据链路层(data link layer,dl layer)实现错误处理(error handling),当主机与设备中任何一方(或称目标端)发现接收的数据有错误时,发现错误的一方(或目标端)应主动向另一方(或称发起端)发送表示错误发生的通知信号,如“否定应答控制”6.(negative acknowledgment control,nac)帧,并因而触发另一方(或发起端)再传输数据。

技术实现要素:

7.实施方式提供了一种用于互连协议的错误处理的技术,适用于能够依据所述互连协议链接第二设备的第一设备中。所述技术在所述第一设备对来自所述第二设备的帧进行接收的处理过程中,且每个时钟周期允许接收多个帧的情况下,能够在互连协议下正确且有效率地实现错误处理中表示错误发生的通知信号的传输。

8.以下依据所述技术提出各种实施方式,如用于互连协议的错误处理的方法、控制

器以及存储设备。

9.实施方式提供了一种用于互连协议的错误处理的方法,适用于能够依据所述互连协议链接第二设备的第一设备中,所述方法包括:在所述第一设备对来自所述第二设备的帧进行接收的处理过程中,且每个时钟周期允许接收多个帧的情况下:a)接收用以表示每个时钟周期中出现的帧是否发生错误及错误所对应的符号位置的帧错误位置标示信号及接收用以表示每个时钟周期中出现的帧是否正确及对应的符号位置的帧正确位置标示信号;b)依据所述帧错误位置标示信号及所述帧正确位置标示信号,且在允许“否定应答控制”(negative acknowledgment control,nac)帧传输的状态下,判别出第一时钟周期中有一个帧错误发生,且请求nac帧传输之后,指示进入禁止nac帧传输的状态;以及c)在所述第一时钟周期后,比较所述帧错误位置标示信号及所述帧正确位置标示信号,来根据帧错误情形而决定是否搁置请求nac帧传输。

10.实施方式提供了一种控制器,适用于能够依据互连协议链接第二设备的第一设备中,所述控制器包括:接口电路及控制器模块。所述接口电路用于实现所述互连协议的物理层以链接所述第二设备。所述控制器模块用于耦接到所述接口电路,且用于实现所述互连协议的链接层。其中在所述第一设备对来自所述第二设备的帧进行接收的处理过程中,且每个时钟周期允许接收多个帧的情况下,所述控制器模块执行多个操作,所述多个操作包括:a)接收用以表示每个时钟周期中出现的帧是否发生错误及错误所对应的符号位置的帧错误位置标示信号及接收用以表示每个时钟周期中出现的帧是否正确及对应的符号位置的帧正确位置标示信号;b)依据所述帧错误位置标示信号及所述帧正确位置标示信号,且在允许“否定应答控制”(negative acknowledgment control,nac)帧传输的状态下,判别出第一时钟周期中有一个帧错误发生,且请求nac帧传输之后,指示进入禁止nac帧传输的状态;以及c)在所述第一时钟周期后,比较所述帧错误位置标示信号及所述帧正确位置标示信号,来根据帧错误情形而决定是否搁置请求nac帧传输。

11.实施方式提供了一种存储设备,能够依据互连协议链接主机,所述存储设备包括:存储模块、接口电路及设备控制器。所述接口电路用于实现所述互连协议的物理层以链接所述主机。所述设备控制器用于耦接到所述接口电路和所述存储模块,且用于实现所述互连协议的链接层,其中在所述存储设备对来自所述主机的帧进行接收的处理过程中,且每个时钟周期允许接收多个帧的情况下,所述设备控制器执行多个操作,所述多个操作包括:a)接收用以表示每个时钟周期中出现的帧是否发生错误及错误所对应的符号位置的帧错误位置标示信号及接收用以表示每个时钟周期中出现的帧是否正确及对应的符号位置的帧正确位置标示信号;b)依据所述帧错误位置标示信号及所述帧正确位置标示信号,且在允许“否定应答控制”(negative acknowledgment control,nac)帧传输的状态下,判别出第一时钟周期中有一个帧错误发生,且请求nac帧传输之后,指示进入禁止nac帧传输的状态;以及c)在所述第一时钟周期后,比较所述帧错误位置标示信号及所述帧正确位置标示信号,来根据帧错误情形而决定是否搁置请求nac帧传输。

12.在上述方法、控制器或存储设备的一些实施例中,所述方法或所述多个操作还包括:依据每个时钟周期中出现的帧是否发生错误及错误所对应的符号位置而产生所述帧错误位置标示信号,并依据每个时钟周期中出现的帧是否正确及所对应的符号位置而产生所述帧正确位置标示信号。

13.在上述方法、控制器或存储设备的一些实施例中,所述步骤c)或操作c)包括:在所述第一时钟周期后的第二时钟周期中有一个正确帧及一个错误帧时,若所述帧正确位置标示信号对应的数值小于所述帧错误位置标示信号对应的数值,则指示进入允许nac帧传输的状态并搁置请求nac帧传输直至允许nac帧传输的状态成立以后。

14.在上述方法、控制器或存储设备的一些实施例中,所述步骤c)或操作c)包括:在所述第一时钟周期后的第二时钟周期中有一个正确帧及一个错误帧时,若所述帧正确位置标示信号对应的数值大于所述帧错误位置标示信号对应的数值,则指示进入允许nac帧传输的状态并忽略请求nac帧传输。

15.在上述方法、控制器或存储设备的一些实施例中,所述互连协议是通用闪存存储(universal flash storage,ufs)标准。

附图说明

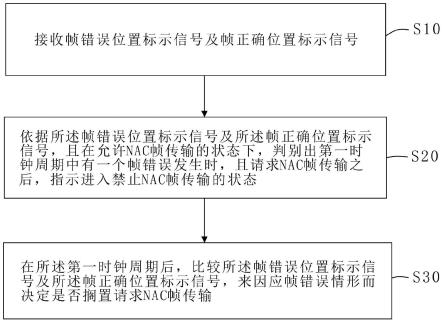

16.图1为用于互连协议的错误处理的方法的一种实施方式的流程图。

17.图2为存储系统的一种实施方式的示意方块图。

18.图3为图2的存储系统依据ufs标准的分层架构的示意图。

19.图4为依据unipro标准的数据链路层的数据帧的格式的示意图。

20.图5a为在每个时钟周期允许接收多个帧的情况下影响是否致能nac帧传输的情况的示意图。

21.图5b为在每个时钟周期允许接收多个帧的情况下产生是否要再次致能nac帧传输的次序问题的示意图。

22.图6为实现上述用于互连协议的错误处理的方法的电路架构的一种实施方式的示意图。

23.图7为依据图6的电路架构中nac传输处理单元的一种实施例的示意图。

24.图8为依据图1的方法实现用于互连协议的错误处理的方法的一个实施例的示意图。

25.图9为依据图1的方法实现用于互连协议的错误处理的方法的一个实施例的示意图。

26.图10为依据图1的方法实现用于互连协议的错误处理的方法的一个实施例的示意图。

27.图11为依据图1的方法实现用于互连协议的错误处理的方法的一个实施例的示意图。

28.图12为依据图1的方法实现用于互连协议的错误处理的方法的一个实施例的示意图。

29.附图标记

[0030]1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储系统

[0031]

10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

主机

[0032]

11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

主机接口

[0033]

12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

主机控制器

[0034]

13

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

硬件协议引擎

[0035]

14

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

处理单元

[0036]

16

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

应用处理器

[0037]

20

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储设备

[0038]

21

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

设备接口

[0039]

22

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

设备控制器

[0040]

23

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

硬件协议引擎

[0041]

24

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

处理单元

[0042]

26

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储模块

[0043]

110

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

mipi物理(m-phy)层

[0044]

111

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

发送器

[0045]

112

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接收器

[0046]

130

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

mipi统一协议(unipro)层

[0047]

131

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

物理适配器层

[0048]

132

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据链路层

[0049]

133

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

网络层

[0050]

134

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

传输层

[0051]

135

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

设备管理实体(dme)

[0052]

210

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

mipi物理(m-phy)层

[0053]

211

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

发送器

[0054]

212

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接收器

[0055]

230

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

mipi统一协议(unipro)层

[0056]

231

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

物理适配器层

[0057]

232

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据链路层

[0058]

233

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

网络层

[0059]

234

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

传输层

[0060]

235

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

设备管理实体(dme)

[0061]

300

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据链路层电路

[0062]

310

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据链路层接收器(dl rx)电路

[0063]

311

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

帧接收处理单元

[0064]

315、315a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

nac传输处理单元

[0065]

321、322、323

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

同步模块

[0066]

330

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据链路层传送器(dl tx)电路

[0067]

410

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

逻辑单元

[0068]

420

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

比较单元

[0069]

430

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

nac_req_mask产生单元

[0070]

s10~s30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

步骤

[0071]

clk

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时钟线

[0072]

din、dout

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据线

[0073]

rst

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

复位线

[0074]

sl1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据通道

[0075]

sl2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据通道

具体实施方式

[0076]

为充分了解本发明的目的、特征及功效,兹借由下述具体的实施例,并配合所附的图式,对本发明做详细说明,说明如后。

[0077]

以下实施方式提供了一种用于互连协议的错误处理的技术,适用于能够依据所述互连协议链接第二设备的第一设备中。所述技术在所述第一设备对来自所述第二设备的帧进行接收的处理过程中,且每个时钟周期允许接收多个帧的情况下,能够在互连协议下正确且有效率地实现错误处理中表示错误发生的通知信号的传输,如nac帧传输。

[0078]

请参考图1,其为用于互连协议的错误处理的方法的一种实施方式的流程图。所述方法可用于能够依据一种互连协议链接第二设备(如图2的主机10)的第一设备(如图2的存储设备20)中。为便于说明,以下就以第一设备为存储设备20,第二设备为主机10来举例说明。如图1所示,所述方法包括步骤s10~s30。所述多个步骤可以在所述第一设备(如存储设备20)的用于实现所述互连协议的链接层的硬件协议引擎(如硬件协议引擎23)依据所述互连协议的所述链接层,在所述第一设备(如存储设备20)对来自所述第二设备(如主机10)的帧进行接收的处理过程中执行。此外,所述方法适用于所述链接层在多个通道被启用的应用情景下,其中所述链接层中数据链路层在每单位时钟周期需要处理的帧中的符号的数量可能达8个或以上,或在每单位时钟周期支援处理两个或以上数量的帧。

[0079]

在所述第一设备对来自所述第二设备的帧进行接收的处理过程中,且每个时钟周期允许接收多个帧的情况下:

[0080]

如步骤s10所示,接收用以表示每个时钟周期中出现的帧是否发生错误及错误所对应的符号位置的帧错误位置标示信号及接收用以表示每个时钟周期中出现的帧是否正确及对应的符号位置的帧正确位置标示信号。

[0081]

如步骤s20所示,依据所述帧错误位置标示信号及所述帧正确位置标示信号,且在允许“否定应答控制”(negative acknowledgment control,nac)帧传输的状态下,判别出第一时钟周期中有一个帧错误发生,且请求nac帧传输之后,指示进入禁止nac帧传输的状态。

[0082]

如步骤s30所示,在所述第一时钟周期后,比较所述帧错误位置标示信号及所述帧正确位置标示信号,来根据帧错误情形而决定是否搁置请求nac帧传输。

[0083]

在上述方法的一些实施例中,所述方法还包括:依据每个时钟周期中出现的帧是否发生错误及错误所对应的符号位置而产生所述帧错误位置标示信号,并依据每个时钟周期中出现的帧是否正确及所对应的符号位置而产生所述帧正确位置标示信号。

[0084]

在上述方法的一些实施例中,所述步骤c)包括:在所述第一时钟周期后的第二时钟周期中有一个正确帧及一个错误帧时,若所述帧正确位置标示信号对应的数值小于所述帧错误位置标示信号对应的数值,则指示进入允许nac帧传输的状态并搁置请求nac帧传输直至允许nac帧传输的状态成立以后。

[0085]

在上述方法的一些实施例中,所述步骤c)包括:在所述第一时钟周期后的第二时钟周期中有一个正确帧及一个错误帧时,若所述帧正确位置标示信号对应的数值大于所述

帧错误位置标示信号对应的数值,则指示进入允许nac帧传输的状态并忽略请求nac帧传输。

[0086]

在上述方法、控制器或存储设备的一些实施例中,所述互连协议是通用闪存存储(universal flash storage,ufs)标准。

[0087]

在上述关于图1的方法的实施例中,虽然以第一设备为存储设备20,第二设备为主机10来举例说明,然而所述方法亦适用于第一设备为主机10,第二设备为存储设备20的情况下。

[0088]

以下举例以说明依据图1的方法的各种实现方式。

[0089]

为便于理解及说明,以下首先依据所述技术提供一种电路架构的实施方式,这种电路架构具足够弹性及能够有效率地被配置来满足不同产品的需求,以适应各种厂商的设计而有助于产品开发。如图2所示,这种电路架构应用于存储系统1时,存储系统1的主机10的控制器模块(如主机控制器12)或存储系统1的存储设备20的控制器模块(如设备控制器22)可分别实现为包括硬件协议引擎及处理单元的电路架构,其中所述控制器的处理单元为可选的。又例如,可依据主机接口11及主机控制器12的结合而作为控制器,如单晶片,用于主机10;另外,可依据设备接口21及设备控制器22的结合而作为控制器,如单晶片,用于存储设备20。

[0090]

请参考图2,其为依据本发明的一种实施方式的存储系统的示意方块图。如图2所示,存储系统1包括主机10及存储设备20。主机10及存储设备20之间通过一种互连协议来通信,从而让主机10对存储设备20进行数据的存取。所述互连协议例如是通用闪存存储(universal flash storage,ufs)标准。主机10例如是智能手机、平板电脑、多媒体设备之类的运算设备。存储设备20例如是所述运算设备内部或外部的存储设备,例如是基于非易失性存储器的存储设备。存储设备20可以在主机10的控制下写入数据或向主机10提供被写入数据。存储设备20可以被实现为固态存储设备(ssd),多媒体卡(mmc),嵌入式mmc(emmc)、安全数字(sd)卡或通用闪存存储(ufs)设备,然而本揭露内容的实现并不受限于上述示例。

[0091]

主机10包括主机接口11、主机控制器12及应用处理器16。

[0092]

主机接口11用于实现所述互连协议的物理层以链接所述存储设备20。例如,主机接口11用以实现ufs标准的物理(m-phy)层。

[0093]

主机控制器12耦接于主机接口11与应用处理器16之间。当应用处理器16需要对存储设备20进行数据的存取时,发出代表对应的存取动作指令至主机控制器12,通过所述互连协议与存储设备20沟通,从而达成对存储设备20进行数据的存取。

[0094]

主机控制器12包括硬件协议引擎13及处理单元14。其中处理单元14为可选的。

[0095]

硬件协议引擎13用于实现所述互连协议的链接层。就以所述互连协议为ufs标准为例,所述链接层为统一协议(unified protocol,unipro)层。硬件协议引擎13依据所述链接层的规范来与主机接口11及处理单元14进行沟通及信息的转换。

[0096]

处理单元14,其与所述硬件协议引擎13耦接,用以与应用处理器16进行通信。处理单元14可执行一个或多个固件。例如应用处理器16所执行的操作系统、驱动程序或应用程序所发出的存取动作指令通过处理单元14所执行的固件转换为符合所述互连协议的链接层的指令格式,并继而发送至硬件协议引擎13以依据所述链接层的规范来进行处理。固件例如可存储于处理单元14的内部存储器,或存储于主机控制器12的内部存储器,其中内部

存储器可包括易失性存储器及非易失性存储器。

[0097]

存储设备20包括设备接口21、设备控制器22及存储模块26。

[0098]

设备接口21用于实现所述互连协议的物理层以链接所述主机10。例如,主机接口21用以实现ufs标准的物理(m-phy)层。

[0099]

设备控制器22耦接于设备接口21与存储模块26之间。设备控制器22可以控制存储模块26的写入操作、读取操作或抹除操作。设备控制器22可以通过地址总线或数据总线与存储模块26交换数据。存储模块26例如包含一个或多个非易失性存储器的存储器晶片。

[0100]

设备控制器22包括硬件协议引擎23及处理单元24。其中处理单元24为可选的。

[0101]

硬件协议引擎23用于实现所述互连协议的链接层。就以所述互连协议为ufs标准为例,所述链接层为unipro层。硬件协议引擎13依据所述链接层的规范来与设备接口21及处理单元24进行沟通及信息的转换。

[0102]

处理单元24,其与所述硬件协议引擎23耦接,用以通过设备接口21而与主机10进行通信。处理单元24可执行一个或多个固件。例如处理单元24执行一个或多个固件来控制或指示存储模块26的写入操作、读取操作或抹除操作,对来自硬件协议引擎23的信息作处理或将信息发送至硬件协议引擎23。固件例如可存储于处理单元24的内部存储器、设备控制器22的内部存储器,或存储模块26的特定存储区域,其中内部存储器可包括易失性存储器及非易失性存储器。

[0103]

如图2所示,主机接口11能够通过用于发送/接收数据的数据线din和dout、用于发送硬件复位信号的复位线rst、用于发送数据的时钟线clk而与设备接口21耦接。数据线din和dout可以被实现为多对,其中一对的数据线din或dout可称为一个通道(lane)。主机接口11可以使用至少一种接口协议与设备接口21行通信,接口协议诸如移动工业处理器接口(mipi)、通用闪存存储(ufs)、小型计算机系统接口(scsi)或串行连接的scsi(sas),然而本揭露内容的实现并不受限于上述示例。在ufs标准之下,主机10及存储设备20之间可以配置为支持多个通道,以增进传输的效率,其中在主机10至存储设备20之间或存储设备20至主机10之间的任一方向上目前最多能支持2个通道,多个通道可以选择设定为启用或不启用。

[0104]

以下借由所述互连协议为通用闪存存储(ufs)标准为例作详细说明。ufs标准中包含ufs指令集层(ufs command set layer,usc)、ufs传输协议层(ufs transport layer,utp)及ufs互连层(ufs interconnect layer,uic)。uic又包含链接层及物理层,uic的链接层依据unipro规范而定义,uic的物理层依据m-phy规范而定义。

[0105]

请参考图3,其为图2的存储系统依据ufs标准的分层架构的示意图。由于ufs标准基于mipi统一协议(unipro)层以及mipi物理(m-phy)层,图2所示的主机10的主机接口11及硬件协议引擎13分别用以实现图3中的m-phy层110及unipro层130;图2所示的存储设备20的设备接口21及硬件协议引擎23分别用以实现图3中的m-phy层210及unipro层230。

[0106]

如图3所示,unipro层130(或230)可以包括物理适配器层(phy adapter layer,pa)131(或231)、数据链路层(data link layer,dl)132(或232)、网络层(network layer)133(或233)和传输层(transport layer)134(或234)。存储设备20的unipro层230中的各个层也可以相似地操作及实现。

[0107]

物理适配器层(131或231)用以将m-phy层(110或210)耦接到数据链路层(132或232)。物理适配器层(131或231)可以在m-phy层(110或210)和数据链路层(132或232)之间

执行频宽控制、功率管理等。在实现时,主机10的m-phy层110包含发送器111及接收器112,又存储设备20的m-phy层210包含发送器211及接收器212,借此能够建立数据通道sl1及sl2以进行全双功通信。unipro规范支援在每一传输方向上(如前向或反向)的链路有多个数据通道。

[0108]

数据链路层(132或232)可以执行用于主机10和存储设备20之间的数据传输的流程控制(flow control)。即,数据链路层(132或232)可以监视数据传输或控制数据传输速率。此外,数据链路层(132或232)可以执行基于循环冗余校验(cyclic redundancy check,crc)的错误控制。数据链路层(132或232)可以使用从网络层(133或233)接收到的分组来产生帧(frame),或者可以使用从物理适配器层(131或231)接收到的帧来产生分组。

[0109]

网络层(133或233)用于对于从传输层(134或234)接收的分组选择传输路径的路由功能。

[0110]

传输层(134或234)可以使用从ufs应用层接收的命令来配置适合于协议的数据段(segment),并且将所述数据段发送到网络层(133或233),或者可以从网络层(133或233)接收的分组中提取命令并且发送所述命令至ufs应用层。传输层(134或234)可以使用基于序列的错误控制方案,以保证数据传输的有效性。

[0111]

再者,unipro层(130或230)中还定义了设备管理实体(device management entity,dme)(135或235),其能够与m-phy层(110或210)及unipro层(130或230)中的各层互通,如物理适配器层(131或231)、数据链路层(132或232)、网络层(133或231)和传输层(134或234)以至ufs应用层互通,从而实现涉及统一协议(unipro)整体性的功能如开机、关机、复位、功耗模式改变等控制或组态的功能。

[0112]

请参考图4,其为依据unipro标准的数据链路层的数据帧的格式的示意图。如图4所示,在数据帧的有效载荷(可称l2有效载荷,l2payload)所负载的数据为0字节时,所述数据帧最小包含4个协议数据单元(如4个16位的数据),其中有1个协议数据单元含有帧启始标记(sof)。此外,所述含有帧启始标记(sof)的协议数据单元还可含有运输级别(traffic class)标记,例如是tc0、tc1以表现优先权等级。此外,esc_dl标记代表此帧为数据链路层的帧,eof_even(或eof

‑‑‑

_odd)为代表帧结束标记(end of frame,eof),crc-16代表循环冗余校验码。由此,如图4的帧可视为至少包含了多个符号(或称为协议数据单元(pdu))。在以下图式或说明中,例如用sof、dx0、

……

、dxy、eof、crc符号来代表包含了多个符号的一个帧,其中x代表帧的编号,y代表这个帧x的第y个符号。例如d00表示第1个帧的第1个符号,d01表示第1个帧的第2个符号,如此类推。当然,l2有效载荷可以有多个,故帧可包含4个以上的符号。故数据帧至少有4个符号。

[0113]

在多个通道被启用(active)的情景下,框讯传送方式,是将一个帧的符号(symbol)同步通过多个通道来传送(每个符号代表16位的有效数据)。例如,在ufs标准中,从mipi m-phy v4.x规范来看,从m-phy到pa层的数据宽度最大为1个通道有32位和2个通道有64位。

[0114]

为了提高数据通量(throughput),在一些实作中,本案发明人提出可以将m-phy实现为1个通道有64位和2个通道有128位,此为超越目前在ufs标准中,m-phy规范的限制的实作方式。在一些实作方式之下,pa层至dl层的数据宽度为1个通道有4个符号和2个通道有8个符号。

[0115]

而依据unipro规范(如unipro规范说明书中关于nac帧传输的第6.6.10节(“unipro v2r.05specification(section 6.6.10nac frame transmission)”)需要在数据链路层实现错误处理(error handling),当主机与设备中任何一方(或称目标端)检测到接收的数据有错误时,发现错误的一方(或目标端)应主动向另一方(或称发起端)发送表示错误发生的通知信号,在unipro中称为“否定应答控制”(negative acknowledgment control,nac)帧,并因而触发另一方(或发起端)再传输数据。此外,在上述情景下,目标端在传输nac帧后,将禁止nac帧传输,直到dl层接收到一个没有任何错误(如无crc错误、错误的帧序列数字等)的数据帧或控制帧(如afc或nac帧)为止。也就是说,除非数据链路层检测到可以再次致能nac传输的事件,否则将禁止nac帧传输。

[0116]

因此,当pa层至dl层的数据宽度为8个符号或以上时,每个时钟周期允许有两个或以上的帧的存在,且在dl层的接收器(rx)的任何一个时钟周期内,可能会出现有正确帧及错误帧,从而影响是否要再次致能nac帧传输的次序问题。此等问题,于ufs标准中所采用unipro规范中并未提及。请参考图5a及图5b,其为在每个时钟周期允许接收多个帧的情况下产生是否要再次致能nac帧传输的次序问题示意图。在图5a、图5b或相似图式的示例中,在时间轴上的tm(m为整数)(如t0、t1~t5)分别表示一个时钟域(clock domain)中时钟的多个时钟周期;在t0、t1~t5上方对应的格子表示在相对应的时钟周期中接收到来自pa层的符号被暂时存储的符号位置(如分别记作符号0~符号7),其中在某一时钟周期来说,来自对等端(peer side)的符号0比符号7的符号来得早,在同一时钟周期内,其他符号位置的相对意义可如此类推。此外,为了方便说明,在图5a、5b或相似图式中,若某一帧的crc、sof或eof符号有误,表示有帧错误发生,在图式中所述符号的格子(如图5a或5b中某些crc符号)会以较粗的框线格式来表示。

[0117]

如图5a所示的一种情况为在nac传输被禁止后,错误帧出现在正确帧之前。在图5a中,在时钟周期t0时,包含sof、d00~d04、eof、crc符号的数据帧(以下简称d0x数据帧)的crc不正确,故dl层传输nac。此后,nac传输被禁止。在时钟周期t3时,即使包含sof、d60、eof、crc符号的数据帧(以下简称d60数据帧;以下其他数据帧亦用类似简洁方式来表示)的crc不正确,dl层也不得发送nac。如此,直至接收到正确的d70数据帧(包含sof、d70、eof、crc符号的数据帧且crc正确)后,dl层再次致能nac传输。

[0118]

如图5b所示的另一种情况为在nac传输被禁止后,错误帧出现在正确帧之后。在图5b中,在时钟周期t0时,d0x数据帧的crc不正确,故dl层传输nac。此后,nac传输被禁止。在时钟周期t3时,dl层先收到正确的d60数据帧,故dl层应再次致能nac传输,又由于d70数据帧的crc不正确表示所述数据帧有损坏,故dl层应再次传输nac。

[0119]

在图5a中的时钟周期t3的情况下,dl层不需要发送nac,但在图5b中的时钟周期t3的情况下,dl层则需要发送nac。

[0120]

在每个时钟周期允许接收多个帧的情况下,为了符合unipro规范,在实现dl层时,应确保能够在没有其他异常原因的情况下,例如rx和tx时钟域之间的硬件同步延迟的情况下,由于哪个损坏的帧而正确发送nac帧传输请求。否则,重复传输nac或错过传输nac将违反unipro规范,从而导致没有正确地向ufs系统反映真实状态。为了解决上述在每个时钟周期允许接收多个帧的情况下所出现的问题(如图5a及5b所示),前述如图1所示的用于互连协议的错误处理的方法,能够在互连协议下正确且有效率地实现错误处理中表示错误发生

的通知信号的传输,如nac帧传输。以下进一步举实施例说明。

[0121]

请参考图6,其为实现上述图1的方法的电路架构的一种实施方式的示意图。图6所示的电路架构可以将依据图1的方法实现在主机的主机控制器(12)或存储设备的设备控制器(22),例如主机及存储设备的硬件协议引擎中数据链路层(132或232)加以实现。

[0122]

如在一些实施例中,依据图6的电路架构而在数据链路层(132或232)中实现数据链路层接收器(dl rx)及数据链路层传送器(dl tx)。如图6所示,数据链路层电路300包括数据链路层接收器(dl rx)电路310及数据链路层传送器(dl tx)电路330。数据链路层接收器(dl rx)电路310包括帧接收处理单元311、nac传输处理单元315。此外,在实施例中,数据链路层接收器(dl rx)电路310及数据链路层传送器(dl tx)电路330分别实现为操作于不同时钟域的情况下,它们之间还可借由同步模块321、322、323而耦接而使彼此信号得以同步。

[0123]

帧接收处理单元311可依据unipro规范而实现关于帧接收的处理。依据图1的方法,还可将帧接收处理单元311配置为具有unipro规范以外的功能,如将帧接收处理单元311配置为用于依据每个时钟周期中出现的帧是否发生错误及错误所对应的符号位置而产生所述帧错误位置标示信号(如以nac_req_trig_sym[7:0]表示),并依据每个时钟周期中出现的帧是否正确及所对应的符号位置而产生所述帧正确位置标示信号(如以correct_frame[7:0]表示)。例如,根据m-phy具有2个通道有8个符号的实现方式,帧接收处理单元311对应地实现每个时钟周期接收来自pa层的最多8个符号数据,如利用数据缓冲器、先进先出(first-in first-out,fifo)缓冲器加以存储。帧接收处理单元311还可依据unipro规范利用逻辑电路或控制电路来实现关于数据链路层的帧接收的处理,并可还进一步实现前述unipro规范以外的功能,以产生所述帧错误位置标示信号(如nac_req_trig_sym[7:0])及产生所述帧正确位置标示信号(如correct_frame[7:0])。

[0124]

nac传输处理单元315可实现依据图1的方法的步骤s10~s30。并可进一步实现其他依据图1的方法的实施例。nac传输处理单元315(依据图1的步骤s10)接收所述帧错误位置标示信号(如以nac_req_trig_sym[7:0]表示)以及所述帧正确位置标示信号(如以correct_frame[7:0]表示)。nac传输处理单元315(依据图1的步骤s20)依据所述帧错误位置标示信号及所述帧正确位置标示信号,用以向dl tx电路330提出nac帧传输请求或提出禁止nac帧传输请求。例如,nac传输处理单元315向dl tx电路330输出多个信号至dl tx电路330,如用以提出nac帧传输请求的信号(如以eh_nac_req表示)及用以提出禁止nac帧传输请求的信号(如以nac_req_mask表示),并通过同步模块321、322而调整为sync_nac_req信号及sync_nac_req_mask信号。此外,为了令向dl tx电路330提出的nac帧传输请求或禁止nac帧传输请求正确地输出并符合unipro规范,nac传输处理单元315还用以代表dl rx电路310而与dl tx电路330进行同步交握(synchronous handshake),例如通过输出nac_req_mask并接收用以向dl rx电路310告知“禁止nac帧传输请求”的状态或遮罩(mask)是否被清除的信号(如以clr_nac_req_mask或sync_clr_nac_req_mask表示),其中dl tx电路330输出clr_nac_req_mask并通过同步模块323而调整为sync_clr_nac_req_mask。

[0125]

请参考图7,其为nac传输处理单元315的一种实施例的示意图。如图7所示,nac传输处理单元315a包括逻辑单元410、比较单元420及nac_req_mask产生单元430。如图7所示,nac传输处理单元315a(依据图1的步骤s10)接收所述帧错误位置标示信号(如以nac_req_

trig_sym[7:0]表示)以及所述帧正确位置标示信号(如以correct_frame[7:0]表示)。

[0126]

逻辑单元410依据nac_req_trig_sym[7:0]信号及eh_nac_req_pending信号进行逻辑运算而产生eh_nac_req信号。所述逻辑运算例如为基于按位或(bitwise or)运算的逻辑运算,如以式子表示如下:

[0127]

eh_nac_req=(|nac_req_trig_sym)|eh_nac_req_pending,

[0128]

其中|nac_req_trig_sym代表对nac_req_trig_sym[7:0]本身进行按位或运算。

[0129]

比较单元420依据nac_req_trig_sym[7:0]信号以及correct_frame[7:0]信号进行比较并依据sync_clr_nac_req_mask信号来确认dl rx电路310与dl tx电路330之间的同步交握是否完成,从而产生eh_nac_req_pending。

[0130]

在每个时钟周期允许接收多个帧的应用情景下,比较单元420可以配置多种的操作方式以处理各种情况,将举多个实施例并配合图8至图12说明在后。以下首先以两种情况来作举例说明。在第一种情况的示例中,有正确的帧及有错误的帧出现在某一时钟周期,即此时钟周期中nac_req_trig_sym[7:0]具有处于作用状态(asserted)的位和correct_frame[7:0]亦具有处于作用状态的位。若在第一种情况下,数据链路层电路300处于禁止nac帧传输的状态(即nac_req_mask=1)和dl rx电路310与dl tx电路330之间的同步交握尚未完成(即sync_clr_nac_req_mask=1)时,比较单元420依据nac_req_trig_sym[7:0]信号以及correct_frame[7:0]信号进行比较(如依据所述两信号对应的数值来比较或按位的运算来比较),比较结果为nac_req_trig_sym[7:0]大于correct_frame[7:0]时,表示在上述时钟周期中,就接收顺序而言,有错误的帧出现在正确的帧之后,依据unipro规范,dl rx电路310需要为这种情况向dl tx电路330提出nac帧传输请求。但由于同步交握尚未完成,故比较单元420设定一个内部信号(以eh_nac_req_pending_flag表示)为作用状态(如为1’b1(高位准)),以搁置(pending)nac帧传输请求。当所述同步交握完成后(如sync_clr_nac_req_mask由1改变为0),比较单元420令eh_nac_req_pending_flag改变为非作用状态(如为从1’b1改为1’b0(低位准))。此时,比较单元420利用eh_nac_req_pending_flag的下降缘来产生eh_nac_req_pending信号的一个时钟周期的脉波(如eh_nac_req_pending=1’b1)。请再参考图7,比较单元420输出的eh_nac_req_pending信号的一个时钟周期的脉波通过逻辑单元410向dl tx电路330提出nac帧传输请求(如eh_nac_req=1’b1)。

[0131]

在第二种情况的示例中,在某一时钟周期中只有错误的帧出现,即此时钟周期中只有nac_req_trig_sym[7:0]具有处于作用状态(asserted)的位,而correct_frame[7:0]的位皆为非作用状态的位。若在第二种情况下,数据链路层电路300处于允许提出nac帧传输请求的状态(即nac_req_mask=0),但dl rx电路310与dl tx电路330之间的同步交握尚未完成(即sync_clr_nac_req_mask=1)时,比较单元420令内部信号eh_nac_req_pending_flag=1’b1,以搁置nac帧传输请求。当所述同步交握完成后(如sync_clr_nac_req_mask由1改变为0),比较单元420令eh_nac_req_pending_flag=1’b0。此时,比较单元420利用eh_nac_req_pending_flag的下降缘来产生eh_nac_req_pending信号的一个时钟周期的脉波(如eh_nac_req_pending=1’b1)。请再参考图7,比较单元420输出的eh_nac_req_pending信号的一个时钟周期的脉波通过逻辑单元410向dl tx电路330提出nac帧传输请求(如eh_nac_req=1’b1)。

[0132]

nac_req_mask产生单元430依据correct_frame[7:0]信号以及sync_clr_nac_

req_mask信号进行运算而产生nac_req_mask信号,从而进行dl rx电路310与dl tx电路330之间的同步交握。举例而言,在某个时钟周期,nac_req_trig_sym[7:0]出现作用状态位(有错误的帧)时,nac_req_mask产生单元430令nac_req_mask=1,并通过同步模块322而调整为sync_nac_req_mask而至dl tx电路330。当dl rx电路310向dl tx电路330提出的nac帧传输请求,并且dl tx电路330真正发送出nac帧后,dl tx电路330令clr_nac_req_mask=1’b1并通过同步模块323而调整sync_clr_nac_req_mask=1’b1。

[0133]

为了解决上述在每个时钟周期允许接收多个帧的情况下所出现的问题(如图5a及5b所示),以下依据前述如图1所示的方法举例说明如何依据所述帧错误位置标示信号(如以nac_req_trig_sym[7:0]表示)以及所述帧正确位置标示信号(如以correct_frame[7:0]表示)来进行“判别错误位置”、“比较”、“决定是否搁置请求nac帧传输”的过程。

[0134]

举例而言,所述帧错误位置标示信号(如以nac_req_trig_sym[n-1:0]表示)代表为依据每个时钟周期中出现的帧是否发生错误及错误所对应的符号位置,其中n为整数代表某一个时钟周期中的允许的符号数目,例如为8或以上,在以下实施例中取n=8,而错误是否发生的条件以unipro规范来定义,如unipro规范说明书中关于nac帧传输的第6.6.10节中所指的传输nac帧所需满足的条件。所述帧正确位置标示信号(如以correct_frame[n-1:0]表示)为依据每个时钟周期中出现的帧是否正确及所对应的符号位置(如正确的crc)。请参考图8,以下举例说明在不同时钟周期时,因为帧的错误或正确的情况。

[0135]

在时钟周期t0:d0x数据帧有crc错误,所述crc符号在符号7,故nac_req_trig_sym[7:0]对应的二进位数值为10000000,被解码为16进位数值即0x80。如在图8中时钟周期t0时,nac_req_trig_sym[7:0]的波形用16进位数值“80”来示意。由于时钟周期t0中并没有正确的数据帧,故correct_frame[7:0]对应的二进位数值为00000000,16进位数值即0x00,如在图8中用“00”来示意。

[0136]

在时钟周期t3:d60数据帧有crc错误,所述crc符号在符号3,故nac_req_trig_sym[7:0]对应的二进位数值为00001000,被解码为0x08。另一方面,d70数据帧是正确的,d70数据帧的crc符号为符号7,所以correct_frame[7:0]对应的二进位数值为10000000,即是0x80。

[0137]

在时钟周期t6:d80数据帧有帧语法错误,如sof符号的错误,d90数据帧有eof语法错误。上述两个错误发生在符号0及符号6,所以nac_req_trig_sym[7:0]对应的二进位数值为01000001,被解码为0x41。由于时钟周期t6中并没有正确的数据帧,故correct_frame[7:0]对应的二进位数值为00000000,即0x00。

[0138]

在时钟周期t9:d10数据帧有eof错误,错误发生在符号2,所以nac_req_trig_sym[7:0]对应的二进位数值为00000100,被解码为0x04。另一方面,d11数据帧是正确的,d11数据帧的crc符号在符号7,所以correct_frame[7:0]为0x80。

[0139]

在时钟周期t12:d12数据帧(其为包含afc、d12、crc符号的afc帧)有crc错误,d13数据帧有帧语法错误。上述两个错误发生在符号1及符号2,所以nac_req_trig_sym[7:0]对应的二进位数值为00000110,被解码为0x06。另一方面,nac帧(其包含nac、crc符号)是正确的,d11数据帧的crc符号在符号7,所以correct_frame[7:0]为0x80。

[0140]

上面显示了识别损坏帧和正确帧位置的第一个过程“判别错误位置”。另一方面,前述图6中帧接收处理单元311依据unipro规范,并可利用如图8的示例的方式,检测帧错误

及确认正确的帧,从而产生nac_req_trig_sym及correct_frame信号。

[0141]

以下进一步举例说明“比较”、“决定是否搁置请求nac帧传输”的过程。

[0142]

依据图1的步骤s20,依据所述帧错误位置标示信号及所述帧正确位置标示信号,且在允许nac帧传输的状态下,判别出第一时钟周期中有一个帧错误发生,且请求nac帧传输之后,指示进入禁止nac帧传输的状态;例如发送请求信号来指示dl tx进入所述状态,如通过将nac_req_mask改变为作用状态(asserted)来请求dl tx。接着,依据图1的步骤s30,在所述第一时钟周期后,比较所述帧错误位置标示信号及所述帧正确位置标示信号,来根据帧错误情形而决定是否搁置请求nac帧传输。

[0143]

在一些实施例,在每个时钟周期内,可就以下几种类别的情况定出处理的方式。

[0144]

1.当只接收到正确的帧时,则清除nac_req_mask,然后再次启用nac传输。

[0145]

2.当只接收到损坏的帧时,忽略错误情况而不发送nac。

[0146]

3.当接收到正确帧和损坏帧时,dl rx将比较correct_frame[7:0]和nac_req_trig_sym[7:0]。类别3依此比较结果而有两种情况,如情况3a,若correct_frame[7:0]的值小于nac_req_trig_sym[7:0]的值,则清除nac_req_mask,搁置nac帧传输请求并在nac_req_mask被设为非作用状态(deasserted)后发送nac帧传输请求。情况3b,correct_frame[7:0]的值大于nac_req_trig_sym[7:0]的值,则清除nac_req_mask,并忽略错误情况而不发送nac。

[0147]

以下分别针对类别的情况作举例说明。

[0148]

请参考图9至图12,其显示利用图6、图7的电路架构下,依据图1的方法来处理nac传输时,在前述各种类别的情况下的处理情况,且以信号波形示意图来作举例说明。在图9中,rmmi_rx_clk代表rmmi rx时钟域的时钟信号,以按位或运算后的|nac_req_trig_sym信号来示意nac_req_trig_sym[7:0]信号,以按位或运算后的|correct_frame信号来示意correct_frame[7:0]信号。

[0149]

请参考图9,其举例说明类别1的情况定出处理的方式。请参考图9,如虚线箭号910所示意,当第一个错误发生时,dl rx(如图6的310)的nac_req_trig_sym[7:0]触发nac帧传输请求(如通过eh_nac_req信号)到dl tx(如图6的330)以发送nac。同时,如图9中虚线箭号910所示意,nac_req_mask信号被设为作用状态(asserted)(如高位准)以禁止nac帧传输。此外,前述发送nac完成后(如send_nac_done所示意),sync_clr_nac_req_mask信号被设为作用状态。

[0150]

如图9中虚线箭号920所示意,在接收到正确的帧(如|correct_frame为作用状态)后,nac_req_mask信号被设为非作用状态以通过dl tx和dl rx之间的同步交握(synchronous handshake)而启用nac传输。如图9中虚线箭号930所示意,sync_clr_nac_req_mask信号被设为非作用状态(如低位准)。

[0151]

请参考图10,其举例说明类别2的情况定出处理的方式。如图10所示,如虚线箭号1010所示意,当第一个错误发生时,dl rx(如图6的310)的nac_req_trig_sym[7:0]将触发nac帧传输请求(如通过eh_nac_req信号)到dl tx(如图6的330)以发送nac。同时,如图10中虚线箭号1010所示意,nac_req_mask信号被设为作用状态(asserted)(如高位准)以禁止nac帧传输。此外,前述发送nac完成后(如send_nac_done所示意),sync_clr_nac_req_mask信号被设为作用状态。

[0152]

当nac_req_mask仍为作用状态时,若dl rx再次接收到损坏的帧时,损坏的帧将被忽略而不发送nac。

[0153]

如图10中虚线箭号1020所示意,在接收到正确的帧(|correct_frame为作用状态)后,nac_req_mask信号被设为非作用状态以通过dl tx和dl rx之间的同步交握而启用nac传输。如图10中虚线箭号1030所示意,sync_clr_nac_req_mask信号被设为非作用状态。

[0154]

请参考图11,其举例说明类别3a的情况定出处理的方式。请参考图11,如虚线箭号1110所示意,当第一个错误发生时,dl rx(如图6的310)的nac_req_trig_sym[7:0]触发nac帧传输请求(如通过eh_nac_req信号)到dl tx(如图6的330)以发送nac。同时,如虚图11线箭号1110所示意,nac_req_mask被设为作用状态以禁止nac帧传输。

[0155]

之后,若dl rx同时接收到损坏的帧和正确的帧,eh_nac_req_pending信号被设为作用状态(eh_nac_req_pending_flag和sync_clr_nac_req_mask的组合)以在损坏的帧在正确的帧之后时触发dl tx始发送nac。

[0156]

如图11中虚线箭号1120所示意,在接收到正确的帧(|correct_frame为作用状态)后,nac_req_mask信号被设为非作用状态以通过dl tx和dl rx之间的同步交握而启用nac传输。如图11中虚线箭号1130所示意,sync_clr_nac_req_mask信号被设为非作用状态。在图11中,例如,eh_nac_req_pending_flag_d1为eh_nac_req_pending_flag延迟一个时钟周期的信号,为比较单元420内部的信号。举例而言,为了令eh_nac_req_pending信号设为作用状态(asserted),当eh_nac_req_pending_flag=0和eh_nac_req_pending_flag_d1=1时,比较单元420可以利用eh_nac_req_pending_flag_d1及eh_nac_req_pending_flag的下降缘,通过逻辑运算来产生eh_nac_req_pending信号的一个时钟周期的脉波(高位准),如图11所示。

[0157]

请参考图12,其举例说明类别3b的情况定出处理的方式。请参考图12,如虚线箭号1210所示意,当第一个错误发生时,dl rx(如图6的310)的nac_req_trig_sym[7:0]触发nac帧传输请求(如通过eh_nac_req信号)到dl tx(如图6的330)以发送nac。同时,如虚图12线箭号1210所示意,nac_req_mask被设为作用状态以禁止nac帧传输。

[0158]

之后,若dl rx同时接收到损坏的帧和正确的帧,当损坏的帧在正确的帧之前时,eh_nac_req_pending信号保持在非作用状态(如低位准)。

[0159]

如图12中虚线箭号1220所示意,在接收到正确的帧(|correct_frame为作用状态)后,nac_req_mask信号被设为非作用状态以通过dl tx和dl rx之间的同步交握而启用nac传输。如图12中虚线箭号1230所示意,sync_clr_nac_req_mask信号被设为非作用状态。

[0160]

通过上述依据图1的方法而进行“判别错误位置”、“比较”、“决定是否搁置请求nac帧传输”的过程,dl rx可以正确请求dl tx发送nac帧或不向ufs系统反映真实状态。

[0161]

此外,在上述关于主机和存储设备的实施例中,主机控制器或设备控制器中的硬件协议引擎是可以基于使用硬件描述语言(hardware description language,hdl)如verilog语言或本领域技术人员所熟悉的数字电路的任何其他设计方法的技术进行设计,并且可以基于使用现场可编程门阵列(field programmable gate array,fpga)、或特定集成电路(application specific integrated circuit,asic)或复杂可编程逻辑器件(cpld)之类的电路中的一个或多个电路来实现,亦可使用专属的电路或模块来实现。主机控制器或设备控制器(或其中的处理单元或硬件协议引擎)也可以基于微控制器、处理器、

或数字讯号处理器来实现。

[0162]

本发明在上文中已以较佳实施例揭露,然而熟习本领域的普通技术人员应理解的是,所述实施例仅用于描绘本发明,而不应解读为限制本发明的范围。应注意的是,举凡与所述实施例等效的变化与置换,均应设为涵盖于本发明的范畴内。因此,本发明的保护范围当以权利要求书所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1