一种硬件编码器流水电路的制作方法

1.本公开涉及硬件编码技术领域,更为具体来说,本公开涉及一种硬件编码器流水电路。

背景技术:

2.不断优化的视频编码标准有助于进一步提升视频图像的压缩效率,减少视频图像存储和网络传输成本代价,包括最新的avs3、av1、h.266等视频编码标准。但是,这些新的视频编码标准采用了更大的处理单元、更多的候选模式以及更高的数据依赖。这意味着新标准也具有比以往标准更高的处理复杂度,即处理视频压缩时间更长,所需要的资源更多以及产生更高的并行设计难度。特别的,在avs3视频编码标准中,对编码树单元 ctu(coding tree unit)除了支持传统的四叉树qt划分之外,还支持二叉树bt划分以及扩展四叉树eqt划分方式。以最大尺寸为128x128的ctu 为例,qt/bt/eqt的划分组合如图1所示。在编码器处理过程中,需要通过在各个尺寸(比如128x128、64x64等)中进行帧内预测、帧间预测以及模式决策等过程,才能产生最优的编码结果。显然,面对更多编码工具、更复杂的视频编码处理过程以及对超高清编码性能的更高质量的要求,对硬件编码器提出了更多的挑战。

3.目前主流的硬件视频编码器设计方案,主要以功能划分处理单元,即对某一最大尺寸ctu,分阶段完成各个主要功能,形成以处理功能优先的流水结构,如图1所示。图1中展示了avs2视频编码器硬件的流水处理电路结构,包括fetch、ime、fme、skip、preip、md、dbk/sao以及aec 等。在每个功能模块中,需要完成从最大64x64到最小4x4的处理过程(根据avs2标准规定部分尺寸到8x8)。比如,在ime阶段过程中,会提前对所有可能的帧间预测尺寸进行ime,包括64x64到8x4/4x8等,并将每个尺寸最优的结果传递给后面功能单元进行处理,同时当前ime模块开始处理下一个ctu的整像素运动估计过程。

4.事实上,这种典型的功能优先的硬件编码器流水结构已经采用了近二三十年,包括h.264/avs/avs+/h.265/avs2等硬件编码器均采用了类似的流水结构。受限于以往的硬件处理能力和硬件编码器瀑布式人工设计方法,这种结构可以平衡好设计复杂度,降低开发难度,在每一个阶段流水处理时仅需要考虑不同尺寸的相同功能设计问题,有利于一些电路复用或逻辑处理。然而,这种应用了多年的结构,也打破了视频编码标准的诸多数据依赖性,导致各个阶段不同程度的性能损失,这也是硬件视频编码器通常压缩性能比较低的关键原因。具体来说,这种结构有以下方面的缺点和不足:

5.第一,在正常的视频编码标准处理过程中,ime/fme/preip等模块在进行帧间和帧内预测时,需要依赖于周边的已经完成编码单元产生的运行矢量mv(motion vector)、最优帧内模式、最优重构像素等信息,得到性能最好的帧间和帧内预测结果,如图3所示,某个ctu由4个cu组成, cu0~cu3。在正常软件编码器过程中,cu3在进行ime/fme过程时,前面3 个cu已经完成md过程,即已经获取最优的帧内/帧间编码结果。然而,在如图1所示的传统经典ctu流水硬件电路设计中,为了能够完成对该 ctu内所有尺寸cu的当前功能,即前3个cu还没有开始md,无法获得最优的参考结果。因此,不得不采用部分原始像素或信息,或采用

模型近似的方式等得到mv和周边预测像素等信息。这些将直接导致硬件编码器性能损失。

6.第二,传统的瀑布式人为手工硬件流水设计方式,往往会导致部分功能单元过多设计,分配过多的运算资源,而有的功能单元则运算资源不够产生性能损失。比如,在监控等场景中,大部分情况物体运动比较容易预测。然而,图1所示的ime/fme在设计过程通常与md过程严格划分边界,其中ime/fme采用较大的预测范围和处理复杂度进行了可能许多不必要的运算,而后者在进行帧内预测的时候受限于运算资源无法得到更好的结果。这个问题也意味着,传统以功能优先为处理单位的方式并不能灵活调整不同功能的处理边界,对所有尺寸都采用相同或相近的功能处理策略并不能实现硬件资源和编码性能更好的平衡。

技术实现要素:

7.针对技术背景指出的现有技术中存在的缺点,本发明克服了现有技术中的以上列举的缺点,提出了一种尺寸优先的高性能硬件编码器流水电路。

8.本公开提供了一种硬件编码器流水电路,包括:用于实现多级流水编码过程的以下单元:

9.获取单元,用于从内存中获取编码信息;

10.去块效应单元,用于编码树单元处理后输出结果到ddr内存;

11.样本自适应偏置单元,用于编码树单元处理后进行滤波处理;

12.算术熵编码单元,用于熵编码压缩语法和残差;

13.多个不同尺寸且按顺序连接的编码单元,每个所述编码单元包括模式决策单元、整像素估计运算单元和分像素估计运算单元;

14.且每级流水的编码过程中按照所述尺寸顺序调用一个编码单元;

15.所述获取单元依次与多个所述编码单元、所述去块效应单元、所述样本自适应偏置单元以及所述算术熵编码单元相连接。

16.进一步,所述多多个不同尺寸且按顺序连接的编码单元的尺寸具体包括:

17.64*64、32*32、64*32、32*64、16*64以及64*16。

18.进一步,所述编码单元以及所述小尺寸编码单元还包括:

19.帧内模式预决策单元以及用于获取编码ctu的skip参考像素的skip 单元。

20.进一步,还包括:

21.模式决策划分单元,用于对当前编码树单元ctu所有尺寸决策完的最优划分模式,对所有最终的划分尺寸,按照真实的周边参考像素进行帧内编码。

22.进一步,所述模式决策单元、整像素估计运算单元和分像素估计运算单元的尺寸为小于等于当前流水所处的所述编码单元以及所述小尺寸编码单元的尺寸大小。

23.进一步,所述模式决策单元、整像素估计运算单元和分像素估计运算单元的尺寸具体为:

24.32*64、64*32、32*32、32*16、16*32、16*16、16*8、8*16或8*8 以上尺寸之一。

25.进一步,所述帧内模式预决策单元以及所述skip单元的尺寸为小于等于当前流水所处的所述编码单元以及所述小尺寸编码单元的尺寸大小。

26.进一步,所述帧内模式预决策单元以及所述skip单元的尺寸具体为:

27.32*64、64*32、32*32、32*16、16*32、16*16、16*8、8*16或8*8 以上尺寸之一。

28.本公开的有益效果为:

29.第一,本公开方案提出以尺寸优先的硬件编码器流水级处理方案,充分结合了视频编码标准处理特点以及硬件流水设计特点,能够充分保留帧内帧间预测的性能,有助于实现高性能的硬件编码器产品;

30.第二,本公开方案充分利用了基于高层次综合软件的敏捷快速评估设计方法,能够灵活的调整各流水尺寸内部的功能合并边界,尽可能实现高性能和硬件资源速度的平衡,避免了可能的人为过多设计产生的性能和资源不合理分配问题。

31.第三,本公开的方案采用了mdenc结构,有助于提升在帧内帧间尺寸编码过程中的算法灵活性,不必受限于编码标准数据依赖性,可以进一步提高处理速度,降低硬件设计和开发难度。

附图说明

32.图1示出了avs3中ctu的qt/bt/eqt划分模式的示意图;

33.图2示出了传统以功能优先的硬件编码器流水结构电路的示意图;

34.图3示出了ctu中相邻cu依赖性关系对帧内/帧间预测的影响示意图;

35.图4示出了本公开的实施例1的结构示意图;

36.图5示出了出于两个ctu流水级中某个cu单元不同功能关系;

37.图6示出了出于当前ctu流水级中某个cu单元不同功能关系。

具体实施方式

38.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

39.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

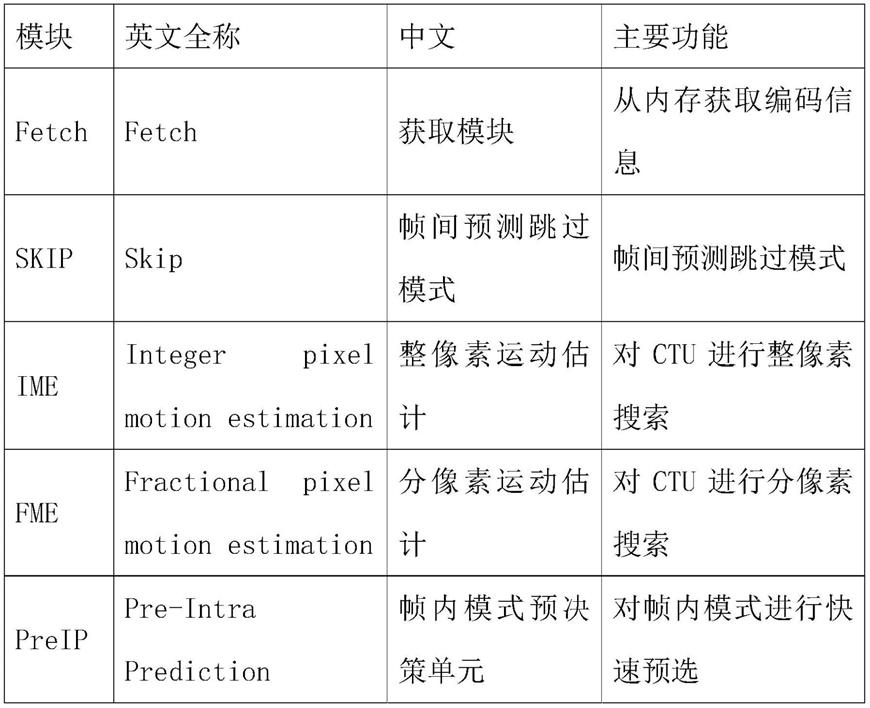

40.表1关键模块功能说明

[0041][0042][0043]

实施例一:

[0044]

如图3所示:

[0045]

本公开提供了一种硬件编码器流水电路,包括:

[0046]

用于实现多级流水编码过程的以下单元:

[0047]

获取单元,用于从内存中获取编码信息;

[0048]

去块效应单元,用于编码树单元处理后输出结果到ddr内存;

[0049]

样本自适应偏置单元,用于编码树单元处理后进行滤波处理;

[0050]

算术熵编码单元,用于熵编码压缩语法和残差;

[0051]

多个不同尺寸且按顺序连接的编码单元,每个所述编码单元包括模式决策单元、整像素估计运算单元和分像素估计运算单元;

[0052]

且每级流水的编码过程中按照所述尺寸顺序调用一个编码单元;

[0053]

所述获取单元依次与多个所述编码单元、所述去块效应单元、所述样本自适应偏置单元以及所述算术熵编码单元相连接。

[0054]

进一步,所述编码单元的尺寸具体包括:

[0055]

64*64、32*32、64*32、32*64、16*64以及64*16。

[0056]

进一步,所述编码单元以及所述小尺寸编码单元还包括:

[0057]

帧内模式预决策单元以及用于获取编码ctu的skip参考像素的skip 单元。

[0058]

进一步,还包括:

[0059]

模式决策划分单元,用于对当前编码树单元ctu所有尺寸决策完的最优划分模式,对所有最终的划分尺寸,按照真实的周边参考像素进行帧内编码。

[0060]

进一步,所述模式决策单元、整像素估计运算单元和分像素估计运算单元的尺寸为小于等于当前流水所处的所述编码单元以及所述小尺寸编码单元的尺寸大小。

[0061]

进一步,所述模式决策单元、整像素估计运算单元和分像素估计运算单元的尺寸具体为:

[0062]

32*64、64*32、32*32、32*16、16*32、16*16、16*8、8*16或8*8 以上尺寸之一。

[0063]

进一步,所述帧内模式预决策单元以及所述skip单元的尺寸为小于等于当前流水所处的所述编码单元以及所述小尺寸编码单元的尺寸大小。

[0064]

进一步,所述帧内模式预决策单元以及所述skip单元的尺寸具体为:

[0065]

32*64、64*32、32*32、32*16、16*32、16*16、16*8、8*16或8*8 以上尺寸之一。

[0066]

第一,图4中qt/bt/eqt代表当前最大64x64按照以上几种划分方式可能产生的当前层结果。可以看到,本发明方案,是将64x64 ctu划分第一层组合都作为流水节点进行处理。比如,在64x32bt中,包括64x32尺寸以及该尺寸下所有的划分可能性所需要完成的处理功能。每一级处理完结果都会传递给下一个节点进行比较,并更新最优的结果。在每一个流水节点内部,完成ime/fme/skip/preip/md等功能。这样在该节点内部的所有尺寸都可以获取到周边的最优结果,即可以充分选择的获取到最优的编码结果作为各个功能的预测参考,提升编码器性能。

[0067]

第二,由于采用了尺寸优先的流水结构,本发明方案采用基于高层次综合软件处理的方式,对每个尺寸的多个功能进行快速面积和算法性能评估,可以避免纯靠经验的硬性功能模块划分方式。具体来说,以某个流水处理内部尺寸8x8的md和fme功能为例,如图5所示,展示cu0和cu1 的关系变化。在图5中,md和fme处于两个完全独立的ctu级硬件顶层模块中,只能单独处理,这导致处于相同处理时间的cu1进行fme无法获取到周边cu0的md的结果。相比之下,在图6中,它们处于某个ctu尺寸中依次处理两个功能。根据整体综合结果,如图虚线所示,将cu0的 fme和md进行合并硬件处理,使得cu1的fme可以获取周边cu0 md之后的预测信息,这使得fme有更准确的帧间预测机会。需要说明的是,采用传统手工方法虽然理论上也可以调整顶层功能边界,但需要大量人工实现、测试和验证,无法做到使用高层次综合软件产生可以得到的快速算法和硬件速度面积评估。

[0068]

第三,由于采用尺寸优先的ctu级流水结构,意味着同时多个相邻的 ctu会同时处于在处理不同尺寸电路中。这将导致当前ctu无法获取左边和左上ctu最终的帧内最优参考像素,会产生编解码不一致问题。在尺寸流水处理实践过程,左侧和左上帧内参考像素仅使用原始像素或前一级部分重构像素。为了解决该问题,在本公开提出的方案中,增加了一级mdenc 模块。因此,当完成7级尺寸流水处理后,mdenc模块对当前ctu所有尺寸决策完的最优划分模式,对所有最终的划分尺寸,按照真实的周边参考像素进行帧内编码,最终获取符合标准规定的码流。特别地,由于使用 mdenc重整码流,将有助于提升前面尺寸决策的灵活性,可以在决策过程中使用更多快速估计算法,提高处理速度,降低设计和处理难度。

[0069]

本公开的有益效果为:

[0070]

第一,本公开方案提出以尺寸优先的硬件编码器流水级处理方案,充分结合了视频编码标准处理特点以及硬件流水设计特点,能够充分保留帧内帧间预测的性能,有助于实现高性能的硬件编码器产品;

[0071]

第二,本公开方案充分利用了基于高层次综合软件的敏捷快速评估设计方法,能够灵活的调整各流水尺寸内部的功能合并边界,尽可能实现高性能和硬件资源速度的平衡,避免了可能的人为过多设计产生的性能和资源不合理分配问题。

[0072]

第三,本公开的方案采用了mdenc结构,有助于提升在帧内帧间尺寸编码过程中的算法灵活性,不必受限于编码标准数据依赖性,可以进一步提高处理速度,降低硬件设计和开发难度。

[0073]

以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1