半导体芯片及信号发送方法与流程

1.本发明涉及一种集成电路设计,更具体地,涉及一种具有本地振荡器(local oscillator,lo)缓冲器的半导体芯片,该本地振荡器(lo)缓冲器被重新(reused)用于环回测试和/或信号发送。

背景技术:

2.环回测试(loop-back test)是用于检查通信系统的操作特性的众所周知的技术。在环回测试中,测试数据从源传出并穿过通信系统的某些部分,最后返回到源。例如,测试数据通过发送(tx)链上变频(up-converted)为射频(rf)信号,然后在通过天线发送之前循环回(loop back)接收(rx)链,rf信号在rx链上进行下变频(down-converted)以进行进一步处理。在测试数据返回后,可以观察测试数据的信息内容和/或测试数据的物理属性(例如,信号强度、信噪比和其他感兴趣的参数)并与最初发送测试数据时存在的相同信息和/或参数进行比较。可以通过对原始测试数据与返回时的测试数据的比较提取测试数据所经过的通信系统部分的状态信息和正在提供的服务质量的指示。

3.在诸如无线电检测和测距(radio detection and ranging,radar)(也即,雷达)系统的一些通信系统中,tx链位于的芯片区域远离rx链所在的芯片区域。可以在rx链附近实施测试音发生器(testing tone generator,ttg)以充当tx电路,用于提供用于测试每个rx链的测试音。但是,ttg占用的芯片面积很大,并不是一个性价比高的解决方案。

4.在诸如雷达系统的一些通信系统中,低功率扫描模式是重要特征。例如,典型的4t4r架构的radar系统在低功率扫描模式下可能只使能4t4r架构的一部分,例如1t1r或1t2r。一旦在低功率扫描模式下使能(enable)正常的tx链(1t),由于使能的块过多,tx通道(channel)会消耗大量功率。

5.因此,需要一种创新的低成本环回测试设计和/或创新的tx设计,其可适用于各种通信系统,包括雷达系统、无线保真(wi-fi)系统、蓝牙(bt)系统、第五代(5g)无线系统等。

技术实现要素:

6.本发明提供半导体芯片及信号发送方法,可将lo缓冲器重新用于发送功能。

7.本发明提供的一种半导体芯片,可包括:第一无线通信电路,包括信号路径,其中该信号路径包括混频器输入端口和与该混频器输入端口不同的信号节点;本地振荡器(lo)缓冲器;和辅助路径,被配置为将该lo缓冲器电连接到该信号路径的该信号节点,其中该lo缓冲器通过该辅助路径被重新用于发送功能。

8.本发明提供的一种发送方法,可包括:通过辅助路径将本地振荡器(lo)缓冲器电连接到无线通信电路中的信号路径的信号节点,其中,该信号路径包括该信号节点和与该信号节点不同的混频器输入端口;和通过该辅助路径将该lo缓冲器重新用于发送功能。

9.实施本发明实施例可通过该辅助路径将该lo缓冲器重新用于发送功能。

附图说明

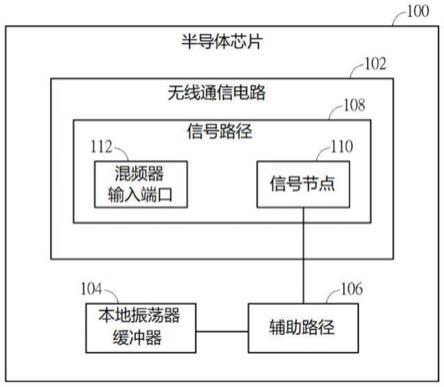

10.图1是示出根据本发明实施例的半导体芯片的框图。

11.图2是图示根据本发明的实施例的具有被重新用于环回测试的lo缓冲器的第一半导体芯片的图。

12.图3是图示根据本发明的实施例的配备有混频器功能的lo缓冲器的图。

13.图4是根据本发明实施例的在环回测试模式下具有第一配置的辅助路径的电路图。

14.图5是根据本发明实施例的正常模式下具有第二配置的辅助路径的电路图。

15.图6是图示根据本发明的实施例的具有被重新用于环回测试的lo缓冲器的第二半导体芯片的图。

16.图7是图示根据本发明的实施例的具有被重新用于环回测试的lo缓冲器的第三半导体芯片的图。

17.图8是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第一半导体芯片的图。

18.图9是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第二半导体芯片的图。

19.图10是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第三半导体芯片的图。

20.图11是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第四半导体芯片的图。

21.图12是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第五半导体芯片的图。

22.图13是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第六半导体芯片的图。

具体实施方式

23.在说明书及权利要求书当中使用了某些词汇来指称特定的组件。本领域技术人员应可理解,硬件制造商可能会用不同的名词来称呼同一个组件。本说明书及权利要求书并不以名称的差异来作为区分组件的方式,而是以组件在功能上的差异来作为区分的准则。在通篇说明书及权利要求当中所提及的“包含”及“包括”为一开放式的用语,故应解释成“包含但不限定于”。“大体上”或“大约”是指在可接受的误差范围内,本领域技术人员能够在一定误差范围内解决所述技术问题,基本达到所述技术效果。此外,“耦接”或“耦合”一词在此包含任何直接及间接的电性连接手段。因此,若文中描述一第一装置耦接于一第二装置,则代表该第一装置可直接电性连接于该第二装置,或通过其它装置或连接手段间接地电性连接至该第二装置。以下所述为实施本发明的较佳方式,目的在于说明本发明的精神而非用以限定本发明的保护范围,本发明的保护范围当视权利要求书所界定者为准。

24.接下面的描述为本发明预期的最优实施例。这些描述用于阐述本发明的大致原则而不应用于限制本发明。本发明的保护范围应在参考本发明的权利要求书的基础上进行认定。

25.图1是示出根据本发明实施例的半导体芯片的框图。半导体芯片100包括无线通信电路102、本地振荡器(lo)缓冲器104、辅助路径106和其他电路组件(未示出)。无线通信电路102包括具有混频器输入端口112和与混频器输入端口112不同的信号节点110的信号路径108。取决于实际设计考虑,无线通信电路102可以是接收(rx)电路的一部分或发送(tx)电路的一部分。因此,信号路径108可以是rx信号路径或tx信号路径。在实践中,半导体芯片100可以包括通信系统(例如radar系统、wi-fi系统、bt系统或5g无线系统)的多个rx电路和多个tx电路。在无线通信电路102是rx电路的一部分的情况下,混频器输入端口112被布置为接收下变频混频器所需的lo信号。在无线通信电路102是tx电路的一部分的另一种情况下,混频器输入端口112被布置为接收上变频混频器所需的lo信号。

26.lo缓冲器104被布置为接收和缓冲从本地振荡器生成的lo信号,并且取决于实际设计考虑可以充当tx lo缓冲器或rx lo缓冲器。即,根据实际设计考虑,lo缓冲器104被包括在可以与无线通信电路102相同或可以与无线通信电路102不同的无线通信电路中。lo缓冲器104最初被设计为向混频器(例如,下变频混频器或上变频混频器)提供lo信号。在该实施例中,辅助路径106被布置为将lo缓冲器104的输出信号电连接到信号路径108处的信号节点110,使得lo缓冲器104可以被重新用于不同的功能。例如,lo缓冲器104可重新用于环回测试功能,其中环回测试功能可在制造测试中被执行(例如,cp(电路探测或芯片探测(circuit probing or chip probing))或ft(最终测试(final test)),或者可以在正常操作期间的产品校准测试中被执行。又例如,lo缓冲器104可重新用于可在正常操作期间执行的tx功能。此外,被注入信号节点110的lo缓冲器104的输出信号可以是lo缓冲器104的最终输出或lo缓冲器104的中间输出。

27.为了更好地理解将lo缓冲器104重新用于环回测试功能和/或tx功能的所提议的设计,以下提供若干示例性设计,每一个均基于图1中所示的架构。

28.图2是图示根据本发明的实施例的具有被重新用于环回测试的lo缓冲器的第一半导体芯片的图。半导体芯片200包括两个rx电路202和204。为简洁起见,图2中仅示出了两个rx电路。实际上,半导体芯片200可以包括多个rx电路和多个tx电路。rx电路202和204可以属于相同的无线通信系统(例如,相同的radar系统)或不同的无线通信系统(例如,一个radar系统和一个非radar系统)。rx电路202和204可以在半导体芯片200中彼此相邻,但本发明不限于此。rx电路202耦合到天线201,并且包括平衡到不平衡(balanced-to-unbalanced,balun)电路(标记为“balun”)212、rx低噪声放大器(lna)214、下变频混频器216、rx模拟前端电路(标记为“rx afe”)218和rx lo缓冲器220。rx电路204耦合到天线203,并且包括平衡到不平衡电路(标记为“balun”)222、rx低噪声放大器224、下变频混频器226、rx模拟前端电路(标记为“rx afe”)228和rx lo缓冲器230。天线201和203中的每一个都可以是封装天线(aip)或板载天线(aob)。半导体芯片200采用图1所示的架构。例如,无线通信电路102由rx电路202的一部分来实现;信号路径108由rx信号路径实现,该rx信号路径包括平衡到不平衡电路212、rx lna 214、下变频混频器216和rx模拟前端电路。其中混频器输入端口112由下变频混频器216的混频器输入端口mix_in实现,信号节点110由平衡到不平衡电路212与天线201之间的信号节点n_lb实现;lo缓冲器104由rx电路204的rx lo缓冲器230实现;辅助路径106由连接在rx lo缓冲器230与信号节点n_lb之间的辅助路径206实现。应当注意,信号节点110(不同于混频器输入端口112)可以是信号路径108处的任何合适的节

点,其可以实现lo缓冲器104的重新使用。作为示例,但不限于,信号节点110可以是可以由变压器实现的平衡到不平衡电路的一个端子。

29.在本实施例中,一个rx电路204的rx lo缓冲器230可以通过辅助路径206被重新用于另一个rx电路202的环回测试。具体地,当辅助路径206被控制切断环回路径(loop-back path),rx电路204的rx lna 224、下变频混频器226和rx模拟前端电路228被使能,rx lo缓冲器230用于向下变频混频器226提供lo信号,rx电路202的rx lna 214、下变频混频器216和rx模拟前端电路218被使能,且rx lo缓冲器220用于向下变频混频器216提供lo信号;当辅助路径206被控制以使能环回路径时,rx lo缓冲器230被重新用于rx电路202的环回测试,rx电路204的rx lna 224、下变频混频器226和rx模拟前端电路228可以被禁用(disabled)以节省功率,而rx lna 214、下变频混频器216和rx模拟前端电路218保持使能状态,并且rx lo缓冲器220用于向下变频混频器216提供lo信号。由于现有的rx lo缓冲器230被重新用于rx电路202的环回测试,因此不需要额外的测试音发生器(ttg)。

30.在本发明的一些实施例中,可以被重新用于环回测试的rx lo缓冲器230可以配备有用于生成和输出lo+if(intermediate frequency,中频)信号的混频器功能,或者可以是典型的lo缓冲器,该典型的lo缓冲器没有用于生成和输出lo信号的混频器功能。图3是图示根据本发明的实施例的配备有混频器功能的lo缓冲器的图。图2所示的rx lo缓冲器230可以使用图3中所示的lo缓冲器300来实现。lo缓冲器300包括第一缓冲器级302、耦合器304和第二缓冲器级306。第一缓冲器级302支持用于生成if测试音的混频器功能。如图3所示,第一缓冲器级302包括多个晶体管m1、m2、m3、m4、m5、m6。晶体管m2和m3可用于接收由例如远离lo缓冲器300的数字模拟转换器(dac)提供的if信号st。假设从本地振荡器(未示出)生成并由第一缓冲器级302接收的lo信号的频率是79ghz。在rx lo缓冲器230由lo缓冲器300实现并且晶体管m2和m3被偏置电压禁用的情况下,环回(loop back)到rx电路202的rx信号路径的信号是79ghz信号。如果rx lo缓冲器220提供的lo信号的频率也是79ghz,则可以在下变频混频器216完成混频之后测试直流(dc)值。在rx lo缓冲器230通过lo缓冲器300实现和晶体管m2和m3用于接收if信号st(例如,2mhz正弦音)的另一种情况下,环回至rx电路202的rx信号路径的信号为79ghz+2mhz信号。如果rx lo缓冲器220提供的lo信号的频率也是79ghz,则可以通过2mhz正弦音来测试rx的总的链路增益。然而,这些仅用于说明目的,并不意味着对本发明的限制。

31.如上所述,辅助路径106被布置为将lo缓冲器104的输出信号电连接到信号节点110以允许lo缓冲器104被重新用于不同的功能(例如,环回测试或低功率发送)。作为示例而非限制,辅助路径106可以由诸如电容器之类的无源组件(passive component)、诸如晶体管之类的有源组件(active component)或其组合来实现。图4是根据本发明实施例的在环回测试模式下具有第一配置的辅助路径的电路图。图2所示的辅助路径206可以通过辅助路径400来实现,使得rx电路204的rx lo缓冲器230可以被重新用于rx电路202的环回测试。如图4所示,辅助路径400包括由基于p型金属氧化物半导体(pmos)的放大器实现的缓冲器,该放大器具有两个pmos晶体管mp1和mp2。图2所示的平衡到不平衡电路212可以通过平衡到不平衡电路402实现,其中平衡到不平衡电路402的不平衡侧的一个端子耦合到地电压gnd,平衡到不平衡电路402的不平衡侧的另一个端子用于充当信号节点n_lb与天线(例如,天线201)通信。换言之,信号节点n_lb是平衡到不平衡电路402的不平衡侧的不接地端。信号节

点n_lb可以不经由发送/接收(tr)开关而耦合到天线(例如,天线201),或可以经由tr开关耦合到天线(例如,天线201)。

32.rx lo缓冲器230可由lo缓冲器404实现,其中lo缓冲器404的一部分被使能以提供环回测试信号,而lo缓冲器404的其余部分可被禁用以节省功率。由于lo缓冲器404的其余部分被禁用,因此为简洁起见,在图4中未示出这些其余部分。更具体地,rx电路204的电路组件,包括rx lna 224、下变频混频器226、rx afe 228等,不涉及rx电路202的环回测试,故可以被禁用以节省功率。rx电路202在环回测试中涉及的电路组件,包括rx lna 214、下变频混频器216、rx afe 218等,应保持使能。

33.为了重新将rx lo缓冲器230用于环回测试,pmos晶体管mpl的源极端耦合到电源电压vdd,pmos晶体管mpl的栅极端被布置为接收来自lo缓冲器404的lo信号(例如,loi+),pmos晶体管mp1的漏极端通过例如表面波传输线t-line耦合到pmos晶体管mp2的源极端,pmos晶体管mp2的漏极端耦接至信号节点n_lb(例如平衡到不平衡电路402的不平衡侧的未接地端),且pmos晶体管mp2的栅极端耦接至偏置电压vb(~0v)。值得注意的是,当基于pmos的放大器被使能且依据lo缓冲器404的输出信号驱动信号节点n_lb时,平衡到不平衡电路402(更具体地,平衡到不平衡电路402的不平衡侧上的绕组)被重新用作基于pmos的放大器的输出负载。换言之,基于pmos的放大器重新使用输入平衡到不平衡电路匹配作为放大器负载来充当高频放大器。

34.当rx电路204在正常模式下操作时,rx lo缓冲器230需要向下变频混频器226提供lo信号。辅助电路206可以被控制以切断rx电路202和204之间的环回路径。图5是根据本发明实施例的正常模式下具有第二配置的辅助路径的电路图。当图2所示的辅助路径206由辅助路径400实现,rx电路204的一部分可由rx电路406实现,而rx lo缓冲器230可由lo缓冲器404实现时,整个lo缓冲器404被使能以向由同相(i)混频器和正交(q)混频器组成的下变频混频器提供所需的lo输入{loi+,loi-,loq+,loq-}。更具体地,rx电路204的电路组件,包括rx lna 224、下变频混频器226、rx afe 228、rx lo缓冲器230等在rx电路204的正常rx操作中涉及到的电路应被使能。

35.为了切断环回路径,pmos晶体管mp1的源极端耦接至电源电压vdd和pmos晶体管mp1的漏极端,而pmos晶体管mp2的栅极端耦接至电源电压vdd和pmos晶体管mp2的源极端。因此,pmos晶体管mp1被配置为mos电容器,并且pmos晶体管mp2被关断(turned off)。

36.在图2所示的实施例中,一个rx电路的rx lo缓冲器被重新用于另一个rx电路的环回测试。然而,这仅用于说明目的,并不意味着对本发明的限制。图6是图示根据本发明的实施例的具有被重新用于环回测试的lo缓冲器的第二半导体芯片的图。半导体芯片600包括与天线203耦合且属于无线通信系统(例如radar系统或非radar系统)的rx电路602。半导体芯片600采用图1所示的架构,例如,无线通信电路102由rx电路602的一部分来实现;信号路径108由rx信号路径实现,该rx信号路径包括平衡到不平衡电路222、rx lna 224、下变频混频器226和rx模拟前端电路228,其中混频器输入端口112通过下变频混频器226的混频器输入端口mix_in实现。信号节点110由平衡到不平衡电路222与天线203之间的信号节点n_lb实现;lo缓冲器104由rx电路602的rx lo缓冲器230实现;辅助路径106由耦接在rx lo缓冲器230与信号节点n_lb之间的辅助路径606实现。在该实施例中,rx lo缓冲器230可以由没有混频器功能的典型lo缓冲器实现,并且辅助路径606可以由诸如图4-5中所示的基于pmos

的放大器的辅助路径400实现。因此,辅助路径606可以包括耦合在rx lo缓冲器230和平衡到不平衡电路222的不平衡侧上的未接地端子之间的基于pmos的放大器。

37.为简洁起见,图6中仅示出了一个rx电路。实际上,半导体芯片600可以包括多个rx电路和多个tx电路。

38.在本实施例中,rx电路602的rx lo缓冲器230可以通过辅助路径606被重新用于同一个rx电路602的环回测试。具体地,当辅助路径606被控制切断环回路径,rx电路602的rx lna 224、下变频混频器226和rx模拟前端电路228被使能,rx lo缓冲器230用于提供lo信号给下变频混频器226;当辅助路径606被控制以使能环回路径时,rx电路602的rx lna 224、下变频混频器226和rx模拟前端电路228保持使能,并且rx lo缓冲器230用于提供lo信号提供给下变频混频器226,并且rx lo缓冲器230还通过向信号节点n_lb提供lo信号来被重新用于rx电路602的环回测试。由于现有的rx lo缓冲器230被重新用于rx电路602的环回测试,因此不需要额外的测试音发生器(ttg)。

39.图7是图示根据本发明的实施例的具有被重新用于环回测试的lo缓冲器的第三半导体芯片的图。半导体芯片700包括tx电路702和rx电路202。为简洁起见,图7中仅示出了一个rx电路和一个tx电路。实际上,半导体芯片700可以包括多个rx电路和多个tx电路。tx电路702和rx电路202可以属于相同的无线通信系统(例如,radar系统)或不同的无线通信系统(例如,一个radar系统和一个非radar系统)。tx电路702耦合到天线(例如,aip或aob)701,并且包括平衡到不平衡电路(标记为“balun”)722、tx功率放大器(pa)电路724(其可以包括一个或多个pa级)、上变频混频器726、tx模拟前端电路(标记为“tx afe”)728和tx lo缓冲器730。半导体芯片700采用图1所示的架构。例如,无线通信电路102由rx电路202的一部分实现;信号路径108由rx信号路径实现,该rx信号路径包括平衡到不平衡电路212、rx lna 214、下变频混频器216和rx模拟前端电路218,其中混频器输入端口112由下变频混频器216的混频器输入端口mix_in实现,信号节点110由平衡到不平衡电路212与天线201之间的信号节点n_lb实现;lo缓冲器104由tx电路702的tx lo缓冲器730实现;辅助路径106由耦合在tx lo缓冲器730与信号节点n_lb之间的辅助路径706实现。tx lo缓冲器730可以由没有混频器功能的典型lo缓冲器实现,或者可以由具有混频器功能的所提议的lo缓冲器(例如图3中所示的lo缓冲器300)实现。辅助路径706可以由基于pmos的放大器来实现,例如图4-5中所示的辅助路径400。因此,辅助路径706可以包括耦合在tx lo缓冲器730和平衡到不平衡电路212的不平衡侧上的未接地端子之间的基于pmos的放大器。

40.在本实施例中,tx电路702的tx lo缓冲器730可以通过辅助路径706被重新用于rx电路202的环回测试。具体地,当辅助路径706被控制切断环回路径时,rx电路202的rx lna 214、下变频混频器216和rx模拟前端电路218被使能,rx lo缓冲器220用于向下变频混频器216提供lo信号,tx电路702的tx pa电路724、上变频混频器726和tx模拟前端电路728被使能,tx lo缓冲器730用于向上变频混频器726提供lo信号;当辅助路径706被控制以使能环回路径时,tx lo缓冲器730被重新用于rx电路202的环回测试,tx电路702的tx pa电路724、上变频混频器726和tx模拟前端电路728可以被禁用以节省功率,并且rx电路202的rx lna 214、下变频混频器216和rx模拟前端电路218可以被禁用以节省功率。由于现有的tx lo缓冲器730被重新用于rx电路202的环回测试,因此不需要额外的测试音发生器(ttg)。

41.在以上实施例中,lo缓冲器(例如,rx lo缓冲器或tx lo缓冲器)被重新用于环回

测试功能。实际上,将lo缓冲器重新用于不同于环回功能的功能是可行的。与普通的tx链相比,lo缓冲器可被视为用于生成和输出具有lo频率的rf信号的低功率发送器。因此,重新使用lo缓冲器(例如,rx lo缓冲器或tx lo缓冲器)的相同概念可适用于低功率tx应用。例如,采用重新使用lo缓冲器的提议设计的低功率tx应用可以是调频连续波形(fmcw)雷达系统的低功率扫描模式(或低功率短距离扫描模式)。又例如,辅助路径可以被用于环回功能,也可以被重新用于低功率tx功能。

42.图8是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第一半导体芯片的图。半导体芯片800包括两个rx电路802和804。为简洁起见,图8中仅示出了两个rx电路。实际上,半导体芯片800可以包括多个rx电路和多个tx电路。rx电路802和804可以在半导体芯片800中彼此相邻,但本发明不限于此。rx电路802和804可以属于相同的无线通信系统(例如,radar系统)或不同的无线通信系统(例如,一个radar系统和一个非radar系统)。rx电路802耦合到天线(例如,aip或aob)801,并且包括平衡到不平衡电路(标记为“balun”)812、rx lna 814、下变频混频器816、rx模拟前端电路(标记为“rx afe”)818和rx lo缓冲器820。rx电路804耦合到天线(例如,aip或aob)803,并且包括平衡到不平衡电路(标记为“balun”)822,rx lna 824、下变频混频器826、rx模拟前端电路(标记为“rx afe”)828和rx lo缓冲器830。半导体芯片800采用图1所示的架构。例如无线通信电路102由rx电路802的一部分来实现;信号路径108由rx信号路径实现,该rx信号路径包括平衡到不平衡电路812、rx lna 814、下变频混频器816和rx模拟前端电路818,其中混频器输入端口112由下变频混频器816的混频器输入端口mix_in实现,信号节点110由平衡到不平衡电路812与天线801之间的信号节点n_lb实现;lo缓冲器104由rx电路804的rx lo缓冲器830实现;辅助路径106是由耦合在rx lo缓冲器830与信号节点n_lb之间的辅助路径806实现。rx lo缓冲器730可由具有混频器功能的提议的lo缓冲器实现,例如图3中所示的lo缓冲器300。辅助路径806可以由基于pmos的放大器实现,例如图4-5中所示的辅助路径400。因此,辅助路径806可以包括耦合在rx lo缓冲器830和平衡到不平衡电路812的不平衡侧上的未接地端子之间的基于pmos的放大器。

43.在该实施例中,rx电路804的rx lo缓冲器830可以通过辅助路径806和天线801被重新用于tx模式。具体地,当辅助路径806被控制切断tx路径时,rx电路804的rx lna 824、下变频混频器826和rx模拟前端电路828被使能,rx lo缓冲器830用于提供lo信号给下变频混频器826、rx电路802的rx lna 814、下变频混频器816和rx模拟前端电路818被使能,rx lo缓冲器820用于提供lo信号给下变频混频器816;当辅助路径806被控制以使能tx路径时,rx lo缓冲器830被重新用于tx模式,rx电路802的rx lna 814、下变频混频器816和rx模拟前端电路818可被禁用以节省功率,且rx电路804的rx lna 824、下变频混频器826和rx模拟前端电路828可以被禁用以节省功率。这使得该方案特别适用于低功耗tx应用,因为可以禁用许多电路以保持低功耗。天线801被低功率tx功能重用,以传送rx lo缓冲器830生成的输出信号(也即低功率发送机生成的rf信号,例如,具有(lo+if)频率的信号)。在一些实施例中,当天线801被低功率tx功能重新使用时,可以在rx电路802的rx输入中集成tr开关以增加关闭模式rx阻抗以提高tx功率。

44.图9是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第二半导体芯片的图。半导体芯片900包括耦合到天线(例如,aip或aob)901并且属于无线通信系统

824、下变频混频器826和rx模拟前端电路828被使能,rx lo缓冲器830用于提供lo信号给下变频混频器826、tx电路1002的tx pa电路1014、上变频混频器1016和tx模拟前端电路1018被使能,tx lo缓冲器1020用于提供lo信号给上变频混频器1016;当辅助路径1006被控制以使能tx路径时,rx lo缓冲器830被重新用于tx模式,tx电路1002的tx pa电路1014、上变频混频器1016和tx模拟前端电路1018可以被禁用以节省功率,且rx电路804的rx lna 824、下变频混频器826和rx模拟前端电路828可以被禁用以节省功率。这使得该方案特别适用于低功耗tx应用,因为可以禁用许多电路以保持低功耗。天线1001被低功率tx功能重用,以传送rx lo缓冲器830生成的输出信号(即低功率发送机生成的rf信号,例如,具有(lo+if)频率的信号)。在一些实施例中,当天线1001被低功率tx功能重新使用时,可以在tx电路1002的tx输出中集成tr开关以增加关闭模式tx阻抗以提高tx功率。

48.图11是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第四半导体芯片的图。半导体芯片1100包括耦合到天线801的rx电路802和耦合到天线1101的tx电路1102。为简洁起见,图11中仅示出一个rx电路和仅一个tx电路。实际上,半导体芯片1100可以包括多个rx电路和多个tx电路。rx电路802和tx电路1102可以属于相同的无线通信系统(例如,radar系统)或不同的无线通信系统(一个radar系统和一个非radar系统)。半导体芯片1100采用图1所示的架构。例如无线通信电路102由rx电路802的一部分来实现;信号路径108由rx信号路径实现,该rx信号路径包括平衡到不平衡电路812、rx lna 814、下变频混频器816和rx模拟前端电路818,其中混频器输入端口112由下变频混频器816的混频器输入端口mix_in实现,信号节点110由平衡到不平衡电路812与天线801之间的信号节点n_lb实现;lo缓冲器104由tx电路1102的tx lo缓冲器1020实现;辅助路径106由耦接在tx lo缓冲器1020与信号节点n_lb之间的辅助路径1106实现。tx lo缓冲器1020可由具有混频器功能的提议的lo缓冲器来实现,例如图3中所示的lo缓冲器300。辅助路径1106可以由基于pmos的放大器来实现,例如图4-5中所示的辅助路径400。因此,辅助路径1106可以包括耦合在tx lo缓冲器1020和平衡到不平衡电路812的不平衡侧上的未接地端子之间的基于pmos的放大器。

49.在该实施例中,tx电路1102的tx lo缓冲器1020可以通过辅助路径1106和天线801被重新用于tx模式。具体地,当辅助路径1106被控制切断tx路径时,rx电路802的rx lna 814、下变频混频器816和rx模拟前端电路818被使能,rx lo缓冲器820用于提供lo信号给下变频混频器816,tx电路1102的tx pa电路1014、上变频混频器1016和tx模拟前端电路1018被使能,tx lo缓冲器1020用于提供lo信号给上变频混频器1016;当辅助路径1106被控制以使能tx路径时,tx lo缓冲器1020被重新用于tx模式,rx电路802的rx lna814、下变频混频器816和rx模拟前端电路818可被禁用以节省功率,且tx电路1102的tx pa电路1014、上变频混频器1016和tx模拟前端电路1018可以被禁用以节省功率。这使得该方案特别适用于低功耗tx应用,因为可以禁用许多电路以保持低功耗。天线801被低功率tx功能重用,以传送tx lo缓冲器1020生成的输出信号(即低功率发送机生成的rf信号,例如,具有(lo+if)频率的信号)。在一些实施例中,当天线801被低功率tx功能重新使用时,可以在rx电路802的rx输入中集成tr开关以增加关闭模式rx阻抗以提高tx功率。

50.图12是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第五半导体芯片的图。半导体芯片1200包括耦合到天线(例如,aip或aob)1201并且属于无线通信

系统(例如,radar系统或非radar系统)的tx电路1202。为简洁起见,图12中仅示出了一个tx电路。实际上,半导体芯片1200可以包括多个rx电路和多个tx电路。半导体芯片1200采用图1所示的架构。例如无线通信电路102由tx电路1202的一部分实现;信号路径108由包括平衡到不平衡电路1012、tx pa电路1014、上变频混频器1016和tx模拟前端电路1018的tx信号路径实现,其中混频器输入端口112由上变频混频器1016的混频器输入端口mix_in实现,信号节点110由平衡到不平衡电路1012与天线1201之间的信号节点n_lb实现;lo缓冲器104由tx电路1202的tx lo缓冲器1020实现;辅助路径106由耦接在tx lo缓冲器1020与信号节点n_lb之间的辅助路径1206实现。tx lo缓冲器1020可由具有混频器功能的提议的lo缓冲器来实现,例如图3中所示的lo缓冲器300。辅助路径1206可以由基于pmos的放大器来实现,例如图4-5中所示的辅助路径400。因此,辅助路径1206可以包括耦合在tx lo缓冲器1020和平衡到不平衡电路1012的不平衡侧上的未接地端子之间的基于pmos的放大器。

51.在该实施例中,tx电路1202的tx lo缓冲器1020可以通过辅助路径1206和天线1201被重新用于tx模式。具体地,当辅助路径1206被控制切断tx路径时,tx电路1202的tx pa电路1014、上变频混频器1016和tx模拟前端电路1018被使能,tx lo缓冲器1020用于提供lo信号给上变频混频器1016;当辅助路径1206被控制以使能tx路径时,tx lo缓冲器1020被重新用于tx模式,并且tx电路1202的tx pa电路1014、上变频混频器1016和tx模拟前端电路1018可以被禁用以节省功率。这使得该方案特别适用于低功耗tx应用,因为可以禁用许多电路以保持低功耗。天线1201由低功率tx功能重用,以传送tx lo缓冲器1020生成的输出信号(即低功率发送机生成的rf信号,例如,具有(lo+if)频率的信号)。在一些实施例中,当天线1201被低功率tx功能重新使用时,可以在tx电路1202的tx输出中集成tr开关以增加关闭模式tx阻抗以提高tx功率。

52.图13是图示根据本发明的实施例的具有被重新用于tx模式的lo缓冲器的第六半导体芯片的图。半导体芯片1300包括两个tx电路1002和1302。为简洁起见,图13中仅示出两个tx电路。实际上,半导体芯片1300可以包括多个rx电路和多个tx电路。tx电路1002和1302可以属于相同的无线通信系统(例如,radar系统)或不同的无线通信系统(例如,一个radar系统和一个非radar系统)。tx电路1002和1302可以在半导体芯片1300中彼此相邻,但本发明不限于此。tx电路1302耦合到天线(例如,aip或aob)1301,并且包括平衡到不平衡电路(标记为“balun”)1312、tx pa电路1314(其可以包括一个或多个pa级)、上变频混频器1316、tx模拟前端电路(标记为“tx afe”)1318和tx lo缓冲器1320。半导体芯片1300采用图13所示的架构。例如无线通信电路102由tx电路1002的一部分来实现;信号路径108由包括平衡不平衡电路1012、tx pa电路1014、上变频混频器1016和tx模拟前端电路1018的tx信号路径实现,其中混频器输入端口112由上变频混频器1016的混频器输入端口mix_in实现。信号节点110由平衡到不平衡电路1012与天线1001之间的信号节点n_lb实现;lo缓冲器104由tx电路1302的tx lo缓冲器1320实现;辅助路径106是由耦接在tx lo缓冲器1320与信号节点n_lb之间的辅助路径1306实现。tx lo缓冲器1320可由具有混频器功能的提议的lo缓冲器来实现,例如图3中所示的lo缓冲器300。辅助路径1306可以由基于pmos的放大器来实现,例如图4-5中所示的辅助路径400。因此,辅助路径1306可以包括耦合在tx lo缓冲器1320和平衡到不平衡电路1012的不平衡侧上的未接地端子之间的基于pmos的放大器。

53.在该实施例中,tx电路1302的tx lo缓冲器1320可以通过辅助路径1306和天线

1001被重新用于tx模式。具体地,当辅助路径1306被控制以切断tx路径时,tx电路1002的tx pa电路1014、上变频混频器1016和tx模拟前端电路1018被使能,tx lo缓冲器1020用于提供lo信号给上变频混频器1016,tx电路1302的tx pa电路1314,上变频混频器1316和tx模拟前端电路1318被使能,tx lo缓冲器1320用于提供lo信号给上变频混频器1316;当辅助路径1306被控制以使能tx路径时,tx lo缓冲器1320被重新用于tx模式,tx电路1302的tx pa电路1314、上变频混频器1316和tx模拟前端电路1318可以被禁用以节省功率,且tx电路1002的tx pa电路1014、上变频混频器1016和tx模拟前端电路1018可以被禁用以节省功率。这使得该方案特别适用于低功耗tx应用,因为可以禁用许多电路以保持低功耗。天线1001被低功率tx功能重用,以传送tx lo缓冲器1320生成的输出信号(即低功率发送机生成的rf信号,例如,具有(lo+if)频率的信号)。在一些实施例中,当天线1001被低功率tx功能重新使用时,可以在tx电路1002的tx输出中集成tr开关以增加关闭模式tx阻抗以提高tx功率。

54.本发明虽以较佳实施例揭露如上,然其并非用以限定本发明的范围,任何本领域技术人员,在不脱离本发明的精神和范围内,当可做些许的更动与润饰,因此本发明的保护范围当视权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1