一种发送端芯片、接收端芯片、显示控制系统及显示设备的制作方法

本发明涉及显示,尤其涉及一种发送端芯片、接收端芯片、显示控制系统及显示设备。

背景技术:

1、随着显示屏技术的不断发展,市场上存在多种类型的显示屏,其中,发光二极管(light-emitting diode,led)显示屏具有亮度高、寿命长、使用和维护简便、显示效果丰富等特点。采用led显示屏的多类大型显示设备,可广泛应用于车站、港口、户外广告、大型文体会馆、政府公告等场所。此外,采用led显示屏的中小型显示设备,例如会议屏幕、家用电视机、车载屏幕等,也有较为广泛的应用。传统的led显示屏的架构包括视频处理、控制器、发送端芯片、接收芯片,这种带来体积过大,成本过高等问题,且现有led灯的发送端芯片及接收芯片体积较大。现有led显示控制系统存在驱动芯片体积过大导致led灯间距无法减小的问题。

技术实现思路

1、为了解决上述技术问题,本发明实施例提供了一种发送端芯片、接收端芯片、显示控制系统及显示设备。

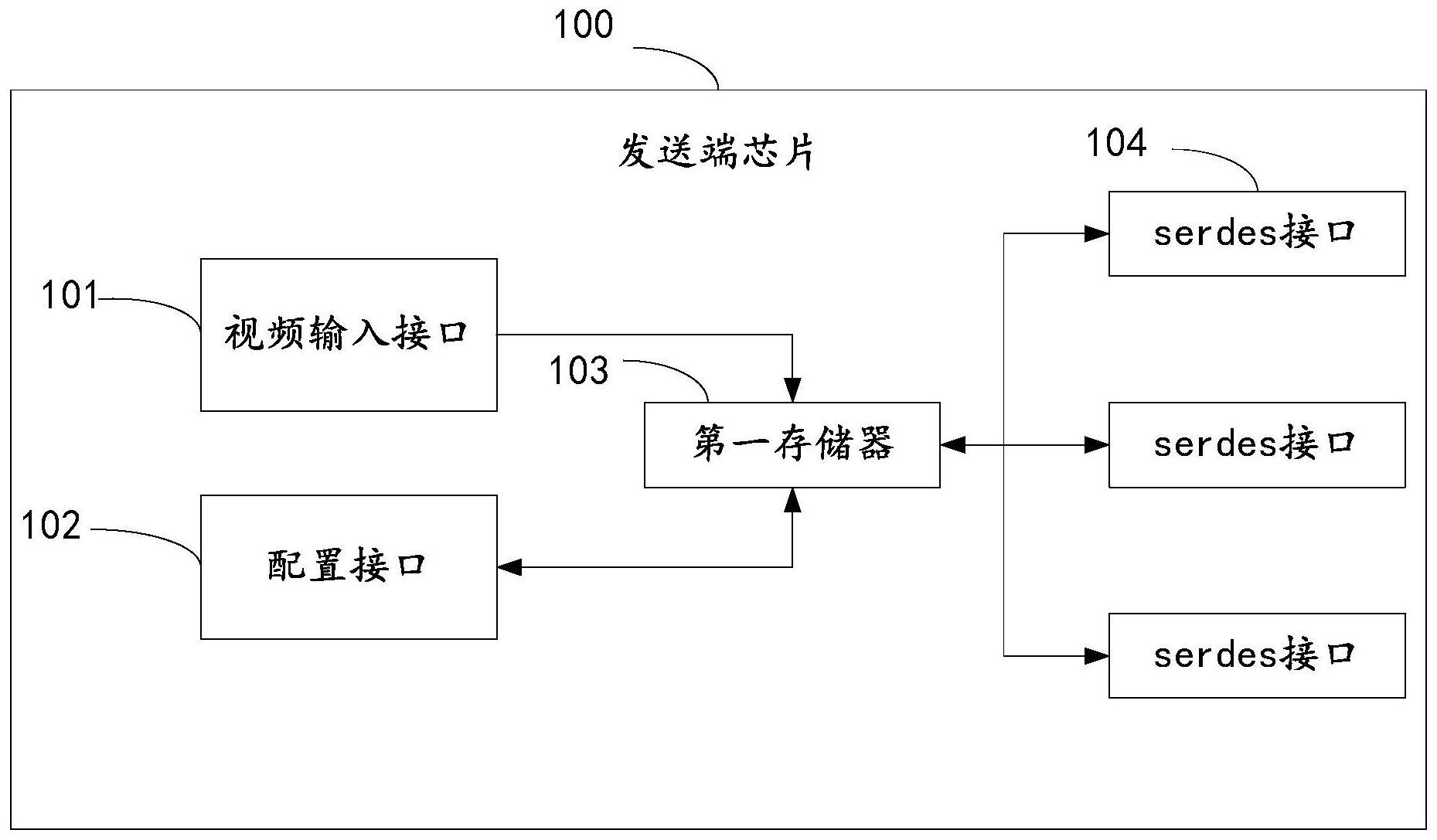

2、第一方面,本发明实施例提供了一种发送端芯片,包括第一存储器及与所述第一存储器分别连接的视频输入接口、配置接口及多个serdes接口,各serdes接口与对应的一接收端芯片连接;

3、所述视频输入接口,用于获取视频数据,将所述视频数据写入所述第一存储器;

4、配置接口,用于获取存储显示器件的配置参数,将所述配置参数写入所述第一存储器;

5、所述第一存储器,用于将所述视频数据划分为多个子视频数据;

6、各serdes接口,用于从所述第一存储器读取对应的子视频数据及所述配置参数,将读取的子视频数据及所述配置参数分配至对应的一接收端芯片。

7、可选的,各serdes接口包含均衡模块及时钟恢复模块;

8、所述均衡模块,用于在低速并行数据通过通信协议层后,对所述低速并行数据进行加扰及比特位转换编码处理,得到转换后的并行数据,并将转换后的并行数据写入先入先出队列,通过串行器将转换后的并行数据转换为串行差分信号,通过均衡器对所述串行差分信号进行均衡化处理,得到均衡化串行差分信号;

9、所述时钟恢复模块,用于通过均衡器对所述均衡化串行差分信号进行补偿,得到修正串行差分信号,对所述修正串行差分信号进行数据时钟恢复,得到时钟信号,将所述时钟信号输入解串器,通过所述解串器根据所述时钟信号对所述修正串行差分信号进行转换处理,得到并行数据,对所述并行数据进行解扰及比特位转换解码处理,得到解码后的并行数据。

10、第二方面,本发明实施例提供接收端芯片,包括主serdes接口、第二存储器、低压差分信号接口及与所述第二存储器连接的视频输出接口,所述视频输出接口,还用于与显示器件连接;

11、所述主serdes接口分别与所述第二储存器、及权利要求1或2所述发送端芯片对应的一serdes接口连接;

12、所述主serdes接口,用于从所述发送端芯片获取对应的子视频数据及配置参数,并将所述子视频数据及所述配置参数写入所述第二存储器;

13、所述视频输出接口,用于从所述第二存储器读取对应的子视频数据及配置参数,向低压差分信号接口输入所述子视频数据及所述配置参数;

14、所述低压差分信号接口,用于将所述子视频数据及所述配置参数输入显示驱动芯片,以通过所述显示驱动芯片产生所述目标电流,所述目标电流用于驱动所述显示器件显示所述子视频数据。

15、可选的,所述接收端芯片包括多个辅serdes接口,各辅serdes接口分别与所述主serdes接口及对应的一其他接收端芯片连接。

16、第三方面,本发明实施例提供了一种显示控制系统,包括:

17、显示器件、第一方面提供的发送端芯片、及多个第二方面提供的接收端芯片;

18、所述发送端芯片的各serdes接口对应连接于一接收端芯片的主serdes接口;

19、多个所述接收端芯片与所述显示器件连接。

20、可选的,各所述接收端芯片的辅serdes接口对应连接于一其他接收端芯片,多个所述接收端芯片构成级联连接。

21、可选的,处于同一级联层的相邻接收端芯片的上一接收端芯片的一辅serdes接口与下一接收端芯片的一辅serdes接口相连接;

22、在多个所述接收端芯片存在从所述发送端芯片或上一级联层对应的接收端芯片获取子视频数据及配置参数失败的目标接收端芯片时,所述目标接收端芯片,用于从与其相连接的接收端芯片获取对应的子视频数据及配置参数。

23、可选的,所述第一存储器和/或所述第二存储器为ddr或sdram。

24、可选的,所述视频输入接口包括hdmi接口、dp接口、dvi接口、sdi接口、vga接口;所述视频输出接口包括lvds接口及hub接口。

25、可选的,所述显示器件包括:led灯板和/或led屏幕。

26、第四方面,本发明实施例提供了一种显示控制方法,应用于第三方面提供的显示控制系统,所述方法包括:

27、发送端芯片的视频输入接口获取视频数据,将所述视频数据写入所述发送端芯片的第一存储器;

28、所述发送端芯片的配置接口获取存储显示器件的配置参数,将所述配置参数写入所述第一存储器;

29、所述发送端芯片的第一存储器将所述视频数据划分为多个子视频数据;

30、所述发送端芯片的各serdes接口从所述第一存储器读取对应的子视频数据及所述配置参数,将读取的子视频数据及配置参数分配至对应的一接收端芯片;

31、接收端芯片的主serdes接口从所述发送端芯片获取对应的子视频数据及配置参数,并将所述子视频数据及所述配置参数写入所述第二存储器;

32、所述接收端芯片的视频输出接口从所述第二存储器读取对应的子视频数据及配置参数,向低压差分信号接口输入所述子视频数据及所述配置参数;

33、所述接收端芯片的低压差分信号接口,用于将所述子视频数据及所述配置参数输入显示驱动芯片,以通过所述显示驱动芯片产生所述目标电流,所述目标电流用于驱动所述显示器件显示所述子视频数据。

34、可选的,所述方法还包括:

35、在多个所述接收端芯片存在从所述发送端芯片或上一级联层对应的接收端芯片获取子视频数据及配置参数失败的目标接收端芯片时,所述目标接收端芯片从与其相连接的接收端芯片获取对应的子视频数据及配置参数。

36、第五方面,本发明实施例提供了一种显示设备,包括第三方面提供的显示控制系统。

37、上述本申请提供的发送端芯片、接收端芯片、显示控制系统及显示设备,发送端芯片、接收端芯片通过集成多个serdes接口,提高通信速率,增加通信带宽,减小发送端芯片接口数量,从而减小发送端芯片体积,解决led灯间距无法减小的问题,增加带载led点数。

技术特征:

1.一种发送端芯片,其特征在于,包括第一存储器及与所述第一存储器分别连接的视频输入接口、配置接口及多个serdes接口,各serdes接口与对应的一接收端芯片连接;

2.根据权利要求1所述的发送端芯片,其特征在于,各serdes接口包含均衡模块及时钟恢复模块;

3.一种接收端芯片,其特征在于,包括主serdes接口、第二存储器、低压差分信号接口及与所述第二存储器连接的视频输出接口,所述视频输出接口,还用于与显示器件连接;

4.根据权利要求3所述的显示控制系统,其特征在于,所述接收端芯片包括多个辅serdes接口,各辅serdes接口分别与所述主serdes接口及对应的一其他接收端芯片连接。

5.一种显示控制系统,其特征在于,包括:

6.根据权利要求5所述的显示控制系统,其特征在于,各所述接收端芯片的辅serdes接口对应连接于一其他接收端芯片,多个所述接收端芯片构成级联连接。

7.根据权利要求6所述的显示控制系统,其特征在于,处于同一级联层的相邻接收端芯片的上一接收端芯片的一辅serdes接口与下一接收端芯片的一辅serdes接口相连接;

8.根据权利要求5所述的显示控制系统,其特征在于,所述第一存储器和/或所述第二存储器为ddr或sdram。

9.根据权利要求5所述的显示控制系统,其特征在于,所述视频输入接口包括hdmi接口、dp接口、dvi接口、sdi接口、vga接口;所述视频输出接口包括lvds接口及hub接口。

10.根据权利要求5所述的显示控制系统,其特征在于,所述显示器件包括:led灯板和/或led屏幕。

11.一种显示控制方法,其特征在于,应用于如权利要求5-10任一项所述的显示控制系统,所述方法包括:

12.根据权利要求11所述的方法,其特征在于,所述方法还包括:

13.一种显示设备,其特征在于,包括如权利要求5-10任一项所述的显示控制系统。

技术总结

本申请实施例提供了一种发送端芯片、接收端芯片、显示控制系统及显示设备,其中发送端芯片包括:第一存储器及与第一存储器分别连接的视频输入接口及多个SERDES接口,各SERDES接口与对应的一接收端芯片连接;视频输入接口,用于获取视频数据,将视频数据写入第一存储器;第一存储器,用于存储显示器件的配置参数、及将视频数据划分为多个子视频数据;各SERDES接口,用于从第一存储器读取对应的子视频数据及配置参数,将读取的子视频数据及配置参数分配至对应的一接收端芯片。通过所提供的发送端芯片、接收端芯片分别集成多个SERDES接口,减小芯片体积,解决LED灯间距无法减小的问题,增加带载LED点数。

技术研发人员:冉峰,戴浩,黄忻杰,季渊

受保护的技术使用者:无锡唐古半导体有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!