交织器、解交织器、及其执行的方法与流程

1.本发明涉及通信技术领域,具体地涉及一种交织器、解交织器、及其执行的方法。

背景技术:

2.在无线通信系统中,交织器和解交织器是通信系统中一个重要的模块,对系统性能的影响较大。交织器通是对输入的原始信息序列进行一定规则的置换后从前向后读出。传统的交织器主要包括:行进列出(列进行出)矩阵交织器。这样的方式实现起来比较简单,但是适用范围不够广,例如不太适用于啁啾扩频(chirp spread spectrum,css)调制系统。另外还可以包括循环对角交织器。但是该交织方法的交织深度与编码速率和扩频因子有关,内存利用效率较低。

技术实现要素:

3.本发明实施例的目的是提供一种交织器、解交织器、及其执行的方法,该交织器、解交织器、及其执行的方法适用范围广泛,易于实现,随机性强。

4.为了实现上述目的,本发明实施例提供一种交织器的执行方法,该方法包括:根据交织深度,接收原始输入数据;获取交织步长;从所述原始输入数据的第一比特数据开始,以所述交织步长为间隔,对所述原始输入数据中的所有数据进行多轮非重复读取,以得到所交织的数据;以及输出所交织的数据。

5.优选地,所述交织步长与扩频因子范围内所有扩频因子的最大公约数为1。

6.优选地,所述根据交织深度,接收原始输入数据包括:接收原始输入数据,以使得所接收的原始输入数据的长度小于或等于所述交织深度。

7.优选地,所述交织深度通过以下方法确定:确定所述交织器的内存;使用所述交织器的内存除以当前需要的扩频因子,得到第一余数;使用所述交织器的内存减去所述第一余数,得到所述交织深度。

8.优选地,所述交织器的内存满足以下条件:所述交织器的内存除以扩频因子范围内所有扩频因子,得到的第二余数均小于或等于第一阈值;所述交织器的内存除以所述原始输入数据的编码长度,得到的第三余数小于或等于所述第一阈值;所述交织器的内存小于或等于第二阈值。

9.本发明实施例还提供一种解交织器的执行方法,该解交织器与上文所述的交织器对应,该方法包括:接收所交织的数据;获取解交织步长;从所交织的数据的第一比特数据开始,以所述解交织步长为间隔,对所交织的数据中所有数据进行多轮非重复读取,以得到所述原始输入数据;以及输出所述原始输入数据。

10.优选地,所述解交织步长通过以下方法确定:使用所述交织器的深度除以所述交织步长,得到第四余数;在前n轮读取所交织的数据时,使用所述交织器的深度除以所述交织步长并取整后加1,作为所述解交织步长,其中n等于所述第四余数;在第n+1轮读取所交织的数据开始时,使用所述交织器的深度除以所述交织步长并取整,作为所述解交织步长。

11.本发明实施例还提供一种交织器,该交织器包括:第一接收单元、第一获取单元、交织单元以及第一输出单元,其中,所述第一接收单元用于根据交织深度,接收原始输入数据;所述第一获取单元用于获取交织步长;所述交织单元用于从所述原始输入数据的第一比特数据开始,以所述交织步长为间隔,对所述原始输入数据中的所有数据进行多轮非重复读取,以得到所交织的数据;以及所述第一输出单元用于输出所交织的数据。

12.优选地,所述交织步长与扩频因子范围内所有扩频因子的最大公约数为1。

13.优选地,所述第一接收单元用于:接收原始输入数据,以使得所接收的原始输入数据的长度小于或等于所述交织深度。

14.优选地,所述交织深度通过以下方法确定:确定所述交织器的内存;使用所述交织器的内存除以当前需要的扩频因子,得到第一余数;使用所述交织器的内存减去所述余数,得到所述交织深度。

15.优选地,所述交织器的内存满足以下条件:所述交织器的内存除以扩频因子范围内所有扩频因子,得到的第二余数均小于或等于第一阈值;所述交织器的内存除以所述原始输入数据的编码长度,得到的第三余数小于或等于所述第一阈值;所述交织器的内存小于或等于第二阈值。

16.本发明实施例还提供一种解交织器,该解交织器与上文所述的交织器对应,该解交织器包括:第二接收单元、第二获取单元、解交织单元以及第二输出单元,其中,所述第二接收单元用于接收所交织的数据;所述第二获取单元用于获取解交织步长;所述解交织单元用于从所交织的数据的第一比特数据开始,以所述解交织步长为间隔,对所交织的数据中所有数据进行多轮非重复读取,以得到所述原始输入数据;以及所述第二输出单元用于输出所述原始输入数据。

17.优选地,所述解交织步长通过以下方法确定:使用所述交织器的深度除以所述交织步长,得到第四余数;在前n轮读取所交织的数据时,使用所述交织器的深度除以所述交织步长并取整后加1,作为所述解交织步长,其中n等于所述第四余数;在第n+1轮读取所交织的数据开始时,使用所述交织器的深度除以所述交织步长并取整,作为所述解交织步长。

18.通过上述技术方案,采用本发明提供的交织器、解交织器、及其执行的方法,适用css调制系统,适用范围广泛,采用固定步长进行读取,易于实现,并且交织的随机性强,能够获得1比特纠错能力的信道编码的性能增益。

19.本发明实施例的其它特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

20.附图是用来提供对本发明实施例的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本发明实施例,但并不构成对本发明实施例的限制。在附图中:

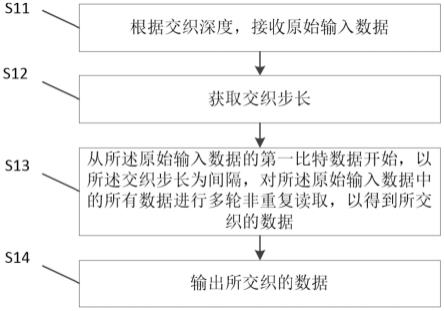

21.图1是本发明一实施例提供的交织器的执行方法的流程图;

22.图2是本发明一实施例提供的确定交织深度的方法的流程图;

23.图3是本发明一实施例提供的解交织器的执行方法的流程图。

24.图4是本发明一实施例提供的交织器的结构框图;

25.图5是本发明一实施例提供的解交织器的结构框图。

26.附图标记说明

27.401

ꢀꢀꢀꢀ

第一接收单元

ꢀꢀꢀꢀꢀꢀ

402

ꢀꢀꢀꢀꢀ

第一获取单元

28.403

ꢀꢀꢀꢀ

交织单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

404

ꢀꢀꢀꢀꢀ

第一输出单元

29.501

ꢀꢀꢀꢀ

第二接收单元

ꢀꢀꢀꢀꢀꢀ

502

ꢀꢀꢀꢀꢀ

第二获取单元

30.503

ꢀꢀꢀꢀ

解交织单元

ꢀꢀꢀꢀꢀꢀꢀꢀ

504

ꢀꢀꢀꢀꢀ

第二输出单元

具体实施方式

31.以下结合附图对本发明实施例的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明实施例,并不用于限制本发明实施例。

32.图1是本发明一实施例提供的交织器的执行方法的流程图。如图1所示,该方法包括:

33.步骤s11,根据交织深度,接收原始输入数据;

34.具体地,接收原始输入数据,以使得所接收的原始输入数据的长度小于或等于所述交织深度。例如,假设交织器的交织深度是143,那么即使原始输入数据是144比特数据,也只会接收143比特数据。如果交织深度是144,那么144比特数据的原始输入数据可以全部接收。

35.本发明如下提供一种确定交织深度的方式,如图2所示:

36.步骤s21,确定所述交织器的内存;

37.例如,所述交织器的内存满足以下条件:

38.第一,所述交织器的内存除以扩频因子范围内所有扩频因子,得到的第二余数均需要小于或等于第一阈值,为使得交织器的内存近似为所有扩频因子的倍数,第一阈值优选可以取4,即如下公式表示:

39.mod(c,sf1)≤4,mod为做除法然后返回余数,c为交织器的内存,sf1为扩频因子范围内所有扩频因子,在此,扩频因子范围常用6-12。

40.第二,所述交织器的内存除以所述原始输入数据的编码长度,得到的第三余数需要小于或等于所述第一阈值。一般来说,进入交织器的数据,是经过编码的。如上文所述,为使得交织器的内存近似为原始输入数据的编码长度的倍数,第一阈值优选可以取4,即如下公式表示;

41.mod(c,cl)≤4,mod为做除法然后返回余数,c为交织器的内存,cl为原始输入数据的编码长度。

42.第三,所述交织器的内存需要小于或等于第二阈值。为了减小存储空间和处理时延,交织器的内存不宜太大,第二阈值优选可以取200,即如下公式表示:

43.c≤200。

44.步骤s22,使用所述交织器的内存除以当前需要的扩频因子,得到第一余数;

45.例如,即第一余数如下公式计算:

46.mod(c,sf2),mod为做除法然后返回余数,c为交织器的内存,sf2为当前需要的扩频因子。在不同场景下,需要的扩频因子不同,此处可以使用当前需要的扩频因子。

47.步骤s23,使用所述交织器的内存减去所述第一余数,得到所述交织深度。

48.例如,此时在得到第一余数之后,就可以使用内存减去第一余数,得到交织深度。

49.步骤s12,获取交织步长;

50.具体地,在上述步骤s11接收原始输入数据之后,可以获取交织步长。该交织步长是指交织时需要跨过的距离。例如交织步长为2,则即从第1比特数据跨过1-2和2-3的2个距离,然后获得第3比特数据。在本发明实施例中,提供一种优选的交织步长,即,所述交织步长与扩频因子范围内所有扩频因子的最大公约数为1。通过下式表示:

51.gcd(step_size,sf1)=1,其中gcd为最大公约数,step_size为交织步长,sf1为扩频因子范围内所有扩频因子。

52.步骤s13,从所述原始输入数据的第一比特数据开始,以所述交织步长为间隔,对所述原始输入数据中的所有数据进行多轮非重复读取,以得到所交织的数据;

53.具体地,从原始输入数据的第一比特数据开始读取,然后跨交织步长,进行下一比特数据读取,直到无法再跨交织步长读取时停止该轮读取,并从开头开始下一轮读取(为了避免重复,应当从原始输入数据的第二比特数据开始读取),重复以上操作,直到原始输入数据中的所有数据都被读取。将上述读取到的数据按读取顺序进行排列,就是所交织的数据。

54.步骤s14,输出所交织的数据。

55.具体地,将所交织的数据输出,即完成交织。

56.图3是本发明一实施例提供的解交织器的执行方法的流程图。如图3所示,该解交织器与上文所述的交织器对应,该方法包括:

57.步骤s31,接收所交织的数据;

58.具体地,解交织器可以接收如上文所述的交织器输出的所交织的数据。

59.步骤s32,获取解交织步长;

60.具体地,本发明实施例提供一种对应于上述交织器的解交织器的解交织步长的确定方式。具体通过以下方法确定:使用所述交织器的深度除以所述交织步长,得到第四余数;在前n轮读取所交织的数据时,使用所述交织器的深度除以所述交织步长并取整后加1,作为所述解交织步长,其中n等于所述第四余数;在第n+1轮读取所交织的数据开始时,使用所述交织器的深度除以所述交织步长并取整,作为所述解交织步长。

61.步骤s33,从所交织的数据的第一比特数据开始,以所述解交织步长为间隔,对所交织的数据中所有数据进行多轮非重复读取,以得到所述原始输入数据;

62.具体地,如上文所述的对原始输入数据进行交织类似,在此对所交织的数据进行解交织,从所交织的数据的第一比特数据开始读取,然后跨解交织步长,进行下一比特数据读取,直到无法再跨解交织步长读取时停止该轮读取,并从开头开始下一轮读取(为了避免重复,应当从所交织的数据的第二比特数据开始读取),重复以上操作,直到所交织的数据中的所有数据都被读取。将上述读取到的数据按读取顺序进行排列,就是原始输入数据。

63.步骤s34,输出所述原始输入数据。

64.具体地,将原始输入数据输出,即完成解交织。

65.为了便于理解,本发明以下还提供一具体交织和解交织的例子,具体如下:

66.采用4/7汉明码(cl=7),扩频因子范围内所有扩频因子sf1=6,7,8,9,10,11,12,可以得到交织器的内存144,在当前的扩频因此sf2=9时,交织器的深度144,并且gcd(13,sf1)=1,因此交织步长为13。假设原始输入数据为144比特数据,如下:

67.123。。。143144

68.先读取1,按照交织补偿13,下一个读取的数据为14,以此读取,第一轮读取的数据为:

69.11427。。。131144

70.在读取到144之后,下一个要读取的数据应当是157,但是交织器并无157,因此从头开始第二轮读取,第二轮读取的数据为:

71.21528。。。119132

72.按照上述方式,第三轮读取的数据为:

73.31629。。。120133

74.为了简便,第四轮到第十二轮读取的数据在此不再赘述。

75.第十三轮读取的数据为:

76.132639。。。130143

77.自此,原始输入数据中所有数据均完成读取,因此,所交织的数据即为将上述被读取的数据按照读取顺序排列,得到144比特数据:

78.114。。。。。。130143

79.随后,可以对所交织的数据进行解交织。

80.首先,交织器的深度144除以交织器的步长13,得到11余数1。因此,在第1轮,使用解交织步长为11+1,在第2轮开始,使用解交织步长11。

81.因此,第一轮解交织进行读取得到:

82.123。。。1213

83.第二轮解交织进行读取得到:

84.141516。。。2526

85.第三轮解交织进行读取得到:

86.272829。。。3839

87.为了简便,第四轮到第十轮读取的数据在此不再赘述。

88.第十一轮解交织进行读取得到:

89.131132133。。。142143

90.第十二轮解交织进行读取得到:

91.144

92.自此,所交织的数据中所有数据均完成读取,因此,原始输入数据即为将上述被读取的数据按照读取顺序排列,得到144比特数据:

93.123。。。143144

94.使用本发明上述交织器、解交织器、及其执行的方法,具有以下优势:

95.1、交织器的深度选取合适,存储空间利用率高。

96.2、采用固定交织步长进行读取,易于实现。

97.3、交织的随机性好,能够获得1比特纠错能力的信道编码(比如4/7码率的汉明码)

的性能增益。

98.图4是本发明一实施例提供的交织器的结构框图。如图4所示,该交织器包括:第一接收单元401、第一获取单元402、交织单元403以及第一输出单元404,其中,所述第一接收单元401用于根据交织深度,接收原始输入数据;所述第一获取单元402用于获取交织步长;所述交织单元403用于从所述原始输入数据的第一比特数据开始,以所述交织步长为间隔,对所述原始输入数据中的所有数据进行多轮非重复读取,以得到所交织的数据;以及所述第一输出单元404用于输出所交织的数据。

99.优选地,所述交织步长与扩频因子范围内所有扩频因子的最大公约数为1。

100.优选地,所述第一接收单元401用于:接收原始输入数据,以使得所接收的原始输入数据的长度小于或等于所述交织深度。

101.优选地,所述交织深度通过以下方法确定:确定所述交织器的内存;使用所述交织器的内存除以当前需要的扩频因子,得到第一余数;使用所述交织器的内存减去所述余数,得到所述交织深度。

102.优选地,所述交织器的内存满足以下条件:所述交织器的内存除以扩频因子范围内所有扩频因子,得到的第二余数均小于或等于第一阈值;所述交织器的内存除以所述原始输入数据的编码长度,得到的第三余数小于或等于所述第一阈值;所述交织器的内存小于或等于第二阈值。

103.图5是本发明一实施例提供的解交织器的结构框图。如图5所示,该解交织器与上文所述的交织器对应,该解交织器包括:第二接收单元501、第二获取单元502、解交织单元503以及第二输出单元504,其中,所述第二接收单元501用于接收所交织的数据;所述第二获取单元502用于获取解交织步长;所述解交织单元503用于从所交织的数据的第一比特数据开始,以所述解交织步长为间隔,对所交织的数据中所有数据进行多轮非重复读取,以得到所述原始输入数据;以及所述第二输出单元504用于输出所述原始输入数据。

104.优选地,所述解交织步长通过以下方法确定:使用所述交织器的深度除以所述交织步长,得到第四余数;在前n轮读取所交织的数据时,使用所述交织器的深度除以所述交织步长并取整后加1,作为所述解交织步长,其中n等于所述第四余数;在第n+1轮读取所交织的数据开始时,使用所述交织器的深度除以所述交织步长并取整,作为所述解交织步长。

105.上述交织器和解交织器的实施例与上文所述的交织器的执行方法以及解交织器的执行方法的实施例类似,在此不再赘述。

106.还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括要素的过程、方法、商品或者设备中还存在另外的相同要素。

107.以上仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1