一种速率匹配的方法及装置与流程

本技术实施例涉及通信,尤其涉及一种速率匹配的方法及装置。

背景技术:

1、信道编解码(forward error correction)是通讯系统关键技术之一,对提升系统灵敏度和抗干扰能力都很重要。polar码是第一个理论上证明可以取得香农容量且具有低编译码复杂度的信道编码,且在码长较短或码率较低的场景下拥有远超其它竞争对手的性能,在第五代(5th generation,5g)通信系统中,将polar码确定为控制信道的编码方式。

2、在对系统延时不敏感的通信应用中,混合自动重传请求(hybrid automaticrepeat request, harq)是一种常用的用以提高系统吞吐率的传输方法。针对于polar码的harq传输方法,一种高效方案是增量冗余harq(incremental redundancy-harq,ir-harq),一般也被归类为harq类型二(harq-ii)。虽然ir-harq在没有速率匹配(即不需要打孔或者缩短) 时,通过可靠度序列选择需要复制的比特数量和位置能达到稳定的性能,但实际系统中,初传和重传的资源数不一定相等,存在重传编码后的比特数少于初传编码后的比特数的情况,这时候需要设计速率匹配方式,才能保证性能稳定,否则由于复制数量和长序列确定的复制位置的不理想,性能会有坏点。所以针对ir-harq如何设计合适的速率匹配方法,成为了亟需解决的问题。

技术实现思路

1、本技术实施例提供一种速率匹配的方法及装置,用于保证ir-harq的性能稳定。

2、本技术第一方面提供一种速率匹配的方法,包括:

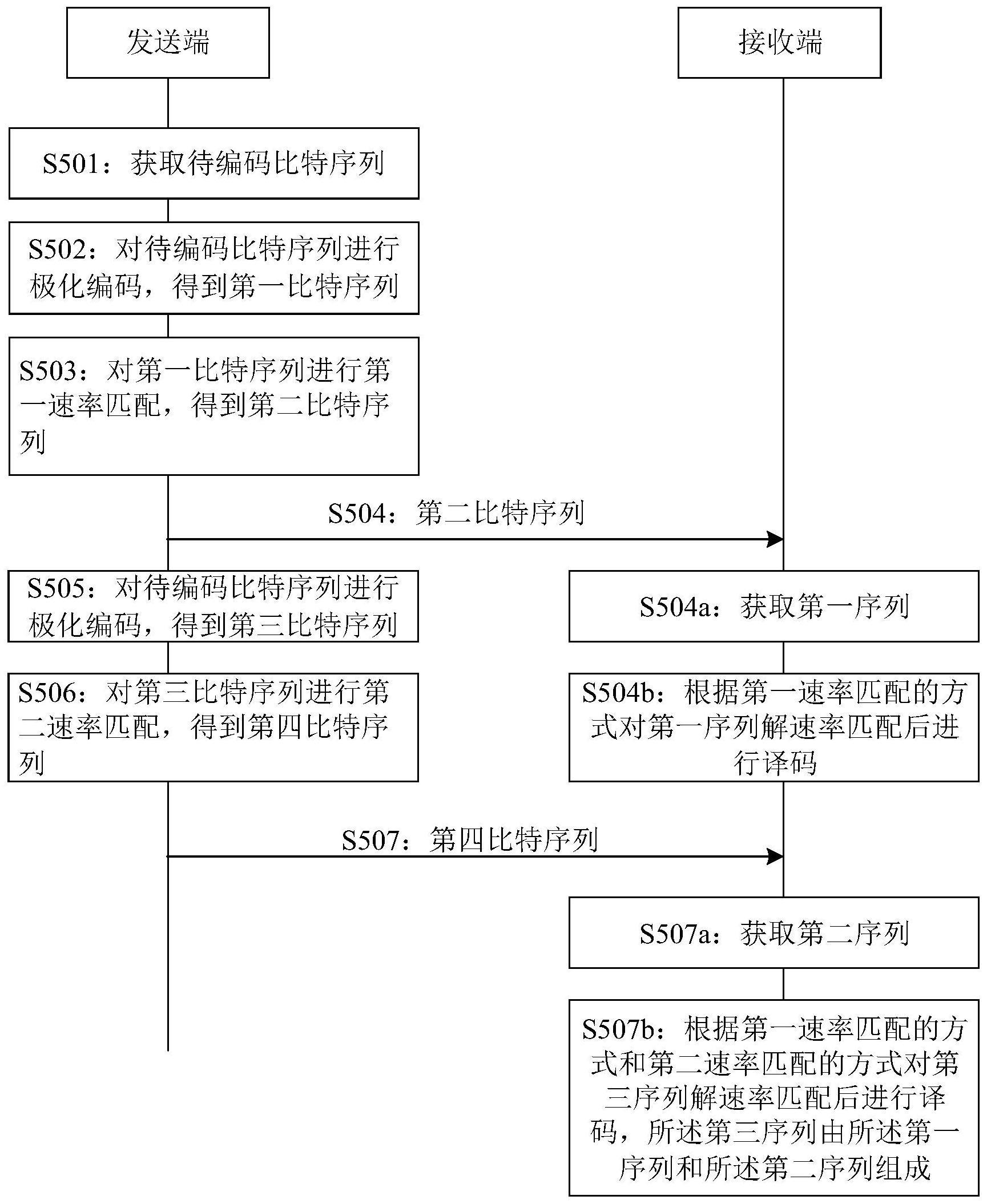

3、发送端获取待编码比特序列;该发送端对该待编码比特序列进行极化编码,得到第一比特序列,该第一比特序列的长度为n;该发送端对该第一比特序列进行第一速率匹配,得到第二比特序列,该第二比特序列的长度为e1;该发送端发送该第二比特序列;

4、该发送端根据该待编码比特序列进行极化编码,得到第三比特序列,该第三比特序列的长度为2*n;该发送端对该第三比特序列进行第二速率匹配,得到第四比特序列,该第四比特序列的长度为e2;该第二速率匹配为基于该f(e1)与e2的关系确定的;f(e1)的值为根据e1确定的;该发送端发送该第四比特序列;其中,n、e1、e2为正整数。

5、上述第一方面涉及一种可以应用在ir-harq中的发送端侧的速率匹配机制,为初传比特序列和重传比特序列分别设计了速率匹配方法,填补了现有技术中没有针对ir-harq的速率匹配方法的空白;更进一步的,为重传比特序列设计的速率匹配方法是根据初传比特序列和重传比特序列之间的关系确定的,针对不同的重传比特数和初传比特数之间不同的对应关系,设计了灵活的速率匹配方式,能够使得该速率匹配完全对应实际情况,从而使得 ir-harq的性能一直处在稳定且优异的状态下。

6、一种可能的实现方式中,该f(e1)=a*e1+b,其中,a为大于0且小于或等于1的常数,b 为绝对值小于e1的常数。

7、一种可能的实现方式中,该f(e1)=a*e1+b,其中,a,b为常数,满足f(e1)小于或等于e1。

8、一种可能的实现方式中,当e2大于或等于该f(e1)时,该第二速率匹配是基于第五比特序列执行的;或,当e2小于该f(e1)时,该第二速率匹配包括对该第五比特序列中第[0:n/2-1] 个比特打孔,并对第[n/2:n-1]个比特进行第三速率匹配;其中,第五比特序列由所述第三比特序列中第[0:n-1]个比特组成。

9、在该实现方式中,第五比特序列为第三比特序列的前半段,即第五比特序列由第三比特序列中的[0:n-1]个比特构成。当e2大于或等于该f(e1)时,第二速率匹配是按照母码的长度 n来执行的;当e2小于该f(e1)时,第二速率匹配是按照母码长度的一半,即n/2来执行的。

10、一种可能的实现方式中,当e2大于或等于该f(e1)时:

11、当e2小于n时,该第二速率匹配为比特逆序缩短;或,当e2大于n时,该第二速率匹配为重复;

12、当e2小于该f(e1)时:

13、当e2小于n/2时,该第三速率匹配为比特逆序缩短;或,当e2大于n/2时,该第三速率匹配为重复;

14、其中,该f(e1)为e1-n/16。

15、上述实现方式描述了当f(e1)为e1-n/16时的速率匹配规则,即a=1,b=-n/16时的速率匹配规则。

16、一种可能的实现方式中,当e2大于或等于f(e1)时:

17、该第二速率匹配包括:对该第五比特序列进行比特逆序缩短,然后按照自然序进行打孔;

18、或,

19、当e2小于f(e1)时:

20、该第三速率匹配为比特逆序缩短;

21、其中,该f(e1)为e1/2。

22、上述可能的实现方式描述了当f(e1)为e1/2时的速率匹配规则,即a=1/2,b=0时的速率匹配规则。

23、一种可能的实现方式中,该n根据该e1确定。具体的,。

24、一种可能的实现方式中,该第一速率匹配为比特逆序缩短。

25、在上述的几个实现方式中,将速率匹配方式设计为比特逆序缩短,而比特逆序缩短由于缩短位置分布比较均匀,很好的保留了比特位置间的可靠度排序,所以在各种码长和码率的场景下都有稳定的性能。

26、本技术第二方面提供一种速率匹配的方法,包括:

27、接收端获取第一序列,该第一序列长度为e1,该第一序列对应的母码长度为n;该接收端根据第一速率匹配的方式对该第一序列解速率匹配后进行译码;接收端获取第二序列,该第二序列长度为e2;该接收端根据第一速率匹配的方式和第二速率匹配的方式对第三序列解速率匹配后进行译码;第三序列由所述第一序列和所述第二序列组成;第三序列对应的母码长度为2*n;该第二速率匹配为基于该f(e1)与e2的关系确定的;f(e1)的值为根据e1确定的;其中,n、e1、e2为正整数。

28、相对应的,上述第二方面涉及一种可以应用在ir-harq中的接收端侧的速率匹配机制,其中,第一序列对应发送端的第二比特序列,即初传比特序列,第二序列对应发送端的第四比特序列,即重传比特序列,填补了现有技术中没有针对ir-harq的速率匹配方法的空白;更进一步的,为重传比特序列设计的速率匹配方法是根据初传比特序列和重传比特序列之间的关系确定的,针对不同的重传比特数和初传比特数之间不同的对应关系,设计了灵活的速率匹配方式,能够使得该速率匹配完全对应实际情况,从而使得ir-harq的性能一直处在稳定且优异的状态下。

29、一种可能的实现方式中,该f(e1)=a*e1+b,其中,a为大于0且小于或等于1的常数,b 为绝对值小于e1的常数。

30、一种可能的实现方式中,该f(e1)=a*e1+b,其中,a,b为常数,满足f(e1)小于或等于e1。

31、一种可能的实现方式中,当e2大于或等于该f(e1)时,该第二速率匹配是基于第五比特序列执行的;或,当e2小于该f(e1)时,该第二速率匹配包括对该第五比特序列中第[0:n/2-1] 个比特打孔,并对第[n/2:n-1]个比特进行第三速率匹配;其中,第五比特序列由所述第三比特序列中第[0:n-1]个比特组成。

32、在该实现方式中,第五比特序列为第三比特序列的前半段,即第五比特序列由第三比特序列中的[0:n-1]个比特构成。当e2大于或等于该f(e1)时,第二速率匹配是按照母码的长度 n来执行的;当e2小于该f(e1)时,第二速率匹配是按照母码长度的一半,即n/2来执行的。

33、一种可能的实现方式中,当e2大于或等于该f(e1)时:

34、当e2小于n时,该第二速率匹配为比特逆序缩短;或,当e2大于n时,该第二速率匹配为重复;

35、当e2小于该f(e1)时:

36、当e2小于n/2时,该第三速率匹配为比特逆序缩短;或,当e2大于n/2时,该第三速率匹配为重复;

37、其中,该f(e1)为e1-n/16。

38、上述可能的实现方式描述了当f(e1)为e1-n/16时的速率匹配规则,即a=1,b=-n/16时的速率匹配规则。

39、一种可能的实现方式中,当e2大于或等于f(e1)时:

40、该第二速率匹配包括:对该第五比特序列进行比特逆序缩短,然后按照自然序进行打孔;

41、或,

42、当e2小于f(e1)时:

43、该第三速率匹配为比特逆序缩短;

44、其中,该f(e1)为e1/2。

45、上述可能的实现方式描述了当f(e1)为e1/2时的速率匹配规则,即a=1/2,b=0时的速率匹配规则。

46、一种可能的实现方式中,该n根据该e1确定。具体的,。

47、一种可能的实现方式中,该第一速率匹配为比特逆序缩短。

48、在上述的几个实现方式中,可以将速率匹配方式设计为比特逆序缩短,而比特逆序缩短由于缩短位置分布比较均匀,很好的保留了比特位置间的可靠度排序,所以在各种码长和码率的场景下都有稳定的性能。

49、本技术第三方面提供一种速率匹配的装置,可以应用于发送端,该装置包括收发单元和处理单元:收发单元获取待编码比特序列;处理单元对该待编码比特序列进行极化编码,得到第一比特序列,该第一比特序列的长度为n;该处理单元对该第一比特序列进行第一速率匹配,得到第二比特序列,该第二比特序列的长度为e1;该收发单元发送该第二比特序列;该处理单元根据该待编码比特序列进行极化编码,得到第三比特序列,该第三比特序列的长度为2*n;该处理单元对该第三比特序列进行第二速率匹配,得到第四比特序列,该第四比特序列的长度为e2;该第二速率匹配为基于该f(e1)与e2的关系确定的;f(e1)的值为根据e1确定的;该收发单元发送该第四比特序列;其中,n、e1、e2为正整数。

50、一种可能的实现方式中,该f(e1)=a*e1+b,其中,a为大于0且小于或等于1的常数,b 的绝对值小于e1的常数。

51、一种可能的实现方式中,该f(e1)=a*e1+b,其中,a,b为常数,满足f(e1)小于或等于e1。

52、一种可能的实现方式中,当e2大于或等于该f(e1)时,该第二速率匹配是基于第五比特序列执行的;或,当e2小于该f(e1)时,该第二速率匹配包括对该第五比特序列中第[0:n/2-1] 个比特打孔,并对第[n/2:n-1]个比特进行第三速率匹配;其中,第五比特序列由所述第三比特序列中第[0:n-1]个比特组成。

53、在该实现方式中,第五比特序列为第三比特序列的前半段,即第五比特序列由第三比特序列中的[0:n-1]个比特构成。当e2大于或等于该f(e1)时,第二速率匹配是按照母码的长度 n来执行的;当e2小于该f(e1)时,第二速率匹配是按照母码长度的一半,即n/2来执行的。

54、一种可能的实现方式中,当e2大于或等于该f(e1)时:

55、当e2小于n时,该第二速率匹配为比特逆序缩短;或,当e2大于n时,该第二速率匹配为重复;

56、当e2小于该f(e1)时:

57、当e2小于n/2时,该第三速率匹配为比特逆序缩短;或,当e2大于n/2时,该第三速率匹配为重复;

58、其中,该f(e1)为e1-n/16。

59、上述实现方式描述了当f(e1)为e1-n/16时的速率匹配规则,即a=1,b=-n/16时的速率匹配规则。

60、一种可能的实现方式中,当e2大于或等于f(e1)时:

61、该第二速率匹配包括:对该第五比特序列进行比特逆序缩短,然后按照自然序进行打孔;

62、或,

63、当e2小于f(e1)时:

64、该第三速率匹配为比特逆序缩短;

65、其中,该f(e1)为e1/2。

66、上述可能的实现方式描述了当f(e1)为e1/2时的速率匹配规则,即a=1/2,b=0时的速率匹配规则。

67、一种可能的实现方式中,该n根据该e1确定。具体的,。

68、一种可能的实现方式中,该第一速率匹配为比特逆序缩短。

69、本技术第四方面提供一种速率匹配的装置,可以应用于接收端,该装置包括收发单元和处理单元:收发单元获取第一序列,该第一序列长度为e1,该第一序列对应的母码长度为n;该处理单元根据第一速率匹配的方式对该第一序列解速率匹配后进行译码;收发单元获取第二序列,该第二序列长度为e2;该处理单元根据第一速率匹配的方式和第二速率匹配的方式对第三序列解速率匹配后进行译码;第三序列由所述第一序列和所述第二序列组成;第三序列对应的母码长度为2*n;该第二速率匹配为基于该f(e1)与e2的关系确定的;f(e1)的值为根据e1确定的;其中,n、e1、e2为正整数。

70、一种可能的实现方式中,该f(e1)=a*e1+b,其中,a为大于0且小于或等于1的常数,bi为绝对值小于e1的常数。

71、一种可能的实现方式中,该f(e1)=a*e1+b,其中,a,b为常数,满足f(e1)小于或等于e1。

72、一种可能的实现方式中,当e2大于或等于该f(e1)时,该第二速率匹配是基于第五比特序列执行的;或,当e2小于该f(e1)时,该第二速率匹配包括对该第五比特序列中第[0:n/2-1] 个比特打孔,并对第[n/2:n-1]个比特进行第三速率匹配;其中,第五比特序列由所述第三比特序列中第[0:n-1]个比特组成。

73、在该实现方式中,第五比特序列为第三比特序列的前半段,即第五比特序列由第三比特序列中的[0:n-1]个比特构成。当e2大于或等于该f(e1)时,第二速率匹配是按照母码的长度 n来执行的;当e2小于该f(e1)时,第二速率匹配是按照母码长度的一半,即n/2来执行的。

74、一种可能的实现方式中,当e2大于或等于该f(e1)时:

75、当e2小于n时,该第二速率匹配为比特逆序缩短;或,当e2大于n时,该第二速率匹配为重复;

76、当e2小于该f(e1)时:

77、当e2小于n/2时,该第三速率匹配为比特逆序缩短;或,当e2大于n/2时,该第三速率匹配为重复;

78、其中,该f(e1)为e1-n/16。

79、上述可能的实现方式描述了当f(e1)为e1-n/16时的速率匹配规则,即a=1,b=-n/16时的速率匹配规则。

80、一种可能的实现方式中,当e2大于或等于f(e1)时:

81、该第二速率匹配包括:对该第五比特序列进行比特逆序缩短,然后按照自然序进行打孔;

82、或,

83、当e2小于f(e1)时:

84、该第三速率匹配为比特逆序缩短;

85、其中,该f(e1)为e1/2。

86、上述可能的实现方式描述了当f(e1)为e1/2时的速率匹配规则,即a=1/2,b=0时的速率匹配规则。

87、一种可能的实现方式中,该n根据该e1确定。具体的,。

88、一种可能的实现方式中,该第一速率匹配为比特逆序缩短。

89、本技术实施例第五方面提供一种通信装置,该通信装置包括:处理器和存储器。该存储器中存储有计算机程序;该处理器用于调用并运行该存储器中存储的计算机程序,使得处理器实现如第一方面中的任意一种实现方式。

90、本技术实施例第六方面提供一种通信装置,该通装置包括:处理器和存储器。该存储器中存储有计算机程序;该处理器用于调用并运行该存储器中存储的计算机程序,使得处理器实现如第二方面中的任意一种实现方式。

91、本技术实施例第七方面提供一种通信装置,该通装置包括:逻辑电路和输入输出接口:该输入输出接口用于输入待编码比特序列;该输入输出接口还用于输出第二比特序列和第四比特序列;该逻辑电路用于实现如第一方面中的任意一种实现方式。

92、本技术实施例第八方面提供一种通信装置,该通装置包括:逻辑电路和输入输出接口:该输入输出接口用于输入第一序列和第二序列;该逻辑电路用于实现如第一方面中的任意一种实现方式。

93、本技术实施例第九方面提供一种包括指令的计算机程序产品,其特征在于,当其在计算机上运行时,使得如第一方面至第二方面中任一种的实现方式被执行。

94、本技术实施例第十方面提供一种计算机可读存储介质,包括计算机指令,当该计算机指令在计算机上运行时,使得如第一方面至第二方面中的任一种实现方式被执行。

95、本技术实施例第十一方面提供一种芯片装置,包括处理器,用于与存储器相连,调用该存储器中存储的程序,以使得该处理器执行上述第一方面至第二方面中的任一种实现方式。

96、本技术实施例第十二方面提供一种通信系统,该通信系统包括如第三方面的装置和第四方面的装置。

97、上述第三方面至第十二方面达到的技术效果可以参考第一方面或第二方面中的技术效果,此处不再重复赘述。

- 还没有人留言评论。精彩留言会获得点赞!