一种5GLTE移动通信基站的制作方法

一种5g lte移动通信基站

技术领域

1.本实用新型涉及移动通信技术领域,具体而言,涉及一种5g lte移动通信基站。

背景技术:

2.目前5g lte移动通信基站主要是移动通信供应商为移动通信部署的基站,用于承载手机等各种智能设备之间的通信。这种基站通常为制式基站,根据移动供应商的要求设计相应的频段,输出固定的功率。

3.因为要求设计相应的频段并输出固定的功率的原因,传统基站往往无法满足基站小型化、平台化和可配置化的要求,也无法实时配置为不同的频段以和不同类型的手机进行通信。

技术实现要素:

4.为了解决上述技术问题,本实用新型提供了一种5g lte移动通信基站,具体技术方案如下:

5.第一方面,本公开实施例提供了一种5g lte移动通信基站,所述5glte移动通信基站包括:npu处理单元和基带处理单元;

6.所述npu处理单元与所述基带处理单元之间通信连接;

7.所述npu处理单元包括ls1046a处理器,所述基带处理单元包括fsm100xx物理层基带处理器、sdr9000射频前端处理器和fpga控制器;

8.其中,所述ls1046a处理器通过pcie接口与所述fsm100xx物理层基带处理器连接,以实现所述npu处理单元与所述基带处理单元之间的数据通信;

9.所述sdr9000射频前端处理器通过qlink接口与所述fsm100xx物理层基带处理器通信连接;

10.所述fpga控制器分别与所述ls1046a处理器、所述fsm100xx物理层基带处理器通信连接。

11.根据本公开实施例的一种具体实施方式,述ls1046a处理器上还包括预设数量的数字接口,用于连接通信终端,所述预设数量的数字接口的类型至少包括iic接口、uart接口、spi接口、rs485接口和gpio接口。

12.根据本公开实施例的一种具体实施方式,所述ls1046a处理器还包括预设数量的网络连接接口;

13.其中,第一网络连接接口的第一通道配置为xfi,所述第一网络连接接口的第一通道用于连接10g sfp接口;

14.第一网络连接接口的第二通道配置为2.5g sgmii,所述第一网络连接接口的第二通道用于通过2.5g phy芯片连接2.5g rj45接口;

15.第一网络连接接口的第三通道配置为1g sgmii,所述第一网络连接接口用于通过1g phy芯片连接1g rj45接口。

16.根据本公开实施例的一种具体实施方式,所述npu处理单元还包括nor flash、emmc flash、网络温度传感器和预设数量的ddr4 sdram;

17.所述ls1046a处理器通过qspi接口与所述nor flash连接;

18.所述ls1046a处理器通过sdhc接口与所述emmc flash连接;

19.所述ls1046a处理器通过ddr接口与所述预设数量的ddr4 sdram连接;

20.所述ls1046a处理器通过tmu/pd i2c1接口与所述网络温度传感器连接。

21.根据本公开实施例的一种具体实施方式,所述fpga控制器的型号为lcmxo3l

‑

1300e

‑

5uwg36ctr。

22.根据本公开实施例的一种具体实施方式,所述5g lte移动通信基站还包括时钟单元,所述时钟单元分别与所述npu处理单元、所述基带处理单元连接;

23.所述时钟单元包括时钟源ocxo、时钟发生器si5383、时钟缓冲器si53306和pmk8002芯片;

24.所述时钟源ocxo分别与时钟发生器si5383、fpga控制器和pmk8002连接;

25.所述时钟发生器si5383通过iic接口与所述ls1046a处理器通信连接,所述时钟发生器si5383还分别与fsm100xx物理层基带处理器、2.5g phy芯片和时钟缓冲器si53306连接。

26.根据本公开实施例的一种具体实施方式,所述ls1046a处理器还包括gps通信接口,用于连接gps接收机。

27.根据本公开实施例的一种具体实施方式,所述ls1046a处理器还用于连接系统电源;

28.所述基带处理单元还包括电源管理单元,所述电源管理单元的输入端用于连接系统电源,所述电源管理单元还分别与所述fsm100xx物理层基带处理器、所述sdr9000射频前端处理器连接;

29.所述电源管理单元包括pm8005芯片和pmx50芯片,其中,所述pm8005芯片与所述fsm100xx物理层基带处理器,所述pmx50芯片分别与sdr9000射频前端处理器、fsm100xx物理层基带处理器连接。

30.根据本公开实施例的一种具体实施方式,所述5g lte移动通信基站还包括复位单元;

31.所述复位单元包括sgm811芯片和系统复位电源;

32.所述系统复位电源与所述ls1046a处理器连接;

33.所述sgm811芯片的输入端用于连接系统电源,所述sgm811芯片的输出端分别与所述ls1046a、nor flash和emmc flash连接。

34.根据本公开实施例的一种具体实施方式,所述sdr9000射频前端处理器包括预设数量的rx引脚、预设数量的tx引脚、fbrx引脚和grfc_3引脚;

35.其中,所述rx引脚、所述tx引脚和所述fbrx引脚用于连接扩展功放单元;

36.所述grfc_3引脚用于连接射频功放设备。

37.本实用新型提供的一种5g lte移动通信基站,包括npu处理单元和基带处理单元,所述npu处理单元与所述基带处理单元之间通信连接,所述npu处理单元包括ls1046a处理器,所述基带处理单元包括fsm100xx物理层基带处理器、sdr9000射频前端处理器和fpga控

制器,其中,所述ls1046a处理器通过pcie接口与所述fsm100xx物理层基带处理器连接,以实现所述npu处理单元与所述基带处理单元之间的数据通信;所述sdr9000射频前端处理器通过qlink接口与所述fsm100xx物理层基带处理器通信连接;所述fpga控制器分别与所述ls1046a处理器、所述fsm100xx物理层基带处理器通信连接,通过所述npu处理单元和所述基带处理单元之间的通信交互,以及对于npu处理单元和基带处理单元的配置,所述5g lte移动通信基站能够实现option6配置、option7配置以及一体化5g配置,并支持任何5g sub6g频段的通信交互。

附图说明

38.为了更清楚地说明本实用新型实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本实用新型的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

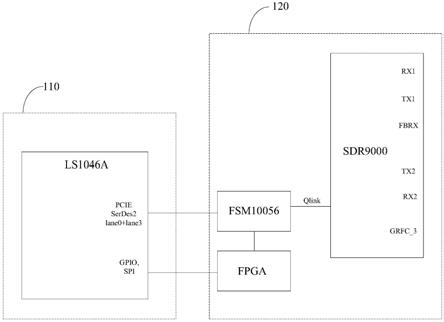

39.图1为本实用新型实施例提供的一种5g lte移动通信基站的结构示意图;

40.图2为本实用新型实施例提供的一种5g lte移动通信基站中的npu处理单元所包括的ls1046a处理器的结构示意图;

41.图3为本实用新型实施例提供的一种5g lte移动通信基站的另一结构示意图;

42.图4为本实用新型实施例提供的一种5g lte移动通信基站中所述ls1046a处理器的连接接口示意图;

43.图5为本实用新型实施例提供的一种5g lte移动通信基站中所述ls1046a处理器的另一连接接口示意图;

44.图6为本实用新型实施例提供的一种5g lte移动通信基站中时钟单元的连接示意图;

45.图7为本实用新型实施例提供的一种5g lte移动通信基站中si5383时钟发生器的结构示意图。

46.附图标记汇总:npu处理单元

‑

110;基带处理单元

‑

120。

具体实施方式

47.为使本实用新型实施例的目的、技术方案和优点更加清楚,下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本实用新型一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本实用新型实施例的组件可以以各种不同的配置来布置和设计。

48.因此,以下对在附图中提供的本实用新型的实施例的详细描述并非旨在限制要求保护的本实用新型的范围,而是仅仅表示本实用新型的选定实施例。基于本实用新型中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

49.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

50.在本实用新型的描述中,需要理解的是,术语“中心”、“上”、“下”、“左”、“右”、“竖

直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该实用新型产品使用时惯常摆放的方位或位置关系,或者是本领域技术人员惯常理解的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的设备或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

51.此外,术语“第一”、“第二”、“第三”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

52.在本实用新型的描述中,还需要说明的是,除非另有明确的规定和限定,术语“设置”、“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本实用新型中的具体含义。

53.参考图1,本实施例提供了一种5g lte移动通信基站,如图1所示,所述5g lte移动通信基站包括:npu处理单元110和基带处理单元120;

54.所述npu处理单元110与所述基带处理单元120之间通信连接;

55.所述npu处理单元110包括ls1046a处理器,所述基带处理单元120包括fsm100xx物理层基带处理器、sdr9000射频前端处理器和fpga控制器;

56.其中,所述ls1046a处理器通过pcie接口与所述fsm100xx物理层基带处理器连接,以实现所述npu处理单元110与所述基带处理单元120之间的数据通信;

57.所述sdr9000射频前端处理器通过qlink接口与所述fsm100xx物理层基带处理器通信连接;

58.所述fpga控制器分别与所述ls1046a处理器、所述fsm100xx物理层基带处理器通信连接。

59.在本实施例中,所述npu处理单元110与所述基带处理单元120之间通信连接,从而可以实现npu处理单元110与基带处理单元120之间的信息通信,传输如时钟信号、网络信号等通信信号,以实现如时钟同步,频段配置等功能。

60.所述npu处理单元110包括ls1046a处理器,如图2所示,所述ls1046a处理器是一款高性能的64位arm四核处理器,ls1046a处理器将四个64位arm cortex

‑

a72内核与数据包处理加速和高速外设相集成,能够与10gb以太网、第三代pcie、sata 3.0、usb 3.0和qspi接口配对,ls1046a可提供稳定的万兆数据通信。

61.所述ls1046a处理器特性包括1.2ghz

‑

1.8ghz主频、64位四核arm cortex

‑

a72、48kb

‑

i缓存、32kb

‑

d l1缓存、2mb l2缓存、2x 10gbe、1x 2.5gbe、5xgbe、八通道serdes、dpaa引擎、内置安全引擎、ddr4 sdram接口、3个pcie 3.0控制器、3个usb 3.0、sata 3.0控制器、quad spi接口、面向硬件增强虚拟化的arm smmu。其中,所述八通道serdes,频段最高可达10g hz,可以在控制器间多路复用,支持3个第二代pci express接口和1个sata3.0接口。所述3个pcie 3.0控制器类型分别为x4、x2、x1。所述3个usb 3.0,带有集成式phy。且所述ls1046a处理器支持可信架构。

62.当然,所述npu处理单元110也可以采用其它与ls1046a处理器功能相同的处理器,此处不作限定。

63.所述基带处理单元120包括fsm100xx物理层基带处理器、sdr9000射频前端处理器和fpga控制器。

64.其中,所述fsm100xx物理层基带处理器为高通fsm100xx平台,所述平台包括fsm10051芯片和fsm10056芯片,是符合sub

‑

6g标准(3gpp rel 15 5g nr)的物理层基带处理器,支持sub

‑

6g tdd模式,采用10ns工艺;集成arm cortex

‑

a7处理器,主频为800mhz;集成hexagon

tm dsp处理器,主频为866mhz;集成2gbit lpddr4x内存,速率为1.33g。

65.另外,所述fsm100xx支持2lanes的pcie gen3接口,fsm100xx需要通过pcie接口通过外部ls1046a来引导、配置和控制,以实现与ls1046a之间的数据通信,也即实现了npu处理单元110与基带处理单元120之间的数据通信。

66.所述sdr9000射频前端处理器是一个支持多频段射频收发器,与fsm10056通过qlink接口通信,所述sdr9000支持3gpp rel15 5g nr sub

‑

6ghz、上行256qam和下行256qam以及2x2 mimo。

67.所述fpga控制器,用于根据同步信号控制38.4mhzocxo晶体输出,并倍频和分频处不同时钟供fsm100xx处理器、pmx50、pm8005等使用。

68.所述fpga控制器可以提供1300个逻辑单元le和28个输入/输出,所述逻辑单元le包含4查找表lut和寄存器dff,内置硬宏,锁相环pll,spi从机,spi主机,i2c接口,定时器和内置用户flash存储器ufm。

69.优选的,所述fpga控制器的型号为lcmxo3l

‑

1300e

‑

5uwg36ctr。

70.在具体的实施过程中,所述fpga控制器内置的锁相环pll被编程为接收38.4mhz时钟并产生115.2mhz(3x 38.4mhz)的频率,核心可预先配置在这个频率上运行,并提供一个锁相输出。

71.所述spi从机硬宏通过wishbone总线接口控制。spi接口的最大频率为133mhz。对于fsm100xx,由于设计使用七级逻辑,因此选择了115.2mhz的频率。这个硬宏被预先设定为作为spi从机运行。

72.所述定时器的操作模式是快速脉冲宽度调制pwm。所述定时器硬宏的最大频率为133mhz。由于设计使用七级逻辑,在本实施例中选用115.2mhz;这个硬宏是预先设定为以50

‑

50占空比作为快速脉宽调制工作。

73.参考图3和图4,为本实施例公开的一种npu处理单元110和基带处理单元120的具体连接示意图,如图3所示,述ls1046a处理器上还包括预设数量的数字接口,用于连接通信终端,所述预设数量的数字接口的类型至少包括iic接口、uart接口、spi接口、rs485接口和gpio接口。

74.通过上述数字接口进行功能扩展,可以使得本实施例公开的5g lte移动通信基站作为一个通信平台,被广泛应用到通用移动通信设备和专网通信设备中,例如矿用系统、车联网通信系统等。

75.如图3和图5所示,所述ls1046a处理器还包括预设数量的网络连接接口;

76.其中,第一网络连接接口的第一通道配置为xfi,所述第一网络连接接口的第一通道用于连接10g sfp接口;

77.第一网络连接接口的第二通道配置为2.5g sgmii,所述第一网络连接接口的第二

通道用于通过2.5g phy芯片连接2.5g rj45接口;

78.第一网络连接接口的第三通道配置为1g sgmii,所述第一网络连接接口用于通过1g phy芯片连接1g rj45接口。

79.在本实施例中,如图5所示,所述第一网络连接接口的第一通道为ls1046a处理器的serdes1的lane0通道,用于连接10g retimer ds110df111sqe芯片,以输出10g sfp接口。

80.所述第一网络连接接口的第二通道为ls1046a处理器的serdes1的lane1通道,用于连接2.5g phy 88e2110芯片,以输出2.5g rj45接口。

81.所述第一网络连接接口的第三通道为ls1046a处理器的serdes1的lane3通道,用于连接1g phy ar8033芯片,以输出1g rj45。

82.从而所述包括ls1046a处理器的npu处理单元110可以提供一个1glan口用于基站管理通信,提供一种2.5g网络wan口和10g光纤wan口用于业务通信。

83.值得注意的是,每个所述serdes接口有两种锁相环,分别为锁相环pll1和锁相环pll2,在具体的实施例中每个lane根据协议差别参考的pll也不相同,需要根据情况选择pll映射配置,此处不作限定。优选的,在本实施例中,根据配置要求pll参考时钟配置可以为将serdes1 pll1设置为156.25mhz hcsl;将serdes1 pll2设置为100mhz hcsl;将serdes2 pll1设置为100mhz hcsl;将serdes2 pll2设置为100mhz hcsl。

84.通过ls1046a处理器的丰富接口,从而可以方便配置各种模式,以实现低成本高效率的以太网接口配置。

85.根据本公开实施例的一种具体实施方式,所述npu处理单元110还包括nor flash、emmc flash、网络温度传感器和预设数量的ddr4 sdram;

86.所述ls1046a处理器通过qspi接口与所述norflash连接;

87.所述ls1046a处理器通过sdhc接口与所述emmc flash连接;

88.所述ls1046a处理器通过ddr接口与所述预设数量的ddr4 sdram连接;

89.所述ls1046a处理器通过tmu/pd i2c1接口与所述网络温度传感器连接。

90.其中,所述nor flash、所述emmc flash和所述预设数量的ddr4sdram均用于存储程序和信号,根据固定配置和具体应用场景进行适应性调整。

91.所述网络温度传感器用于检测所述npu处理单元110的温度,在温度过高时向所述ls1046a处理器发出报警信号。

92.对于lte移动通信基站来说,时钟信号和时钟同步是基站通信正常工作的关键,对于所述npu处理单元110和所述基带处理单元120来说,也需要不同的时钟信号,来支持单元内各个元器件的正常运行。

93.如图3和图6所示,所述5g lte移动通信基站还包括时钟单元,所述时钟单元分别与所述npu处理单元110、所述基带处理单元120连接;

94.所述时钟单元包括时钟源ocxo、时钟发生器si5383、时钟缓冲器si53306和pmk8002芯片;

95.所述时钟源ocxo分别与时钟发生器si5383、fpga控制器和pmk8002连接;

96.所述时钟发生器si5383通过iic接口与所述ls1046a处理器通信连接,所述时钟发生器si5383还分别与fsm100xx物理层基带处理器、2.5g phy芯片和时钟缓冲器si53306连接。

97.在具体的实施例中,所述时钟源ocxo为38.4mhz ocxo,用于提供基础时钟。相比于传统的vctcxo,ocxo具有失锁定条件下更好的稳定能力,可以在失锁定条件下维持长达10小时的时钟稳定,提高基站的稳定性。

98.如图6所示,所述时钟源ocxo将38.4mhz的基础时钟信号分别传输给所述基带处理单元120中的fpga控制器和pmk8002芯片、所述npu处理单元110中的时钟发生器si5383。所述pmk8002芯片同时为sdr9000和fsm10056提供38.4mhz时钟信号。所述时钟发生器si5383为ls1046a处理器同时提供125mhz、156.25mhz、100mhz时钟信号和1pps信号。

99.所述fpga控制器在接收了所述38.4mhz的基础时钟信号后,可以根据同步信号对ocxo输出信号进行训练,并输出经过所述fpga控制器汇总pdm单元训练后的压控信号fpga_pdm_vctcxo,控制所述时钟源输出满足要求。

100.如图7所示,为所述时钟发生器si5383的示意性结构图。所述时钟发生器si5383采用的是三级锁相环结构,单芯片上集成3个独立的dspll,支持灵活的synce和ieee 1588配置要求。

101.具体的,所述时钟发生器si5383支持7路差分输出或14路单端输出,最大输出频率可达到差分718.5mhz,单端输出可达到250mhz;输出可灵活配置为差分lvpecl、lvds、hcsl,cml和单端型lvcmos等电平类型;输出时钟具有低至95fs(10khz~20mhz)抖动性能;

102.所述时钟发生器si5383具备5个输入时钟,支持外部晶体,tcxo/ocxo,差分时钟和单端时钟输入;外部晶体支持频率48~54mhz,tcxo/ocxo支持5~250mhz,差分时钟支持8khz~750mhz,单端lvcmos时钟支持8khz~250mhz;

103.值得注意的是,si5383的in0通道用于输入synce时钟,synce时钟来自phy芯片从以太网线路上恢复出的时钟,实现synce+ieee 1588的功能。

104.根据本公开实施例的一种具体实施方式,所述ls1046a处理器还包括gps通信接口,用于连接gps接收机。

105.在一个具体的实施例中,所述npu处理单元110的时钟连接关系可以是由si5383输出各种时钟,分别为ls1046a处理器、fsm100xx物理层基带处理器和2.5g phy芯片等提供参考时钟。

106.具体的,所述si5383的输入时钟:

107.ref:参考时钟,频率为38.4mhz,由ocxo输出提供;

108.xa/xb:基本时钟,频率为48mhz,由时钟晶体输出提供;

109.输入通道in4:gps_1pps同步信号,由gps接收机输出提供;

110.输入通道in0:synce同步信号,由2.5g phy芯片88e2110输出提供;

111.输入通道in3:1588_1pps同步信号,由ls1046处理器内部的ieee1588单元解析出提供;

112.同时si5383与ls1046a处理器之间通过iic接口通信。

113.所述si5383的输出时钟:

114.out0通道:输出差分100mhz hcsl信号给时钟缓冲器si53306,所述时钟缓冲器si53306可以基于1路输入扩展出4路输出;

115.所述时钟缓冲器si53306输出四路差分100mhzhcsl信号,所述时钟缓冲器的第一差分信号输出路out0输出给基带处理器fsm100xx的pcie参考时钟;第二差分信号输出路

out1输出给ls1046a处理器的sd2_refclk1;第三差分信号输出路out2输出给ls1046a处理器的sd2_refclk2;第四差分信号输出路out3输出给ls1046a处理器的sd1_refclk1;

116.out1通道:输出差分100mhz lvds信号给ls1046a处理器的diff_sysclk信号;

117.out2通道:输出差分125mhz lvcoms信号给ls1046a处理器的ieee1588处理单元;

118.out3通道:输出差分156.25mhz hcsl信号给ls1046a处理器的sd1_refclk2信号;

119.out4通道:输出差分156.25mhz hcsl信号给88e2110芯片作为参考时钟;

120.out5通道:输出lvcoms_1pps信号给fpga控制器。

121.具体的,时钟同步是基站通信正常工作的关键,而同步的基础源时钟是卫星,也就是说,保证所有通信基站与卫星时钟边沿一致,彼此之间就可以实现通信。

122.在本实施例中,所述npu处理单元110和所述基带处理单元120基于不同配置,可以实现ieee1588+synce同步、卫星同步和sniffer同步三种同步方式。

123.在进行卫星同步方式时,采用gps收发机执行,根据不同需求,将gps收发机配置为和北斗、gps或伽利略卫星进行同步。

124.当所述gps收发机同步到卫星后,会输出1pps信号及tod信号,所述1pps信号的上升沿为时间同步点,在本基站中,所需要同步的时间点均以改所述1pps信号上升沿为基础,其中,所述tod信号即时间信息,将所述tod信号发送给ls1046a处理器;

125.所述gps收发机输出的1pps信号还分别发送给si5383的in4引脚和基带处理单元120上的fpga控制器。所述fpga控制器输出同步1pps同步信号给fsm100xx和npu处理单元110,完成系统同步。

126.ieee1588是一个精密时间协议ptp,用于同步计算机网络中的时钟。在局域网中,它能将时钟精确度控制在亚微秒范围内,使其适于测量和控制系统。在进行ieee1588+synce同步时,通过以太网解析出同步信号;

127.ls1046a接收si5383输出的100mhz,125mhz、156.25mhz等时钟信号,完成配置后工作。2.5g phy接收si5383输出的156.25mhz时钟信号以及48mhz时钟晶体工作信号。ls1046a和2.5g phy芯片共同工作,连接互联网后,通过ls1046a内部算法解析出1588同步信号。

128.在ls1046a解析出1588信号后,通过1588_pulse_out又传输给si5383的in3,作为1588同步的输入。si5383的out5输出lvcoms类型的1588同步信号给fpga。

129.si5383的in0通道用于输入synce时钟,synce时钟来自phy芯片从以太网线路上恢复出的时钟,实现synce+ieee 1588的功能。

130.同步以太网synce,定义了如何在以太网物理层中传送时钟信号。同步以太网的目的是为网络中的各种资源提供同步信号。同步以太网信号在以太网物理层中传输,并能追溯至少一个外部时钟。

131.在进行sniffer同步时,通过fsm100xx物理层基带处理器扫描环境中的4或5g等无线信号,进而从其它无线射频信号中解析出nl_1pps信号,并将所述nl_1pps信号传输给fpga控制器,以实现同步。

132.根据本公开实施例的一种具体实施方式,所述ls1046a处理器还用于连接系统电源;

133.所述基带处理单元120还包括电源管理单元,所述电源管理单元的输入端用于连接系统电源,所述电源管理单元还分别与所述fsm100xx物理层基带处理器、所述sdr9000射

频前端处理器连接;

134.所述电源管理单元包括pm8005芯片和pmx50芯片,其中,所述pm8005芯片与所述fsm100xx物理层基带处理器,所述pmx50芯片分别与sdr9000射频前端处理器、fsm100xx物理层基带处理器连接。

135.在具体的实施例中,所述系统电源采用12v供电电源,为所述npu处理单元110和所述基带处理单元120供电的两部分电源相对独立,没有相互间的时序限制。所述电源可以根据实际设置的需要,进行适应性的时序设计,以满足所述npu处理单元110和所述基带处理单元120内各元器件的工作需求,并充分保证效率,此处不作限定。

136.具体的,所述pm8005芯片和所述pmx50芯片的一部分输入电压,由所述ls1046a的进行供给,所述pm8005芯片和所述pmx50芯片的另一部分输入电压,由电源连接一个低压差线性稳压器ld0后进行供给。

137.所述pm8005用于调整给所述fsm100xx物理层基带处理器的电压,并为所述fsm100xx物理层基带处理器供电。

138.所述pmx用于调整管理电压,并为sdr9000射频前端处理器和fsm100xx物理层基带处理器进行供电。

139.上述其它设备的输入电压,均可由所述ls1046a进行供给。

140.根据本公开实施例的一种具体实施方式,所述5g lte移动通信基站还包括复位单元;

141.所述复位单元包括sgm811芯片和系统复位电源;

142.所述系统复位电源与所述ls1046a处理器连接;

143.所述sgm811芯片的输入端用于连接系统电源,所述sgm811芯片的输出端分别与所述ls1046a、nor flash和emmc flash连接。

144.系统采用sgm811芯片作为上电复位源,同时用作3.3v电压监控功能,门限电压2.93v,复位脉冲宽度典型值240ms,具体可为150ms~560ms,满足系统复位要求。所述sgm811芯片输出驱动可达20ma,因此系统设计中采用sgm811芯片输出直接驱动ls1046a、nor flash和emmc flash,以保证ls1046a启动后可以正常从flash中读取数据。

145.具体的,当给到所述sgm811芯片3.3v电压输出时,所述sgm811芯片工作,其输出240ms复位脉冲,可以复位所述npu处理单元110和所述基带处理单元120内的所有元器件。

146.值得注意的是,所述ddr4芯片、2.5g phy 88e2110、1g phy ar8033和fpga控制器的复位,均由ls1046a进行控制。

147.根据本公开实施例的一种具体实施方式,所述sdr9000射频前端处理器包括预设数量的rx引脚、预设数量的tx引脚、fbrx引脚和grfc_3引脚;

148.其中,所述rx引脚、所述tx引脚和所述fbrx引脚用于连接扩展功放单元;

149.所述grfc_3引脚用于连接射频功放设备。

150.具体的,本实施例中的5g lte移动通信基站可以支持所有5g sub6g频段,通过输出sdr9000射频收发器可以输出各个频段的射频信号,输出功率为5dbm。通过外接扩展功放单元,还可以实现不同等级功率的信号输出。

151.本实施例的5g lte移动通信基站支持数字预失真dpd功能,可以极大的提高功放输出效率,降低整机功耗,节约电能。

152.综上所述,本公开实施例提供了一种5g lte移动通信基站,其所述npu处理单元可以通过回传接口连接核心网络,使得基站系统最大上下行数据大于2.5gbps,采用10g以太网端口,并采用光纤布线,物理接口使用sfp+光口实现,系统支持synce,从synce线路恢复的时钟从phy 88e2111输出,送到同步时钟芯片si5383锁定,从而实现option6和option7配置。

153.所述npu处理单元还支持电口1000base

‑

t回传接口连接核心网络,使得基站系统最大上下行数据小于1gbps,采用1g的rj45以太网端口,所述sfp接口直接与ls1046a的sgmii连接,从而可以实现5g一体化配置。

154.以上所述仅为本实用新型的优选实施例而已,并不用于限制本实用新型,对于本领域的技术人员来说,本实用新型可以有各种更改和变化。凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1