支持实现自动化超宽带无线信号采集传输处理的系统的制作方法

1.本实用新型涉及宽带无线信号自动化领域,尤其涉及宽带无线信号自动化采集及传输领域,具体是指一种支持实现自动化超宽带无线信号采集传输处理的系统。

背景技术:

2.通用信号分析仪均具备宽带信号采集并网络传输的能力,操作场景为信号分析仪通过射频缆线连接待测设备,通过千兆网卡连接至局域网络,网络中存在远程控制主机,主机通过发送scpi指令设置分析仪的频点、参考电平或采样时长等参数,每次设置需要一个单独的scpi指令操作,耗时较长,待参数配置完毕后再发送scpi数据请求指令,完成iq数据的网络传输。上述操作流程均由远程控制主机发起,通过编写脚本逐条运行,交互频繁,操作时间长,如果应用于流水线等产线场景,效率极低。本实用新型将参数设置脚本放置于fpga中执行,配备有网络中心服务器,该服务器提供数据缓存池及节拍信号,保证信号采集端在统一的步调下执行,具有操作时刻可控、运行效率高、系统带宽使用率高的特点,完全满足产线测试效率要求高,测试范例固定的特定需求。另外,本实用新型采用硬件功率校准技术,将海量校准数据预先缓存至fpga的ddr外设,实现功率实时补偿。为进一步提高频谱分析速度,fft等数据分析操作也作为选件在fpga中实现。

技术实现要素:

3.本实用新型的目的是克服了上述现有技术的缺点,提供了一种满足效率高、采样率高、适用范围较为广泛的支持实现自动化超宽带无线信号采集传输处理的系统。

4.为了实现上述目的,本实用新型的支持实现自动化超宽带无线信号采集传输处理的系统如下:

5.该支持实现自动化超宽带无线信号采集传输处理的系统,其主要特点是,所述的系统包括:

6.射频变频单元;

7.宽带滤波器单元,与所述的射频变频单元相连接;

8.高速adc单元,与所述的宽带滤波器单元相连接;

9.fpga信号处理单元,与所述的高速adc单元相连接;

10.主控单元,与所述的fpga信号处理单元相连接;

11.网络传输接口,与所述的主控单元相连接;

12.中心服务器,接收端与所述的网络传输接口相连接,输出端与fpga信号处理单元相连接;

13.同步信号接口,与所述的中心服务器相连接;

14.参考时钟单元,接收端与所述的同步信号接口相连接,输出端与高速adc单元和fpga信号处理单元相连接;

15.本振单元,接收端与所述的参考时钟单元相连接,输出端与射频变频单元相连接。

16.较佳地,所述的fpga信号处理单元包括:

17.逻辑控制状态机;

18.控制寄存器,与所述的逻辑控制状态机相连接;

19.脚本存储器,与所述的逻辑控制状态机相连接,包括正本和副本;

20.外设控制接口,与所述的逻辑控制状态机相连接;

21.数据通道,与所述的逻辑控制状态机相连接;

22.外部触发激励信号接口,与所述的逻辑控制状态机相连接。

23.较佳地,所述的射频变频单元的前端通过开关形成两路预处理通道,其中一路预处理通道采用数控衰减器,处理大功率信号,对大信号进行功率衰减;另外一路预处理通道采用固定增益低噪放,处理小信号通路。

24.较佳地,所述的高速adc单元包含ddc及半带滤波数字信号处理链路,具有不同的信号处理模式。

25.采用了本实用新型的支持实现自动化超宽带无线信号采集传输处理的系统,采用网络架构,采集和测量分离。具体为数据集中缓存、数据采集节点分布式部署,同时保证采集节点设置的灵活性和中央调度的统一性。采用中心服务器产生时序节拍的方法,统一调度采集节点的任务时序,充分利用网络带宽,减少网络传输冲突,提高了无线信号采集效率,适用于产线流水线测试。系统架构较为合理,数据流清晰,采用多项技术,实时处理宽带信号,使用硬件均衡技术,补偿通带内频响,降低带内波动,提高功率及evm测量精确度。

附图说明

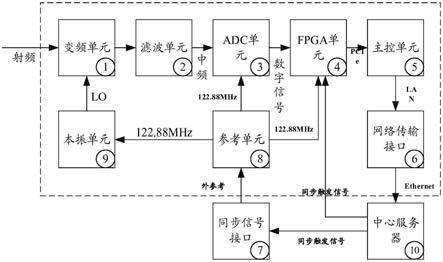

26.图1为本实用新型的支持实现自动化超宽带无线信号采集传输处理的系统的方案框图。

27.图2为本实用新型的支持实现自动化超宽带无线信号采集传输处理的系统的控制逻辑fpga实现框图。

28.图3为本实用新型的支持实现自动化超宽带无线信号采集传输处理的系统的控制流程图。

29.图4为本实用新型的支持实现自动化超宽带无线信号采集传输处理的系统的数据流程框图。

具体实施方式

30.为了能够更清楚地描述本实用新型的技术内容,下面结合具体实施例来进行进一步的描述。

31.本实用新型的支持实现自动化超宽带无线信号采集传输处理的系统的技术方案中,其中所包括的各个功能模块和模块单元均能够对应于集成电路结构中的具体硬件电路,因此仅涉及具体硬件电路的改进,硬件部分并非仅仅属于执行控制软件或者计算机程序的载体,因此解决相应的技术问题并获得相应的技术效果也并未涉及任何控制软件或者计算机程序的应用,也就是说,本实用新型仅仅利用这些模块和单元所涉及的硬件电路结构方面的改进即可以解决所要解决的技术问题,并获得相应的技术效果,而并不需要辅助以特定的控制软件或者计算机程序即可以实现相应功能。

32.本实用新型的该支持实现自动化超宽带无线信号采集传输处理的系统,其中包括:

33.射频变频单元;

34.宽带滤波器单元,与所述的射频变频单元相连接;

35.高速adc单元,与所述的宽带滤波器单元相连接;

36.fpga信号处理单元,与所述的高速adc单元相连接;

37.主控单元,与所述的fpga信号处理单元相连接;

38.网络传输接口,与所述的主控单元相连接;

39.中心服务器,接收端与所述的网络传输接口相连接,输出端与fpga信号处理单元相连接;

40.同步信号接口,与所述的中心服务器相连接;

41.参考时钟单元,接收端与所述的同步信号接口相连接,输出端与高速adc单元和fpga信号处理单元相连接;

42.本振单元,接收端与所述的参考时钟单元相连接,输出端与射频变频单元相连接。

43.作为本实用新型的优选实施方式,所述的fpga信号处理单元包括:

44.逻辑控制状态机;

45.控制寄存器,与所述的逻辑控制状态机相连接;

46.脚本存储器,与所述的逻辑控制状态机相连接,包括正本和副本;

47.外设控制接口,与所述的逻辑控制状态机相连接;

48.数据通道,与所述的逻辑控制状态机相连接;

49.外部触发激励信号接口,与所述的逻辑控制状态机相连接。

50.作为本实用新型的优选实施方式,所述的射频变频单元的前端通过开关形成两路预处理通道,其中一路预处理通道采用数控衰减器,处理大功率信号,对大信号进行功率衰减;另外一路预处理通道采用固定增益低噪放,处理小信号通路。

51.作为本实用新型的优选实施方式,所述的高速adc单元包含ddc及半带滤波数字信号处理链路,具有不同的信号处理模式。

52.本实用新型的具体实施方式中,提供了一种利用中心服务器提供数据缓存池并提供同步节拍信号,控制网络中无线信号采集设备实现流水线测试自动化的方案。该方案功能结构如图2所示,主要由十部分组成,分别是一次射频变频单元、宽带滤波器单元、高速adc单元、参考时钟单元、本振单元、fpga信号处理单元、主控单元、网络传输接口、同步信号接口及中心服务器。

53.如图1所示为实用新型方案框图,罗列了系统组成构建及逻辑关系,主体分为两部分,虚线圈住部分为分布式采集单元实现框图,另外一部分为基于网络的中心服务器,上述两者分别承担不同的工作任务,采集单元通过变频采样,实现无线信号的采集、存储及回传;中心服务器运行缓存池,并响应回传请求,同时发起节拍事件,引导采集单元按照特定的时序执行。

54.一次射频变频单元覆盖10mhz至8ghz频率范围,将待测高频射频信号变频至中频频率,中频频点设置为307.2mhz;

55.宽带滤波器单元对中频信号进行滤波,滤除镜像频率,并实现adc前端抗混叠滤波

器功能;

56.高速adc单元采用1.2288ghz采样时钟对中频宽带信号进行数字量化,保证500mhz分析带宽,通过jesd204b接口与fpga通信,将量化信号传输给fpga进行后续dsp处理;

57.参考单元对10mhz高稳高精度时钟进行锁定,控制122.88mhz的vcxo产生相噪优良的稳定信号,并以122.88mhz信号为基础频率,10倍频产生采样时钟。参考时钟单元通过功分器将122.88mhz参考时钟提供给fpga单元和本振单元,实现所需的时钟树设计;

58.本振单元对122.88mhz参考信号进行锁定,采用小数分频,控制宽带vco,产生混频器所需的本振信号;

59.fpga信号处理单元提供dsp处理逻辑,采用jesd204b与高速adc通信,采用ddr4作为外部缓存器,采用pcie与上位机通信,提供了匹配的接口带宽,保证500mhz带宽信号的接收、多项滤波器、数字下变频、数据缓存及数据上传。

60.下面对不同的功能单元作进一步描述:

61.1、一次射频变频单元:采用有源混频器,频率范围覆盖10mhz至8ghz,其主要功能是实现不同频点的射频信号变频转换至固定中频输出,中频频点设定为307.2mhz;射频前端通过开关形成两路预处理通道,一路为处理大功率信号,采用数控衰减器,可对大信号做可编程功率衰减,另外一路为处理小信号通路,采用固定增益低噪放,降低链路噪声系数,增强信号灵敏度。

62.2、宽带滤波器单元:低通设计,使用腔体滤波器,改善过渡带矩形系数,通带带宽为500mhz,主要作用为混频后镜像抑制及adc前端抗混叠。

63.3、高速adc单元:使用采样率为1.2288ghz的高速adc,数据接口为jesd204b,链路采用4x接口,单根lane速率为12.288ghz;该adc内部包括ddc及半带滤波数字信号处理链路,可编程实现不同的信号处理模式。

64.4、参考时钟单元:具有内外参考切换功能,板载高精度10mhz ocxo,通过锁相环路与122.88mhz vcxo时钟进行锁相,从而产生高精度122.88mhz的基准时钟,该时钟分别提供给本振单元及fpga单元作为参考,同时10倍频后产生1.2288ghz时钟作为adc的采样时钟。

65.5、本振单元:使用集成套片电路结构,具有小数分频能力,以122.88mhz参考作为基准锁相时钟,通过软件控制,产生不同的混频本振信号,本振信号功率可调,实现混频器3阶等性能最优化。

66.6、fpga信号处理单元:采用kintex ultrascale低功耗fpga,实现量化信号的数字处理功能,具体功能模块包括与adc的jesd204b高速数据接口、多相fir低通滤波器、多相fir任意响应滤波器、数字下变频单元、ddr4数据缓冲接口单元、pcie上位机通信接口单元。

67.7、主控单元:采用x86架构cpu,通过pcie与fpga进行通信,实现硬件初始化及控制,实现数据采集上传,实现网络数据传输,支持scpi指令解析。

68.8、网络传输接口:实现指令及数据的网络传输。

69.9、同步信号接口:实现系统的定时同步信号的传递。

70.10、中心服务器:在本地网络中承载数据池服务,支持采集设备数据的上传和存储,实现同步节拍信号发起及控制功能,是网络系统中的控制中枢。

71.如图2所示为本实用新型控制逻辑fpga实现框图,主要内容是1控制寄存器,软件可访问,配置当前工作参数和操作流程;2是脚本存储器,分为正本和副本,可选择某一脚本

执行;3是射频等外设控制接口,按照脚本语义进行外设的配置和操作;4是数据通道,根据外部触发信号指引,执行数据缓存或回传操作;5是逻辑控制状态机,按照软件参数配合外部触发激励信号执行状态跳转,实现不同的时序流程;6是外部触发激励信号接口,可以整形,计数,并产生特定事件。

72.按照处理流程进一步描述:

73.1、无线信号采集前端电路对射频信号进行变频处理,变频至固定频点307.2mhz;该通带信号通过通带500mhz带通滤波器进行抗混叠处理,馈入adc进行量化;adc采样频率为1.2288ghz;

74.2、高速adc实现了1.2288ghz的高速采样;使用了高速jesd204b链路与fpga通信,单根lane速率可达12.288gbps,将500mhz带宽量化信号准确传输至fpga。

75.3、fpga内部采用xilinx提供的jesd204b ip核与adc进行通信,用户接口时钟为307.2mhz,1个时钟具有4个采样点,并行数据传递至后端dsp单元进行进一步处理。

76.4、采集到的高速并行数据通过多项fir数字滤波器进行滤波,实现较高矩形系数的滤波器,提高过渡带陡峭度,低通滤波后的数据传递至任意响应滤波器,进行宽带内均衡,补偿系统的幅频响应,降低带内波动,为较高质量的功率测量提供硬件补偿。

77.5、fpga接收外部节拍信号,在触发时刻将处理完毕的数据缓存至ddr4外部存储空间,缓存数据长度可调,时长参数软件可设,满足后续上位机对iq数据的请求以及后续流控。fpga可产生中断信号,在全局节拍信号的激励下定时进行网络数据传输。

78.6、上位机根据硬件中断信号请求iq数据并通过pcie缓存至上位机,然后通过网络传输,将连续iq的数据传输至服务端;

79.7、服务端响应iq数据网络传输请求,并将数据缓存至资源池。服务端产生全局节拍信号,控制数据采集、传输的节奏。

80.如图3所示为控制流程图,第一步,系统上电并完成初始化(包括服务器和采集设备);第二步,服务器发起第一个触发节拍;第三步,采集设备按照初始化参数响应触发节拍,开始执行当前激活的脚本,内部计数器开始计数;第四步,采集设备频点、参考电平等参数设置完毕,进入稳态,数据链路稳定;第五步,计数器在规定的计数值产生内部触发,开始数据采集并缓存;第六步,计数器在规定的计数值产生软件中断(保证第五步数据采集并缓存可靠执行),上位机响应中断信号,将缓存数据回传并通过网络发送至服务端。上述流程为服务器发起一次采集事件。循环执行,则可实现特定脚本条件下的无线信号自动采集。

81.如图4所示为数据流程框图,首先adc的量化数据通过jesd204b接口传送至fpga,fpga内部实现了采用多相技术的低通滤波器、均衡滤波器、功率补偿乘法器、ddc、采样率变换和pcie通道。上位机通过pcie通道传送数据并通过网络发送至服务器端。

82.表格1是操作边界条件列表,是本实用新型的具体实施事实和方法的实施例。

83.表格1 边界条件列表

[0084][0085]

无线信号采集前端电路对射频信号进行变频处理,变频至固定频点307.2mhz;该通带信号通过通带500mhz带通滤波器进行抗混叠处理,馈入adc进行量化;adc采样频率为1.2288ghz;

[0086]

高速adc实现了1.2288ghz的高速采样;使用了高速jesd204b链路与fpga通信,单根lane速率可达12.288gbps,将500mhz带宽量化信号准确传输至fpga。fpga内部采用xilinx提供的jesd204b ip核与adc进行通信,用户接口时钟为307.2mhz,1个时钟具有4个采样点,并行数据传递至后端dsp单元进行进一步处理。采集到的高速并行数据通过多项fir数字滤波器进行滤波,实现较高矩形系数的滤波器,提高过渡带陡峭度,低通滤波后的数据传递至任意响应滤波器,进行宽带带内均衡,补偿系统的幅频响应,降低带内波动,为较高质量的功率测量提供硬件补偿。fpga接收外部节拍信号,在触发时刻将处理完毕的数据缓存至ddr4外部存储空间,缓存数据长度可调,时长参数软件可设,满足后续上位机对iq数据的请求以及后续流控。fpga可产生中断信号,在全局节拍信号的激励下定时进行网络数据传输。上位机根据硬件中断信号请求iq数据并通过pcie缓存至上位机,然后通过网络传输,将连续iq的数据传输至服务端;服务端响应iq数据网络传输请求,并将数据缓存至资源池。服务端产生全局节拍信号,控制数据采集、传输的节奏。

[0087]

本实施例的具体实现方案可以参见上述实施例中的相关说明,此处不再赘述。

[0088]

可以理解的是,上述各实施例中相同或相似部分可以相互参考,在一些实施例中未详细说明的内容可以参见其他实施例中相同或相似的内容。

[0089]

需要说明的是,在本实用新型的描述中,术语“第一”、“第二”等仅用于描述目的,

而不能理解为指示或暗示相对重要性。此外,在本实用新型的描述中,除非另有说明,“多个”的含义是指至少两个。

[0090]

流程图中或在此以其他方式描述的任何过程或方法描述可以被理解为,表示包括一个或更多个用于实现特定逻辑功能或过程的步骤的可执行指令的代码的模块、片段或部分,并且本实用新型的优选实施方式的范围包括另外的实现,其中可以不按所示出或讨论的顺序,包括根据所涉及的功能按基本同时的方式或按相反的顺序,来执行功能,这应被本实用新型的实施例所属技术领域的技术人员所理解。

[0091]

应当理解,本实用新型的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,多个步骤或方法可以用存储在存储器中且由合适的指令执行装置执行的软件或固件来实现。例如,如果用硬件来实现,和在另一实施方式中一样,可用本领域公知的下列技术中的任一项或他们的组合来实现:具有用于对数据信号实现逻辑功能的逻辑门电路的离散逻辑电路,具有合适的组合逻辑门电路的专用集成电路,可编程门阵列(pga),现场可编程门阵列(fpga)等。

[0092]

本技术领域的普通技术人员可以理解实现上述实施例方法携带的全部或部分步骤是可以通过程序来指令相关的硬件完成,相应的程序可以存储于一种计算机可读存储介质中,该程序在执行时,包括方法实施例的步骤之一或其组合。

[0093]

此外,在本实用新型各个实施例中的各功能单元可以集成在一个处理模块中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个模块中。上述集成的模块既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。集成的模块如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读取存储介质中。

[0094]

上述提到的存储介质可以是只读存储器,磁盘或光盘等。

[0095]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本实用新型的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

[0096]

采用了本实用新型的支持实现自动化超宽带无线信号采集传输处理的系统,采用网络架构,采集和测量分离。具体为数据集中缓存、数据采集节点分布式部署,同时保证采集节点设置的灵活性和中央调度的统一性。采用中心服务器产生时序节拍的方法,统一调度采集节点的任务时序,充分利用网络带宽,减少网络传输冲突,提高了无线信号采集效率,适用于产线流水线测试。系统架构较为合理,数据流清晰,采用多项技术,实时处理宽带信号,使用硬件均衡技术,补偿通带内频响,降低带内波动,提高功率及evm测量精确度。

[0097]

在此说明书中,本实用新型已参照其特定的实施例作了描述。但是,很显然仍可以作出各种修改和变换而不背离本实用新型的精神和范围。因此,说明书和附图应被认为是说明性的而非限制性的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1