一种谱型可灵活设计的集成化实时光谱展宽模块的制作方法

1.本发明涉及激光信号光谱展宽领域,尤其涉及一种谱型可灵活设计的相位调制信号的实时生成且集成化的光谱展宽模块。

背景技术:

2.超高功率连续光纤激光器具有高功率、高可靠性、高光束质量和热管理方便等优点,在工业加工、军事攻防等领域具有广泛的应用。在军事领域,作为激光武器的核心部分,高功率光纤激光器具有比固体激光器体积小,能耗低等特点,可解决固定安装问题,拓展应用于机、舰等移动载体。因此,多个国家都在推进激光武器开发,加大高功率连续光纤激光器的研究力度,旨在此领域占得先机。

3.当激光器功率放大过程中泵浦功率过高时,受光纤中多种非线性效应的影响,输出功率曲线进入非线性区。其中,光纤中的受激布里渊散射(stimulated brillouin scattering,sbs)效应阈值最低,容易造成有效输出效率降低,成为限制激光器最高输出功率的瓶颈问题。为提升光纤激光器的输出功率,提出了多种抑制sbs效应的方法,例如,减小光场和声场重叠面积、引入增益竞争、降低数值孔径(na)、使用高掺杂光纤与相位调制展宽种子激光光谱等。

4.其中,基于相位调制的方式对种子源光谱进行展宽,能够降低平均入纤功率,具有操作简单、效率高的特点,成为保证高功率连续光纤激光器系统高功率输出的关键技术之一。现阶段中,种子源相位调制展宽的驱动信号多为白噪声源,通过物理方法产生白噪声模拟信号,通过调节信号的功率或者加滤波器来改变光谱的带宽,光谱的形状是高斯型。白噪声源的缺点是谱型单一,随机性太强,信号的不确定性大。因此,现有技术还有待于改进和发展。

技术实现要素:

5.鉴于上述现有技术的不足,本发明的目的在于提供一种谱型可灵活设计的集成化实时光谱展宽模块,以解决现有相位调制器的驱动信号采用白噪声源,使得谱型单一,随机性太强,信号的不确定性大,无法实现谱型灵活设计和确定性问题。

6.本发明的技术方案如下:

7.一种谱型可灵活设计的集成化实时光谱展宽模块,包括:种子源、相位调制器驱动信号生成模块、射频功放和相位调制器;

8.所述相位调制器驱动信号生成模块由fpga芯片和dac芯片构成,可实现相位调制信号的实时生成,且信号的谱型可以灵活设计;

9.所述fpga芯片包括锁相环单元、数据生成单元、两个并串转换单元;

10.所述锁相环单元接收所述dac芯片的数据时钟输出作为所述锁相环单元的参考时钟输入,生成数据生成时钟和数据同步时钟,并将所述数据生成时钟输入所述数据生成单元,将所述数据同步时钟输入所述dac芯片作为数据时钟输入;

11.所述数据生成单元根据dac芯片的采样率和数据生成时钟并行实时生成多个串行化数据,根据dac芯片双通道的工作模式,将多个串行化数据分为两组,每组内将多个串行化数据拼接为一个数据,将拼接后得到的两个数据分别输入到相应的并串转换单元,经并串转换后输入所述dac芯片作为数据输入;

12.所述dac芯片根据所述数据输入和所述数据时钟输入,将数字信号转化为模拟信号,作为相位调制器的驱动信号。

13.进一步地,所述fpga芯片中的各功能单元均通过verilog hdl硬件语言编程实现。

14.进一步地,所述锁相环单元用于实现fpga芯片中各功能单元间的时序同步。

15.进一步地,所述数据生成单元并行实时生成的串行化数据的个数为:dac芯片的采样率/数据生成时钟,数据位宽由dac芯片决定。

16.进一步地,所述数据生成单元的数据生成方式包括实时运算、预存储并实时控制读取,能够根据需求实现不同的信号生成,从而使得信号的谱型可灵活设计。

17.进一步地,所述数据生成单元中,每组内将多个串行化数据根据并串转换单元的工作原理拼接为一个数据,每个拼接得到的数据其位宽为对应组串行化数据的位宽乘以串行化数据的个数。

18.进一步地,所述dac芯片输出的模拟信号经所述射频功放放大后驱动所述相位调制器。

19.进一步地,所述相位调制器的光输入端与所述种子源连接,用于接收所述种子源输出的保偏窄线宽连续激光信号,并通过高阶外相位调制的方式对所述种子源输出的保偏窄线宽连续激光信号进行展宽。

20.本发明的有益效果是:本发明提出的光谱展宽模块,关键部分为相位调制器驱动信号生成模块,该部分主要由fpga芯片和dac芯片构成,可实现相位调制信号的实时生成,且信号的谱型可以灵活设计。fpga芯片包括锁相环单元、数据生成单元和两个并串转换单元,各功能单元均通过verilog hdl硬件语言编程实现。锁相环单元用于实现fpga芯片中各功能单元间的时序同步。数据生成单元的数据生成方式包括实时运算、预存储并实时控制读取,能够根据需求实现不同的信号生成,从而使得信号的谱型可灵活设计。

附图说明

21.为了更清楚的说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图示出的结构获得其他的附图。

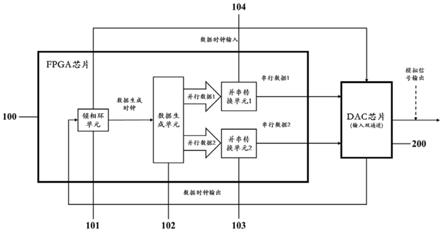

22.图1是本发明中相位调制器驱动信号生成模块的架构示意图。

23.图2是本发明中312.5msps并行数据到1.25gsps串行数据的并串转换原理图。

24.图3是本发明中数据生成单元的原理图1。

25.图4是本发明中数据生成单元的原理图2。

26.附图中各标记:100、fpga芯片;101、锁相环单元;102、数据生成单元;1021、prbs生成单元;1022、比较器单元;1023、调p序列生成单元;1024、地址生成单元;1025、数据存储单元;103、第一并串转换单元;104、第二并串转换单元;200、dac芯片。

具体实施方式

27.本发明提供一种谱型可灵活设计的集成化实时光谱展宽模块,为使本发明的目的、技术方案及效果更加清楚、明确,以下参照附图并举实例对本发明进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

28.在实施方式和申请专利范围中,除非文中对于冠词有特别限定,否则“一”、“一个”、“所述”和“该”也可包括复数形式。若本发明实施例中有涉及“第一”、“第二”等的描述,则该“第一”、“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。

29.应该进一步理解的是,本发明的说明书中使用的措辞“包括”是指存在所述特征、整数、步骤、操作、元件和/或组件,但是并不排除存在或添加一个或多个其他特征、整数、步骤、操作、元件、组件和/或它们的组。应该理解,当我们称元件被“连接”或“耦接”到另一元件时,它可以直接连接或耦接到其他元件,或者也可以存在中间元件。此外,这里使用的“连接”或“耦接”可以包括无线连接或无线耦接。这里使用的措辞“和/或”包括一个或多个相关联的列出项的全部或任一单元和全部组合。

30.本技术领域技术人员可以理解,除非另外定义,这里使用的所有术语(包括技术术语和科学术语),具有与本发明所属领域中的普通技术人员的一般理解相同的意义。还应该理解的是,诸如通用字典中定义的那些术语,应该被理解为具有与现有技术的上下文中的意义一致的意义,并且除非像这里一样被特定定义,否则不会用理想化或过于正式的含义来解释。

31.另外,各实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本发明要求的保护范围之内。

32.本发明提供一种谱型可灵活设计的集成化实时光谱展宽模块,包括:种子源、相位调制器驱动信号生成模块、射频功放和相位调制器;

33.所述种子源用于输出保偏窄线宽连续激光信号;

34.所述相位调制器驱动信号生成模块与所述相位调制器的电输入端连接,用于生成所述相位调制器驱动信号;

35.所述射频功放连接在所述相位调制器与所述相位调制器驱动信号生成模块之间,用于对所述相位调制器驱动信号生成模块输出的驱动信号进行功率放大后输出至所述相位调制器;

36.所述相位调制器的光输入端与所述种子源连接,用于接收所述种子源输出的保偏窄线宽连续激光信号,并通过高阶外相位调制的方式对所述种子源输出的保偏窄线宽连续激光信号进行展宽。

37.请同时参阅图1至图4,本发明提供了一种相位调制器驱动信号生成模块的较佳实施例。

38.如图1所示,本实施例提供的一种相位调制器驱动信号生成模块,包括fpga芯片100以及与所述fpga芯片100连接的dac芯片200,所述dac芯片200用于将所述fpga芯片100输出的数字信号转换为模拟信号。

39.所述fpga芯片100包括:锁相环单元101、数据生成单元102、第一并串转换单元103以及第二并串转换单元104。所述锁相环单元101与所述dac芯片200连接,用于接收所述dac芯片200数据时钟输出作为该单元的参考时钟输入,分别产生数据生成时钟给到数据生成单元102和数据同步时钟给到dac芯片200的数据时钟输入,其功能是实现fpga芯片中各功能单元间的时序同步;所述数据生成单元102分别与所述锁相环单元101、所述第一并串转换单元103以及所述第二并串转换单元104连接,用于根据dac芯片的采样率和所述数据生成时钟信号生成数字信号,并分两路分别输送至所述第一并串转换单元103与所述第二并串转换单元104,经并串转换后输入所述dac芯片200作为数据输入;所述dac芯片200分别与所述第一并串转换单元103以及所述第二并串转换单元104连接,用于根据所述数据输入和所述数据时钟输入,将数字信号转换为模拟信号提供给相位调制器作为驱动信号。

40.具体地,所述dac芯片200型号是ad9739,ad9739是一款14bit dac芯片,采用cmos工艺技术制造,最高采样率达2.5gsps;ad9739采用双通道双倍数据速率(ddr)数据传输模式,1/4dac采样率的数据时钟,在数据时钟上升沿和下降沿均触发转换,输入数据速率为1/2时钟速率,每个通道数据最高速率1.25gsps;所述fpga芯片100的型号是xc7z020clg484,利用verilog hdl硬件语言实时生成所需信号的数字形式,经dac芯片200模拟输出。

41.所述数据时钟输出为625mhz,所述数据生成时钟为312.5mhz,所述数据时钟输入为625mhz。工作时,所述dac芯片200的采样时钟分频出的625mhz的数据时钟输出作为参考时钟输入给到所述锁相环单元101,并产生一个312.5mhz的数据生成时钟和一个625mhz的数据同步时钟。所述数据生成单元102根据所述数据生成时钟生成数字信号,并分两路分别输送至所述第一并串转换单元103与所述第二并串转换单元104,具体为通过产生的312.5mhz的数据生成时钟信号并行实时生成8个14bits的数据,并将8个数据分成两组,第1、3、5、7个数据为第一组,对应通道1的数据;第2、4、6、8个数据为第二组,对应通道2的数据,每个通道的4个14bit的数据根据并串转换单元的并串转换原理先拼接成56bit的数据,312.5msps并行数据到1.25gsps串行数据的并串转换的原理如图2所示(以2bit的数据为例,14bit的数据可以类推),将2组312.5m的56bit的数据分别作为2个并串转换单元的输入,2个并串转换单元分别输出1.25gsps串行的14bit数据,dac芯片200根据625mhz的数据时钟输入与两组1.25gsps的数据输入以2.5gsps的采样率将数字信号转换为模拟信号,作为相位调制器的驱动信号。

42.需要说明的是,在一些实施例中,双通道的8个数据根据一定的赋值方式可以生成2.5gsps、等效1.25gsps(1和2、3和4、5和6、7和8赋予同一值)、等效625msps(1和2和3和4、5和6和7和8赋予同一值)、等效312.5msps(1和2和3和4和5和6和7和8均赋予同一值)四种速率的数据。

43.在上述技术方案中,本发明通过fpga芯片100以及与所述fpga芯片100连接的dac芯片200构成相位调制器驱动信号生成模块,能够实时生成所需信号,根据所需信号的生成模式选择实时运算或预存储后再实时控制读取,并可以根据不同的需求灵活调整信号,实现了谱型可灵活设计的集成化实时光谱展宽模块。

44.请参阅图3,实施例1为基于prbs生成1.25gsps的调p序列,所述数据生成单元102包括:prbs生成单元1021、比较器单元1022以及调p序列生成单元1023;其中,所述prbs生成单元1021根据所述数据生成时钟生成prbs序列;所述比较器单元1022根据所述prbs序列和

所述数据生成时钟生成操作数序列;所述调p序列生成单元1023根据所述操作数序列和所述数据生成时钟生成调p序列,并将所述调p序列根据所述并串转换原理预先拼接,再给到所述第一并串转换单元103与所述第二并串转换单元104。

45.具体地,调p序列为一串由0和1组成的序列,p为序列中相邻两个数据间的翻转(0到1或者1到0)的概率。调p序列的生成过程为:先生成一组0-1之间的随机数,设置一个0-1之间的阈值p,根据阈值进行量化,大于阈值量化为0,否则阈值量化为1,生成一组操作数序列,操作数为1代表相邻两个数据之间存在翻转,操作数为0代表相邻两个数据之间不翻转,其中翻转的概率等于阈值p。其后选取一个初值为0或者为1,然后在此初值的基础上根据操作数序列生成调p序列。

46.更具体地,基于prbs的调p序列实质上是利用prbs生成随机数。如图3所示,首先选定某一本原多项式来控制prbs的周期,从而控制调p序列的周期,是一种时域上的控制,易于操作。具体为利用4组不同初值的线性移位寄存器,在单个312.5mhz的时钟周期里,每一组线性移位寄存器并行生成对应prbs序列的串行化输出的4位数据,为xout1-xout4,将对应位置的四组数据组成4个4bit的随机数rd_num1-rd_num4,该随机数的范围为0-15,所以0-1之间的阈值p对应的0-15的值为(p*16-1)的四舍五入取整。量化之后得到4个操作数op_num1-op_num4,将前一个数据与当前操作数异或就可以得到当前数据,即得到调p序列。需要说明的是,上述的4个数据的前后是指串行输出的先后顺序,但4个数据是在同一个时钟内并行运算的。将4个数据根据等效1.25gsps采样率的赋值方式进行分组和赋值。

47.请参阅图4,实施例2为2.5gsps的多频信号,所述数据生成单元102包括:地址生成单元1024与数据存储单元1025;其中,所述地址生成单元1024根据所述数据生成时钟生成数据地址;所述数据存储单元1025用于预先存储多频信号,并根据地址输出数据。

48.具体地,所述地址生成单元1024并行生成8组数据地址,分别用于8组预先存储了多频信号的数据存储单元1025的数据读取控制。其中,多频信号离线在频域上设计出所需的信号,再通过傅里叶逆变换得出时域信号,通过先存储在数据存储单元1025(rom)中,再通过实时控制从数据存储单元1025中读取信号,是一种频域上的控制。在实施例2中,多频信号存储在8个rom的规则为:第n个rom中存储的数据是第(8k+n)个数据,k=0,1,2,3

……

。

49.可见,本发明通过fpga芯片100与dac芯片200构成相位调制器驱动信号生成模块,能够实时生成所需信号,因fpga芯片100具备可编程能力,根据所需信号的生成模式选择实时运算或预存储再实时控制读取,并可以根据不同的需求灵活调整信号,实现了谱型可灵活设计的集成化实时光谱展宽模块。

50.应当理解的是,本发明的应用不限于上述的举例,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,所有这些改进和变换都应属于本发明所附权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1