时钟数据恢复电路以及串行接收机的制作方法

1.本发明涉及电路技术领域,特别涉及一种时钟数据恢复电路以及串行接收机。

背景技术:

2.串行通信芯片是高速有线数据通信中必不可少的模块,实现了在端口数量少的情况下进行高速率的数据传输。目前,56gb/s速率以上的超高速有线串行接收机一般采用pam4(4pulse amplitude modulation,第四代脉冲幅度调制)调制方式,引入adc(analog-to-digital converter,模拟数字转换器)对于模拟前端信号进行量化。均衡方式采用前馈均衡(feed-forward equalization,ffe)与判决反馈均衡(decision-feedback equalization,dfe)相结合的方式,通过前馈均衡技术实现更好的高阶均衡,提高了在pam4调制方式下整个系统的误码率。

3.目前,基于adc的超高速串行接收机结构中,时钟数据恢复电路(clock data recovery circuit,cdr)一般基于鉴相器来提取接收时钟与采集数据之间的相位误差,鉴相器的数据输入来源于均衡器的输出数据。在这种情况下,cdr环路需要经过如下阶段:首先,在模拟电路层面,cdr环路控制下的采样时钟对于模拟前端均衡信号进行采样,adc对于数据进行量化;之后,adc的量化数据将传递至数字域中,时间交织adc的校准算法将对量化数据进行adc通道内和通道间的误差进行校准,校准后的数据将传递至ffe/dfe均衡器中,均衡器中的滤波单元将生成数据传递至鉴相器中,鉴相器的输出结果经过抽取、积分等操作后得到待调整的采样时刻相位,并反馈至相位插值器中,更新adc的采样时钟相位。经过上述操作,实现了一次cdr环路的相位迭代。

4.在传统基于slicer(双向限幅器)的接收机中,没有数字域ffe/dfe均衡,接收到模拟dfe均衡后信号的slicer将其判决结果直接传递至cdr的鉴相器,整个cdr环路也基于模拟电路实现,环路速度快,仅需要20-30个单位码元时间(ui)即可完成。

5.然而,在目前基于adc的接收机中,cdr环路延迟长,且在超高速串行接口中,由于数字域工作频率与模拟域工作频率之间有较大差距,因此在数字域均衡系数迭代、cdr相位迭代中会引入抽取的方案,导致基于adc的接收机中cdr环路响应速度慢、难以追踪高频频偏等问题,降低了接收机系统的稳定性。同时,在串行接口的实际应用中,在有数据待传输和无数据待传输的情况下,会对串行接口的工作状态加以控制,由于cdr建立速度慢带来的无效输出传输将降低系统功耗。

技术实现要素:

6.本发明要解决的技术问题是为了克服现有基于adc的串行接收机中cdr环路延迟长、响应速度慢的缺陷,提供一种时钟数据恢复电路以及串行接收机。

7.本发明是通过下述技术方案来解决上述技术问题:

8.本发明的第一方面提供一种时钟数据恢复电路,包括第一时钟数据恢复单元、第二时钟数据恢复单元以及相位插值器:

9.所述第一时钟数据恢复单元用于采集adc的高位量化数据,并对所述高位量化数据进行处理,得到待调整的第一采样时刻相位;其中,所述第一时钟数据恢复单元中的第一鉴相器以时钟和数据的相位同步时信道的冲激响应函数的采样值h(0)=h(1)的特性作为鉴相标准;

10.所述第二时钟数据恢复单元用于采集所述adc经过数字校准和均衡处理的数据,并对所述数据进行处理,得到待调整的第二采样时刻相位;其中,所述第二时钟数据恢复单元中的第二鉴相器以时钟和数据的相位同步时信道的冲激响应函数的采样值h(-1)=h(1)的特性作为鉴相标准;

11.所述相位插值器用于根据所述第一采样时刻相位的波动幅度和所述第二采样时刻相位的波动幅度更新所述adc的采样时钟相位。

12.可选地,所述相位插值器具体用于在所述第一采样时刻相位的波动幅度大于预设阈值或者所述第二采样时刻相位的波动幅度大于所述预设阈值的情况下,根据所述第一采样时刻相位更新所述adc的采样时钟相位;以及

13.在所述第一采样时刻相位的波动幅度和所述第二采样时刻相位的波动幅度均小于等于预设阈值情况下,根据所述第二采样时刻相位更新所述adc的采样时钟相位。

14.可选地,所述第一时钟数据恢复单元还包括第一表决器、第一相位积分器、第一编码器,所述第一鉴相器、所述第一表决器、所述第一相位积分器、所述第一编码器、所述相位插值器依次连接;

15.所述第二时钟数据恢复单元还包括第二表决器、第二相位积分器、频率积分器、第二编码器,所述第二鉴相器的输出端与所述第二表决器的输入端连接,所述第二表决器的输出端分别与所述第二相位积分器的输入端以及所述频率积分器的输入端连接,所述第二相位积分器的输出端和所述频率积分器的输出端均与所述第二编码器的输入端连接,第二编码器的输出端与所述相位插值器连接。

16.可选地,所述第一编码器用于去除所述第一采样时刻相位中的直流信息。

17.可选地,所述第一编码器用于将所述第一采样时刻相位的格式转换为所述相位插值器可识别的格式。

18.可选地,所述第二编码器用于将所述第二采样时刻相位的格式转换为所述相位插值器可识别的格式。

19.可选地,所述第一时钟数据恢复单元具体用于采集所述adc经过串并转换后的高位量化数据。

20.可选地,所述高位量化数据的位数为至少两位。

21.本发明的第二方面还提供一种串行接收机,包括如第一方面所述的时钟数据恢复电路。

22.可选地,所述串行接收机还包括依次连接的模拟前端、串并转换单元、数字校准单元和均衡器;所述模拟前端包括adc。

23.本发明的积极进步效果在于:第一鉴相器与第二鉴相器采用不同的鉴相标准,以实现第一时钟恢复单元的收敛相位与第二时钟恢复单元的收敛相位更为接近。第一时钟数据恢复单元通过采集adc的高位量化数据可以快速锁定第一采样时刻相位,从而可以降低时钟数据恢复电路的环路延迟。第二时钟数据恢复单元通过采集adc经过数字校准和均衡

处理的完整数据,以及长时间的统计平均锁定第二采样时刻相位,从而可以保证时钟数据恢复电路的稳定性。

24.相位插值器根据第一采样时刻相位和第二采样时刻相位的波动幅度更新adc的采样时钟相位,融合了第一时钟数据恢复单元的迭代结果和第二时钟数据恢复单元的迭代结果,不仅降低了时钟数据恢复电路的环路延迟,同时保证了时钟数据恢复电路的稳定性,进而提高了串行接收机的稳定性和收发系统的工作能效。

附图说明

25.图1为本发明实施例1提供的一种时钟数据恢复电路的结构框图。

26.图2为本发明实施例1提供的一种冲激响应曲线图。

27.图3为本发明实施例1提供的另一种冲激响应曲线图。

28.图4为本发明实施例1提供的一种时钟数据恢复电路的内部结构示意图。

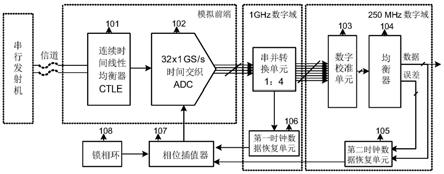

29.图5为本发明实施例2提供的一种串行接收机的结构示意图。

具体实施方式

30.下面通过实施例的方式进一步说明本发明,但并不因此将本发明限制在所述的实施例范围之中。

31.实施例1

32.本实施例提供一种时钟数据恢复电路,如图1所示,包括第一时钟数据恢复单元、第二时钟数据恢复单元以及相位插值器。

33.所述第一时钟数据恢复单元用于采集adc的高位量化数据,并对所述高位量化数据进行处理,得到待调整的第一采样时刻相位。其中,所述第一时钟数据恢复单元中的第一鉴相器以时钟和数据的相位同步时信道的冲激响应函数的采样值h(0)=h(1)的特性作为鉴相标准。

34.在具体实施中,上述第一时钟数据恢复单元可以直接采集adc输出的高位量化数据,也可以采集adc经过串并转换后的高位量化数据。其中,串并转换是指将1路串行数据转换为n路并行数据,n可以根据串行接收机中模拟前端的工作频率和数字域的工作频率确定。在一个具体的例子中,串行接收机中模拟前端的工作频率为1gh,数字域的工作频率为250mhz,n=1ghz/250mhz=4。

35.在可选的一种实施方式中,上述高位量化数据的位数为至少两位。在一个具体的例子中,上述adc为时间交织adc,考虑到其中子adc的结构一般为逐次逼近型adc,因此,在高2位量化结束后采集adc的输出数据。

36.所述第二时钟数据恢复单元用于采集所述adc经过数字校准和均衡处理的数据,并对所述数据进行处理,得到待调整的第二采样时刻相位。其中,所述第二时钟数据恢复单元中的第二鉴相器使用的是mueller-m

ü

ller算法,以时钟和数据的相位同步时信道的冲激响应函数的采样值h(-1)=h(1)的特性作为鉴相标准。在一些例子中,第二鉴相器也可以称为基于mm判决的鉴相器。

37.在具体实施中,上述数字校准处理具体为对adc通道内和通道间的误差进行校准,可以利用数字校准单元实现。上述均衡处理可以利用均衡器实现,例如ffe/dfe均衡器。

38.所述相位插值器用于根据所述第一采样时刻相位的波动幅度和所述第二采样时刻相位的波动幅度更新所述adc的采样时钟相位。

39.本实施方式中,第一鉴相器与第二鉴相器采用了不同的鉴相标准,也即采用了不同的判据,期望在第一鉴相器处理未均衡数据的情况下得到与第二鉴相器收敛的相位尽可能相近,从而降低第二时钟数据恢复单元高精度收敛的时间。在如图2所示的冲激响应曲线301中,收敛到主项302对应的相位位置。由于经过均衡处理的影响,相比于没有经过均衡处理利用第一鉴相器收敛到的相位,利用第二鉴相器收敛到的相位更为提前。因此,为了实现第一时钟恢复单元的收敛相位与第二时钟恢复单元的收敛相位更为接近,在如图3所示的冲激响应曲线中,将采样值h(0)=h(1)作为第一鉴相器的判据,也即令收敛到的相位满足主项305的大小与后一项306的大小一致;以及在如图2所示的冲激响应曲线301中,将采样值h(-1)=h(1)作为第二鉴相器的判据,也即令收敛到的相位满足主项302的前一项303的大小与后一项304的大小一致。

40.本实施方式提供的时钟数据恢复电路包括两个时钟数据恢复单元,其中,第一时钟数据恢复单元通过采集adc的高位量化数据可以快速锁定第一采样时刻相位,从而可以降低时钟数据恢复电路的环路延迟,因此第一时钟数据恢复单元也可以称为快速时钟数据恢复单元。第二时钟数据恢复单元通过采集adc经过数字校准和均衡处理的完整数据,以及长时间的统计平均锁定第二采样时刻相位,从而可以保证时钟数据恢复电路的稳定性,因此第二时钟数据恢复单元也可以称为慢速时钟数据恢复单元。

41.本实施方式中,相位插值器根据第一采样时刻相位和第二采样时刻相位的波动幅度更新adc的采样时钟相位,融合了快速时钟数据恢复单元的迭代结果和慢速时钟数据恢复单元的迭代结果,不仅降低了时钟数据恢复电路的环路延迟,同时保证了时钟数据恢复电路的稳定性。

42.在可选的一种实施方式中,如图4所示,所述第一时钟数据恢复单元还包括第一表决器202、第一相位积分器203、第一编码器204,第一鉴相器201、第一表决器202、第一相位积分器203、第一编码器204、相位插值器107依次连接,实现时钟数据相位误差的提取、积分和反馈。在具体实施中,第一表决器用于对第一鉴相器的输出结果进行表决,第一相位积分器用于对第一表决器的输出结果进行相位积分,第一编码器用于对第一相位积分器的输出结果进行编码,输出待调整的第一采样时刻相位。

43.所述第二时钟数据恢复单元还包括第二表决器206、第二相位积分器208、频率积分器207、第二编码器209,第二鉴相器205的输出端与第二表决器206的输入端连接,第二表决器206的输出端分别与第二相位积分器208的输入端以及频率积分器207的输入端连接,第二相位积分器208的输出端和频率积分器207的输出端均与第二编码器209的输入端连接,第二编码器209的输出端与相位插值器107连接,实现时钟数据相位误差和频率误差的提取、积分和反馈。在具体实施中,第二表决器用于对第二鉴相器的输出结果进行表决,第一相位积分器用于对第二表决器的输出结果进行相位积分,频率积分器用于对第二表决器的输出结果进行频率积分,第二编码器用于对第二相位积分器的输出结果和频率积分器的输出结果进行编码,输出待调整的第二采样时刻相位。

44.在具体实施中,可以在相位插值器的前端设置选通单元,也可以在现有相位插值器的基础上,在相位插值器的内部增加选通单元,如图4所示。选通单元用于根据所述第一

采样时刻相位的波动幅度和所述第二采样时刻相位的波动幅度选通第一采样时刻相位或者选通第二采样时刻相位。相位插值器根据选通的第一采样时刻相位或者第二采样时刻相位更新adc的采样时钟相位。

45.需要说明的是,由于第一鉴相器仅采集adc的高位量化数据,因此第一表决器的数据处理量远少于第二表决器的数据处理量。

46.在可选的一种实施方式中,上述相位插值器具体用于在所述第一采样时刻相位的波动幅度大于预设阈值或者所述第二采样时刻相位的波动幅度大于所述预设阈值的情况下,根据所述第一采样时刻相位更新所述adc的采样时钟相位;以及在所述第一采样时刻相位的波动幅度和所述第二采样时刻相位的波动幅度均小于等于预设阈值情况下,根据所述第二采样时刻相位更新所述adc的采样时钟相位。

47.在具体实施中,上述预设阈值可以根据实际情况进行设置,例如可以设置为10个lsb(least significant bit,最低有效位),若第一采样时刻相位的波动幅度即第一编码器的相邻编码结果大于10,或者第二采样时刻相位的波动幅度即第二编码器的相邻编码结果大于10,则根据第一编码器的编码结果即第一采样时刻相位更新adc的采样时钟相位。若第一编码器的相邻编码结果和第二编码器的相邻编码结果均小于等于10,则根据第二编码器的编码结果即第二采样时刻相位更新adc的采样时钟相位。

48.在可选的一种实施方式中,所述第一编码器用于去除所述第一采样时刻相位中的直流信息,仅保留可跟随高频频偏的交流信息,避免adc中直流偏差对时钟数据相位误差信息的积分结果造成影响。

49.在可选的一种实施方式中,所述第一编码器用于将所述第一采样时刻相位的格式转换为所述相位插值器可识别的格式。所述第二编码器用于将所述第二采样时刻相位的格式转换为所述相位插值器可识别的格式。本实施方式中,由第一编码器和第二编码器执行格式转换。

50.在可选的另一种实施方式中,所述相位插值器用于将第一编码器输出的第一采样时刻相位的格式转换为可识别的格式,以及将第二编码器输出的第二采样时刻相位的格式转换为可识别的格式。本实施方式中,由相位插值器执行格式转换。

51.需要说明的是,在其它实施方式中,还可以在相位插值器与第一编码器或第二编码器之间设置格式转换单元,将第一采样时刻相位和第二采样时刻相位的格式转换为相位插值器可识别的格式。

52.实施例2

53.本实施例提供一种串行接收机,包括实施例1所述的时钟数据恢复电路。

54.在可选的一种实施方式中,上述串行接收机还包括依次连接的模拟前端、串并转换单元、数字校准单元和均衡器。所述模拟前端包括adc,用于通过信道接收串行发射机发射的模拟信号,并对其进行采样。

55.在具体实施中,如图5所示,上述模拟前端还包括ctle(continuous time linear equalization,连续时间线性均衡器)101,adc可以为时间交织adc102,由32个1gs/s的子通道adc时间交织而成,输出数据通过串并转换单元的1:4串并转换后进入数字域,并在数字校准单元103中以250mhz的速率完成,第二时钟数据恢复单元105采集均衡器104输出的数据和误差,以250mhz的速率完成对数据的处理。其中,均衡器104可以为ffe/dfe均衡器。

56.为了实现更低的环路延迟,第一时钟数据恢复单元106直接采集adc的高位量化数据,以1ghz的速率对于各个子通道adc的量化数据进行并行处理以及快速投票操作。相位插值器107接收第一时钟数据恢复单元输出的第一采样时刻相位、第二时钟数据恢复单元输出的第二采样时刻相位以及来自锁相环108生成的时钟信号,以1ghz的速率更新时间交织adc的采样时钟相位。

57.本实施例中,相位插值器根据第一采样时刻相位和第二采样时刻相位的波动幅度更新adc的采样时钟相位,融合了第一时钟数据恢复单元的迭代结果和第二时钟数据恢复单元的迭代结果,不仅降低了时钟数据恢复电路的环路延迟,同时保证了时钟数据恢复电路的稳定性,进而提高了串行接收机的稳定性和收发系统的工作能效。

58.虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这仅是举例说明,本发明的保护范围是由所附权利要求书限定的。本领域的技术人员在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,但这些变更和修改均落入本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1