多维网络接口的制作方法

多维网络接口

1.相关申请

2.本技术要求于2021年4月21日提交的名称为“methods for low latency connection of components to a network in a 3d-ic”的专利申请号us 63/177595的优先权和权益,并且据此全文以引用方式并入。

背景技术:

3.本节旨在提供与理解本文所述的各种技术相关的信息。如本节的标题所暗示的,这是对相关技术的讨论,绝不应当暗示其是现有技术。一般来讲,相关技术可被认为是或可不被认为是现有技术。因此,应当理解,本节中的任何陈述均应按此意义来理解,并且不作为对现有技术的任何认可。

4.在一些现代电路设计中,对形成数字逻辑、存储器和通信接口的附加电路面积的需求超过了工艺技术中密度改进的速率。这导致芯片面积的增长并限制了2d中的系统设计。作为缓解措施,芯片生产技术能够实现紧密集成的三维(3d)系统设计。一些已知技术已尝试通过在接口处放置异步域交叉来在不同管芯之间划分电路块,以便在3d系统设计中保持任何时序路径完全限制于每个管芯,从而以异步接口的附加延时为代价来保证稳健的时序。3d系统设计的一些示范已尝试利用3d集成电路(3dic)中的同步时钟树,从而实现多个3d层之间的功能块的u架构分割。然而,在3d系统的不同管芯之间延伸的路径的时序受到3d层之间的全局工艺偏斜的差异的影响,这使得该方法在批量生产中容易出现低产量。因此,需要在考虑到3d层之间的全局工艺变化的情况下减少业务延时同时确保稳健的时序收敛的改进电路设计。

附图说明

5.本文参考附图描述了各种架构和电路设计方案和技术的具体实施。然而,应当理解,附图仅示出了本文所述的各种具体实施,并且不旨在限制本文所述的各种技术的实施方案。

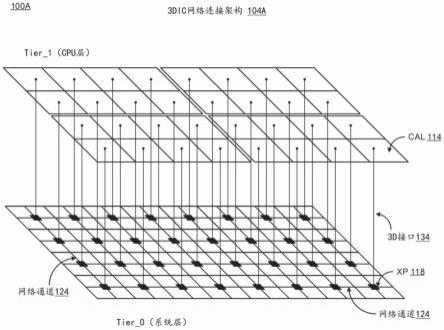

6.图1a至图1b示出了根据本文所述的各种具体实施的多维网络连接架构的各个图。

7.图2示出了根据本文所述的各种具体实施的多维接口时钟架构的图。

8.图3示出了根据本文所述的具体实施的用于提供多维网络连接架构的方法的图。

9.图4示出了根据本文所述的具体实施的用于提供多维网络连接架构的方法的图。

具体实施方式

10.本文所述的各种具体实施涉及提供用于参考3d物理电路设计来支持三维(3d)互连电路相关应用的多维网络连接方案和技术的集成电路。多维网络连接架构可提供以针对各种3d联网应用配置的多层结构来实现的3d互连电路。本文所述的各种具体实施提供了一种通过以3d堆叠管芯之间的低延时连接系统部件来划分系统部件的方法。本文所述的各种方案和技术解决了与互连的可用性相关联的限制,这些限制是由于在可采用不同工艺技术

制造堆叠管芯的约束下在3d边界处引入的面积约束与延时,并且因为每个堆叠管芯可独立地参数偏斜。

11.本文所述的各种具体实施提供了一种通过3d接口在通信网络与各个部件之间实现低延时连接的方法,由此接口信号的时钟相位根据设计的一部分所支持的延时敏感通信的方向而被不同地对待,方向诸如从部件到网络的发射(tx)或从网络到部件的接收(rx)。在一些情况下,设计的tx部分或rx部分内的信号分别在相反方向上传递或在发射(tx)与接收(rx)之间交叉。此类路径被视为非延时敏感的,并且可被定义为满足同步时序的多周期路径,同步时序应在3d层之间的工艺偏斜的所有不同条件下得到满足。另选地,可对这些路径执行重新同步。此外,可定义寄存器传输逻辑(rtl)设计的准则以便有利于将集成电路划分为3d层,大多数时序路径可满足此条件。此外,在一些情况下,网络部件不包含所有输入和输出上的触发器以最小化延时。在这种情况下,触发器的位置对于所有部件应是一致的并且遵循将触发器定位在部件的输入或输出处的惯例,以在任何可能的地方将时序路径保持在单个层内,从而最小化延迟发散的影响。另外,在一些情况下,一种改善此类不满足rtl准则的路径的时序收敛的方法将逻辑门重新分配在3d边界上,从而将一个功能部件分离在两个3d层上,代价是增加了所需的3d接口数量。本文所述的方法涉及保持3d堆叠管芯之间的电路的受限子集同步并且采用相同的电源电压供应。

12.本文将参考图1a至图1b和图2至图4来描述多维网络连接架构的各种具体实施。

13.图1a至图1b示出了根据本文所述的具体实施的多维网络连接架构的各个图。具体地,图1a示出了具有一种多层结构的多维网络连接架构104a的图100a,并且图1b示出了具有另一种多层结构的多维网络连接架构104b的图100b。

14.在各种具体实施中,多维网络连接架构可用各种集成电路(ic)部件来实现,这些部件被布置并耦合在一起作为提供物理电路设计和相关结构的部件的组装或一些组合。在一些情况下,一种设计、提供、制造和/或生产多维网络连接架构的方法可涉及使用本文所述的ic电路部件,以便实现与其相关联的各种相关制造方案和技术。此外,多维网络连接架构可与各种计算电路和/或多个芯片上的部件集成,并且此外,多维网络连接架构也可在用于汽车、手机、服务器以及物联网(iot)的各种嵌入式应用中实现。

15.图1a示出了具有多层结构的多维网络连接架构104a的图100a,其中类似的部件和/或电路连同特征、特性和/或行为在范围上类似于图1b所示的多维网络连接架构104b。一般来讲,图1b所示的布置在网络内重复多次。

16.如图1a所示,多维(3d)网络连接架构104a可指一种设备,该设备具有集成电路以及多层结构和包括以堆叠构型垂直布置的第一层(tier_0)和第二层(tier_1)的多个层。第一层(tier_0)可指系统层并且具有第一功能部件,诸如例如以其间设置有网络通道124的网格图案布置的多个网络路由器(xp)118。第二层(tier_1)可指cpu层并且具有第二功能部件,诸如例如以其间设置有3d网络接口134的网格图案布置的一个或多个网络复用器(cal)114。如前所述,一个或多个网络复用器(cal)114中的每个网络复用器被配置为将多个网络端口集中到单个网络端口。在3d网络连接中使用复用器(cal)可用于限制所需的3d信号连接的数量并因此限制实施3d接口所需的面积。此外,该设备可通过在网络交叉点之间运行的网络通道124在第一层(tier_0)中包括通信网络。在各种具体实施中,经由3d接口134的同步信令可被配置为满足与包括不同工艺技术节点(或世代)的多个层(tier_0,tier_1)相

关联的不同全局工艺偏斜(或拐角)的不同条件下的时序约束。

17.在一些具体实施中,网络通道124在网络交叉点之间运行,诸如例如在两个交叉点之间运行。在一些情况下,可沿网络通道将交叉点插入以提供3d连接点。取决于用途,3d接口134可沿一个或多个网络通道124放置,在这种情况下,可能只有两个网络通道124连接到xp/cal 118、114,或者在与网络通道124的完全交叉xp 118处在四个方向上连接到相邻的xp 118。

18.如图1b所示,多维(3d)网络连接架构104b可指一种设备,该设备具有集成电路以及多层结构和包括以堆叠构型垂直布置的第一层(tier_0)和第二层(tier_1)的多个层。第一层(tier_0)可具有第一功能部件,并且第二层(tier_1)可具有第二功能部件。在一些具体实施中,第一功能部件可包括网络路由器,诸如例如xp 118,并且此外,第二功能部件还可包括被配置为将多个网络端口集中到单个网络端口的网络复用器,诸如例如cal 114。此外,该设备可通过网络通道124和路由器内的网络端口在第一层(tier_0)中包括2d通信网络,该2d通信网络允许经由3d接口134在第一层(tier_0)中的第一功能部件118与第二层(tier_1)中的第二功能部件114之间进行同步信令,用于减少包括第一层(tier_0)和第二层(tier_1)的多个层之间的延时。在一些具体实施中,经由3d接口134的同步信令可被配置为满足与包括不同工艺技术节点(或世代)的第一层(tier_0)和第二层(tier_1)相关联的不同全局工艺偏斜(或拐角)的不同条件下的时序约束。

19.在一些具体实施中,3d接口134提供第二层(tier_1)中的网络复用器114与第一层(tier_0)中的网络路由器118之间的同步信令。3d接口信号可包括微片(flit)信号和相关联的信用(credit)信号,由此微片信号在第一方向上从第一层(tier_0)传递到第二层(tier_1),并且3d接口信号可包括微片信号和相关联的信用信号,由此微片信号在第二方向上从第二层(tier_1)传递到第一层(tier_0)。在每种情况下,在与它们与3d接口信号相关联的微片信号相反的方向上传递的信用信号可包括在从第一层(tier_0)到第二层(tier_1)的第一方向上传递的转发的公共时钟早信号(cce)和公共时钟晚信号(ccl)。此外,第一层(tier_0)中的网络路由器118可接收用于生成公共时钟早信号(cce)和公共时钟晚信号(ccl)的公共时钟信号(cmn_clk)。在一些情况下,cmn_clk可被转发到cal,并且cce和ccl可由cal生成。一般来讲,微片是指需要快速移动的数据有效载荷单元,并且此外,信用是指指示下游网络部件能够接收(没有溢出)的微片数量的电子令牌。此外,信用的使用可以不需要使每个传输握手。

20.在各种具体实施中,通信网络可指三维(3d)接口,由此根据通信方向针对对延时敏感的3d接口信号134不同地调整用于发射或捕获网络通道信号(例如微片)的时钟相位。此外,通过将额外的寄存器或同步器插入,可将时钟相位调整成增大可用于延时敏感路径的时序窗口并补偿具有设计变化的非延时敏感路径。此外,通过包括基于来自工艺变化表126、138和3d连接延迟传感器中(诸如例如硅穿孔(tsv)延迟传感器128)的至少一者的各种输入(例如var_trim、tsv_trim)进行调谐(或修整)的可调谐(或可修整)时序延迟电路,可对时钟相位进行调整。

21.在一些具体实施中,网络通道可指下层(tier_0)上的各个xp 118之间的连接,并且网络通道还可用于传送转发到位于上层或第二层(tier_1)中的第二功能部件114的微片。在各种情况下,这些微片中的许多微片是延时关键的,其中网络通道是指连接交叉点的

通道。在一些情况下,在网络通道上携带的微片基于其地址信息被路由,并且如果地址对应于通过3d接口附接的设备,则微片将以该方式被路由。

22.在一些具体实施中,网络连接架构104a可包括设置在第二层(tier_1)中的一个或多个处理核心130,并且此外,核心130还可与网络异步操作并且通过使用一个或多个同步器(sync)被重新同步成与网络复用器114通信。在一些情况下,核心130被配置为通过网络复用器114和3d接口134与设置在第一层(tier_0)中的网络路由器118异步通信。

23.如本文所述和图1a所示,多维(3d)网络连接架构104a可具有多个层,该多个层包括第一层(tier_0)和第二层(tier_1)。在各种其他具体实施中,多维(3d)网络连接架构104a可具有多个层以及一个或多个附加层,并且因此在这种情况下,通信网络提供一个或多个附加层中的附加功能部件之间的附加同步信令,用于减少第一层(tier_0)、第二层(tier_1)和一个或多个附加层(诸如例如第三层,第四层等)之间的延时。

24.图2示出了具有多层结构的多维(3d)接口时钟架构204的图200,其中类似的部件和/或电路连同特征、特性和/或行为在范围上类似于图1a至图1b所示的多维网络连接架构104a、104b。

25.在各种具体实施中,多维接口时钟架构可用各种集成电路(ic)部件来实现,这些部件被布置并耦接在一起作为提供物理电路设计和相关结构的部件的组装或一些组合。在一些情况下,一种设计、提供、制造和/或生产多维接口时钟架构的方法可涉及使用本文所述的ic电路部件,以便实现与其相关联的各种相关制造方案和技术。此外,多维接口时钟架构可与各种计算电路和/或多个芯片上的部件集成,并且此外,多维接口时钟架构也可在用于汽车、手机、服务器以及物联网(iot)的各种嵌入式应用中实现。

26.如图2所示,3d接口时钟架构204可指一种设备,该设备具有3d集成电路(3dic)以及多层结构和包括以堆叠构型垂直布置的第一层(tier_0)和第二层(tier_1)的多个层。第一层(tier_0)可指系统层并且具有第一功能部件,诸如例如多个网络路由器(xp)218。第二层(tier_1)可指cpu层并且具有第二功能部件,诸如例如网络复用器(cal)214。如前所述,一个或多个网络复用器(cal)214中的每个网络复用器被配置为将多个网络端口集中到单个网络端口。此外,该设备可通过允许经由第一层(tier_0)中的第一功能部件218之间的交叉点进行同步信令的网络通道在第一层(tier_0)中包括通信网络。在各种具体实施中,经由3d接口的同步信令可被配置为满足与包括不同工艺技术节点(或世代)的多个层(tier_0,tier_1)相关联的不同全局工艺偏斜(或拐角)的不同条件下的各种时序约束。

27.在一些具体实施中,网络复用器(cal)214可具有应用于进入xp 218的延时关键路径上的寄存器(触发器)的传输时钟树(cal-tx),并且此外,网络复用器(cal)214还可具有应用于来自xp 218的延时关键路径上的寄存器(触发器)的接收时钟树(cal-rx)。其中发射时钟和捕获时钟为cal-tx和calr-rx或cal-rx和cal-tx的时序路径可包括附加同步器(sync1,sync2),或在设计中被修改为多周期路径,以便能够实现稳健的时序收敛。此类时序路径被视为非延时关键的。从cal-rx发射并在xp中捕获的时序路径以及从xp发射并使用cal-tx捕获的时序路径可包括附加同步器或被修改为多周期路径。此类时序路径也视为延时关键的。在各种情况下,网络复用器(cal)214的cal-tx和cal-rx部分可被配置为经由一个或多个同步器桥210与第二层中的其他功能部件进行双向异步通信。在一些情况下,术语早/晚针对相对于xp 218中时钟的参考相位的时钟相位使用,其中时钟相位可在xp侧生成

并且考虑3d接口的附加相移以在它们到达cal 214时使它们正确。实现最终相位校正的电路位于cal 214中的另选方案是可能的。cal-tx可从网络路由器(xp)218接收公共时钟早信号(cmn_clk_early),并且此外,cal-tx可具有通过组合逻辑的大云(lc)耦合到网络路由器(xp)218的触发器(ff)。此外,cal-rx可从网络路由器(xp)218接收公共时钟晚信号(cmn_clk_late),并且此外,cal-rx可具有通过组合逻辑的小云(sc)耦合到网络路由器(xp)218的触发器(ff)。时序路径位于通过组合逻辑的发射触发器与捕获触发器之间,其中每个触发器涉及多个时序路径的开始/结束点。此外,每个时序路径上的组合逻辑门的数量是指云的大小,由此包括少量组合逻辑门的时序路径是指小云(sc),并且包括与用于信号传播的较长时间相关联的大量门的时序路径被描述为大云(lc)。

28.在一些具体实施中,网络路由器(xp)218可指具有时钟树的路由器块(xp-blk),该时钟树通过一个或多个输入缓冲器(b1,b2)和由可变修整信号(var_trim)和/或可变tsv信号(tsv_trim)控制的一个或多个可变修整缓冲器(vb1,vb2,vb3)接收公共时钟信号(cmn_clk)。此配置可用于在相关电路位于xp侧的情况下生成不同的时钟相位,如图2所示。在一些情况下,系统中的每个xp需要具有时钟缓冲器以确保xp之间的网络通道上的信令。cmn_clk信号可通过输入缓冲器(b1,b2)作为cmn_clk_early信号提供给网络复用器214的cal-tx,并且cmn_clk信号可经历由3d接口和每个层上的相关联横向路由引入的延迟。此外,cmn_clk信号被提供给由可变修整信号(var_trim)控制的第一可变修整缓冲器(vb1)。第一可变修整缓冲器(vb1)将输出信号提供给由可变tsv信号(tsv_trim)控制的第二可变修整缓冲器(vb2),由此vb2和vb3的延迟表示与3d接口上的一次通过相关联的延迟。第二可变修整缓冲器(vb2)将输出信号作为cmn_clk_late信号提供给也由可变tsv信号(tsv_trim)控制的第三可变修整缓冲器(vb3)。第三可变修整缓冲器(vb3)将输出信号提供给cal-rx和xp-blk,并且cal-rx可具有从xp 218中的vb3接收cmn_clk_late信号的可变修整缓冲器(vb4)。此外,cal-tx可通过组合逻辑的大云(lc)和/或组合逻辑的小云将其触发器(ff)耦合到xp-clk。

29.在一些具体实施中,cal-tx可通过触发器(ff)和组合逻辑的大云(lc)向组合逻辑的小云(sc)提供发射信号(代表性tx微片路径)。在一些情况下,代表性tx微片路径从cal_tx上的触发器的q端口开始(其中组合逻辑的大部分位于cal_tx内(显示为lc)并且穿过3d连接去往另一层,在此它进入xp_blk上的较小组合逻辑(sc),继而被xp_blk中的触发器采样。此外,在一些情况下,xp-blk可通过输出触发器(ff)、组合逻辑的大云(lc)和/或组合逻辑的小云(sc)向cal-rx提供接收信号(代表性rx微片路径)。在一些情况下,代表性rx微片路径与tx微片路径相反,并且从xp_blk中的触发器开始,去往lc,然后去往sc,然后被cal_rx中的触发器采样。参考图2,大云(lc)电路和小云(sc)电路是指每个功能块的组合逻辑,因此,lc和sc完全驻留在每个对应功能块的边界内。此外,在各种具体实施中,本文所述的3dic网络连接方案和技术设法将时序路径内的组合逻辑的大部分或几乎全部限制在一个单独的层上,诸如例如第一层(tier_0)。此外,参考cal-tx,时钟发射信号(ctx_clk)可能产生并被提供给大云(lc)处的触发器(ff)以及sync1触发器,并且参考cal-rx,接收时钟信号(crx_clk)可能产生并被提供给小云(sc)处的触发器(ff)以及sync2触发器。此外,参考xp-blk,可将时钟信号提供给大云(lc)和小云(sc)处的触发器(ff)。

30.图3示出了根据本文所述的具体实施的用于提供多维(3d)网络连接架构的方法

300的图。

31.应当理解,即使方法300指示特定的操作执行顺序,但在一些情况下,操作的各个部分也可能以不同的顺序并且在不同的系统上执行。在其他情况下,可向方法300添加附加操作和/或步骤和/或从该方法省略附加操作和/或步骤。另外,方法300可在硬件和/或软件中实现。例如,如果在硬件中实现,则方法300可用如图1a至图1b和图2中所述的部件和/或电路实现。在其他情况下,如果在软件中实现,则方法300可被实现为被配置用于提供如本文所述的多维(3d)网络连接架构的程序或软件指令过程。另外,如果在软件中实现,则与实现方法300相关的指令可存储在存储器和/或数据库中。因此,在各种具体实施中,具有处理器和存储器的计算机或各种其他类型的计算设备可被配置为执行方法300。

32.如参考图3所述,方法300可用于制造和/或生产或者使得制造和/或生产集成电路(ic),该ic在如本文所述的物理设计中实现各种布局方案和技术,从而使用如本文所述的各种相关设备、部件和/或电路来提供多维(3d)网络连接。

33.在框310处,方法300可提供具有多个层的集成电路,该多个层包括以堆叠构型垂直布置的第一层和第二层,其中第一层中的发射序列元件形成组合路径以对应于第二层中的捕获序列元件,并且其中第二层中的发射序列元件对应于第一层中的捕获序列元件。此外,在框320处,方法300可在第一层和第二层中的对应发射序列元件与捕获序列元件之间形成跨越多个层的时序路径。此外,在框330处,方法300可实施确保与时序路径相关联的组合逻辑的大部分与第一层或第二层中的发射序列元件或捕获序列元件共同位于同一层上的寄存器传输逻辑(rtl)策略。

34.在一些具体实施中,第一层中的发射序列元件包括第一层中的一个或多个发射序列部件(例如,锁存器、触发器、存储器等),并且第二层中的捕获序列元件包括第二层中的一个或多个捕获锁存器。另外,时序路径可包括从第一层中的发射锁存器到第二层中的捕获锁存器跨越多个层的第一时序路径。在一些情况下,第二层中的发射序列元件可包括第二层中的一个或多个发射锁存器,并且第一层中的捕获序列元件包括第一层中的一个或多个捕获锁存器。另外,时序路径可包括从第二层中的发射锁存器到第一层中的捕获锁存器跨越多个层的第二时序路径。

35.在一些具体实施中,组合逻辑可包括第一层中的第一组合逻辑,并且组合逻辑可包括第二层中的第二组合逻辑。在一些情况下,方法300可将第一组合逻辑的一部分从第一层移动到第二层,以确保与时序路径相关联的组合逻辑的大部分与第一层或第二层中的发射序列元件或捕获序列元件共同位于同一层上。此外,在一些情况下,方法可将第二组合逻辑的一部分从第二层移动到第一层,以确保与时序路径相关联的组合逻辑的大部分与第一层或第二层中的发射序列元件或捕获序列元件共同位于同一层上。

36.图4示出了根据本文所述的具体实施的用于提供多维(3d)网络连接架构的方法400的图。

37.应当理解,即使方法400指示特定的操作执行顺序,但在一些情况下,操作的各个部分也可能以不同的顺序并且在不同的系统上执行。在其他情况下,可以向方法400添加附加操作和/或步骤和/或从该方法省略附加操作和/或步骤。另外,方法400可在硬件和/或软件中实现。例如,如果在硬件中实现,则方法400可用如图1a至图1b、图2至图3中所述的部件和/或电路实现。在其他情况下,如果在软件中实现,则方法400可被实现为被配置用于提供

如本文所述的多维(3d)网络连接架构的程序或软件指令过程。另外,如果在软件中实现,则与实现方法400相关的指令可存储在存储器和/或数据库中。因此,在各种具体实施中,具有处理器和存储器的计算机或各种其他类型的计算设备可被配置为执行方法400。

38.如参考图4所述,方法400可用于制造和/或生产或者致使制造出和/或生产出集成电路(ic),该ic在如本文所述的物理设计中实现各种布局方案和技术,从而使用如本文所述的各种相关设备、部件和/或电路来提供多维(3d)网络连接架构。

39.在框410处,方法400可提供具有多个层的集成电路,该多个层包括以堆叠构型垂直布置的第一层和第二层,其中第一层可包括第一功能部件,并且其中第二层可包括第二功能部件。此外,在框420处,方法400可通过第一层内的网络通道提供通信网络,该通信网络可允许第一功能部件与第二功能部件之间的同步信令,用于减少包括第一层和第二层的多个层之间的延时。此外,在框430处,方法400可制造或导致制造出具有多个层和通信网络的集成电路。

40.在一些具体实施中,第一功能部件可包括网络路由器,并且此外,第二功能部件还可包括将多个网络端口集中到单个网络端口的网络复用器。此外,在一些情况下,同步信令满足与包括不同工艺技术节点(或世代)的第一层和第二层相关联的不同全局工艺偏斜(或拐角)的不同条件下的时序约束。

41.在一些具体实施中,通信网络可被实现为三维(3d)接口,由此可根据通信方向针对对延时敏感的网络通道不同地调整用于发射或捕获网络通道信号的时钟相位。此外,通过将额外的寄存器或同步器插入,可将时钟相位调整成增大可用于与延时敏感信号相关联的时序路径的时序窗口并补偿具有设计变化的非延时敏感路径。此外,通过包括基于来自工艺变化表和3d连接延迟传感器中的至少一者的输入进行调谐(或修整)的可调谐(或可修整)时序延迟电路,可对时钟相位进行调整。在各种情况下,信号可包括来自第一功能部件的延时敏感发射路径、去往第一功能部件的延时敏感接收路径、来自第一功能部件的非延时敏感发射路径、去往第一功能部件的非延时敏感接收路径以及层级限制本地路径中的至少一者。

42.应当预期的是,权利要求的主题不限于本文提供的各种具体实施和/或图示,而是应该包括根据权利要求的那些具体实施的任一修改形式,包括具体实施的部分和参考不同具体实施的各个元件的组合。还应当理解,在任何此类具体实施的开发中,如在任何工程或设计项目中,应该作出许多具体实施特定的决策以实现开发者的特定目标,诸如例如符合系统相关的约束和/或业务相关的约束,这些约束可能在不同具体实施之间变化。此外,应当理解,此类开发工作可能是复杂且耗时的,但是尽管如此,对于受益于本公开的普通技术人员而言,这仍然是设计、制造和生产的常规任务。

43.本文描述了具有集成电路的设备的各种实施方案,该集成电路具有多个层,该多个层包括以堆叠构型垂直布置的第一层和第二层。该第一层可具有第一功能部件,并且该第二层可具有第二功能部件。该设备还具有位于第一层内的三维(3d)连接,该3d连接允许第一功能部件与第二功能部件之间的同步信令,用于减少包括第一层和第二层的多个层之间的延时。

44.本文描述了方法的各种具体实施。该方法可提供具有多个层的集成电路,该多个层包括以堆叠构型垂直布置的第一层和第二层,其中第一层中的发射序列元件对应于第二

层中的捕获序列元件,并且其中第二层中的发射序列元件对应于第一层中的捕获序列元件。该方法可在第一层和第二层中的对应发射序列元件与捕获序列元件之间形成跨越多个层的时序路径。该方法可实施确保与时序路径相关联的组合逻辑的大部分与第一层或第二层中的发射序列元件或捕获序列元件共同位于同一层上的寄存器传输逻辑(rtl)策略。

45.本文描述了方法的各种具体实施。该方法可提供具有多个层的集成电路,该多个层包括以堆叠构型垂直布置的第一层和第二层。该第一层可具有第一功能部件,并且该第二层可具有第二功能部件。该方法可提供位于第一层内的三维(3d)连接,该3d连接允许第一功能部件与第二功能部件之间的同步信令,用于减少包括第一层和第二层的多个层之间的延时。该方法可生产或导致生产出具有多个层和通信网络的集成电路。

46.已经详细地参考了各种具体实施,其示例在附图和图示中示出。在以下具体描述中,阐述了许多具体细节以提供对本文提供的公开内容的透彻理解。然而,可以在没有这些具体细节的情况下实践本文提供的公开内容。在各种具体实施中,没有详细描述熟知的方法、规程、部件、电路和网络,以便不会不必要地模糊实施方案的细节。

47.还应当理解,虽然各个术语“第一”、“第二”等在本文中可用于描述各种元件,但这些元件不应受这些术语的限制。这些术语仅用于将一个元件与另一个元件区分开。例如,第一元件可被称为第二元件,并且类似地,第二元件可被称为第一元件。此外,第一元件和第二元件分别均为元件,但它们不被认为是相同的元件。

48.在本文提供的本公开的描述中使用的术语是为了描述特定具体实施的目的,并且不旨在限制本文提供的公开内容。如本文中提供的公开内容和所附权利要求的描述中使用的,单数形式“一个”、“一种”和“该”旨在也包括复数形式,除非上下文另有明确指示。如本文所用,术语“和/或”是指并涵盖相关联的列出项目中的一者或多者的任何和所有可能组合。当在本说明书中使用时,术语“包括”、“包含”和/或“含有”指定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或多个其他特征、整数、步骤、操作、元件、部件和/或它们的组的存在或添加。

49.如本文所用,根据上下文,术语“如果”可被解释为意指“当......时”或“在......时”或“响应于确定”或“响应于检测到”。类似地,根据上下文,短语“如果确定......”或“如果检测到[所述条件或事件]”可被解释为意指“在确定......时”或“响应于确定......”或“在检测到[所述条件或事件]时”或“响应于检测到[所述条件或事件]”。术语“上”和“下”;“上部”和“下部”;“向上”和“向下”;“在......下方”和“在......上方”;以及指示给定点或元件上方或下方的相对位置的各种其他类似术语可与本文所述的各种技术的各种具体实施结合使用。

[0050]

虽然前述内容涉及本文所述的各种技术的具体实施,但是可以根据本文的公开内容想出其他和另外的具体实施,本文的公开内容可以由所附权利要求确定。虽然以特定于结构特征和/或方法动作的语言描述了本主题,但应当理解,所附权利要求中限定的主题不一定限于上述特定特征或动作。相反,上述的具体特征和/或动作被公开为实现权利要求的示例性形式。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1